摘要:本节将系统介绍各种半导体存储电路的结构、工作原理和使用方法。首先介绍基本的存储单元,然后介绍由这些存储单元组成的寄存器和随机存储器,包括静态随机存储器和动态随机存储器。最后还将介绍各种只读存储器。

基本概念

存储单元:存储一位数据的电路。可分为静态存储单元和动态存储单元两大类。静态存储单元由门电路连接而成,其中包括各种电路结构形式的锁存器和触发器,只要保持通电,静态存储单元的状态会一直保持下去。动态存储单元则是利用电容的电荷存储效应来存储数据的,由于电容存储的电荷会随着时间的推移逐渐泄露,必须定期地进行“刷新”,才能保证数据不会丢失。

寄存器:存储一组数据的电路,由N个触发器构成。

存储器:存储大量数据的电路。存储器种类虽然很多,但它们的基本结构形式都是由存储矩阵和读/写控制电路两部分组成的。从存储功能上讲,可分为随机存储器(Random Access Memory,简称RAM)和只读存储器(Read Only Memory ,简称ROM)两大类。随机存储器又分成静态随机存储器(SRAM)和动态随机存储器(DRAM)两类。只读存储器有掩模ROM、可编程ROM(PRAM)和可擦除可编程ROM(EPRAM)等几类。

SR锁存器

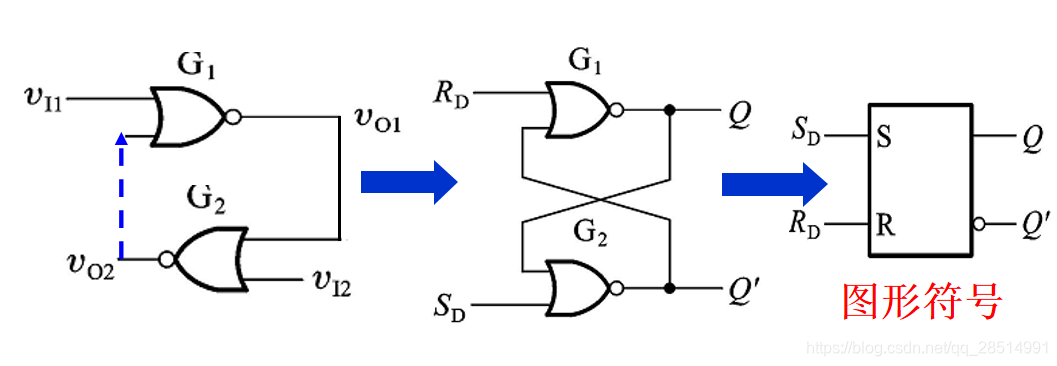

SR锁存器(Set-Reset Latch)是静态存储单元当中最基本、也是电路结构最简单的一种。通常它由两个或非门或者与非门组成。图1给出了两个由或非门组成的SR锁存器电路。

工作原理

- 当

=1,

=0时,

=1,

=0 (定义为1状态)

- 当

=0,

=0时,输出保持

- 当

=0,

=1时,

=0,

=1(定义为0状态)

- 当

=1,

=1时,

=0,

=0。约束条件:

当 =1,

=1, =1时,

=1时, =0,

=0, =0,这既不是定义的1状态,也不是定义的0状态。而且,在

=0,这既不是定义的1状态,也不是定义的0状态。而且,在 和

和 同时回到0以后无法断定锁存器将回到1状态还是0状态。因此,在正常工作时输入信号应遵守

同时回到0以后无法断定锁存器将回到1状态还是0状态。因此,在正常工作时输入信号应遵守的约束条件。

用与非门构成的SR锁存器分析略。

触发器

为协调各部分的工作,常常要求某些电路同时工作。所以需要一个同步信号(触发信号)叫做时钟信号(CLOCK),简称时钟,用CLK表示。触发信号的工作方式可以分为电平触发、边沿触发和脉冲触发三种。

电平触发的触发器

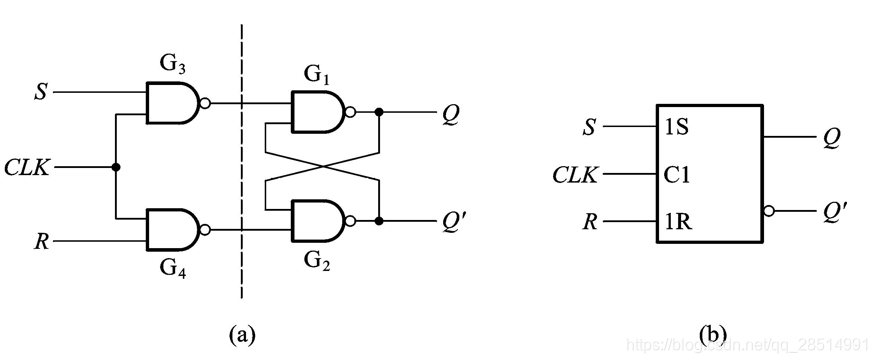

电路结构和逻辑符号

工作原理

当CLK=0,输出保持。当CLK=1,输出随S、R变而变,故称电平触发。

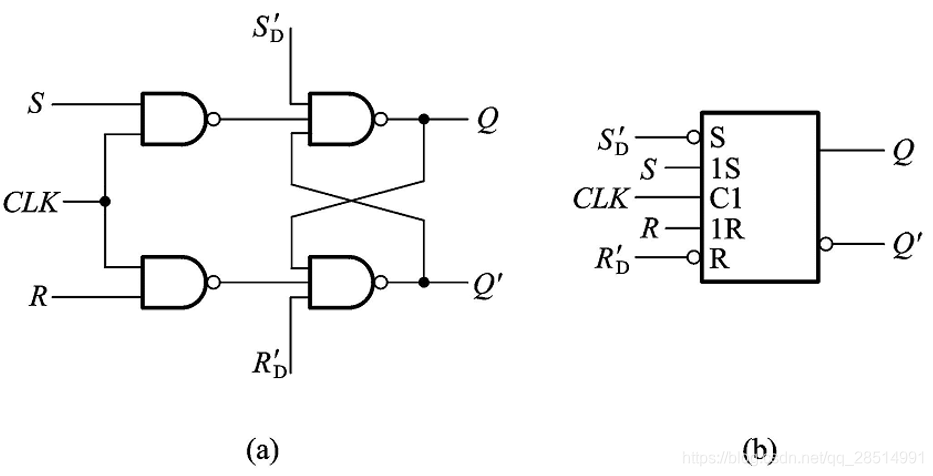

预置功能

在某些应用场合,有时需要在CLK的有效电平到达之前预先将触发器置成指定状态,为此,在实际电路上往往还设置有异步置1输入端 和异步置零输入端

和异步置零输入端 ,如图4所示。

,如图4所示。

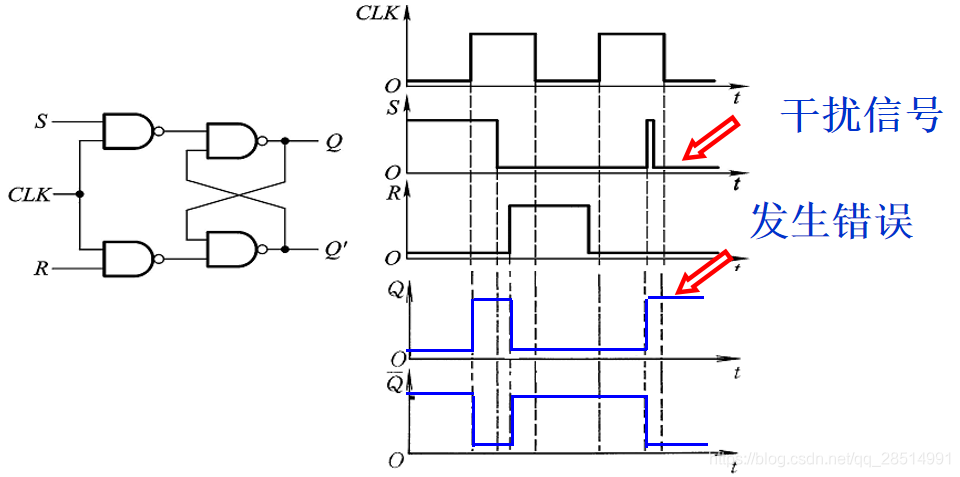

电平触发方式的动作特点

- 当CLK=0,输出保持; 当CLK=1,输出随S、R变而变。

- 在CLK=1的全部时间里,S和R状态的变化都可能引起输出状态的改变。在CLK回到0后,触发器保存的是CLK回到0以前瞬间的状态。

根据上述的动作特点可以想象,如果在CLK=1期间S、R的状态多次发生变化,那么触发器输出的状态也将发生多次翻转,这就降低了触发器的抗干扰能力。

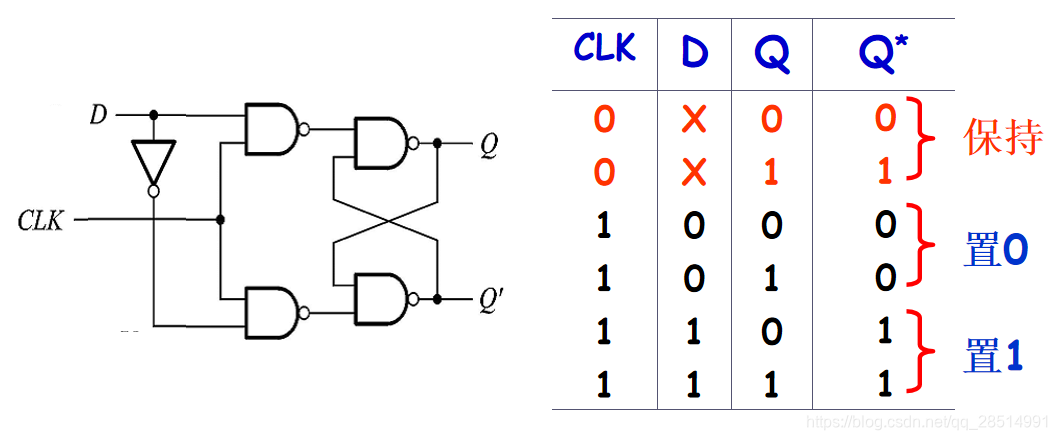

D触发器

为了满足约束条件,以及单端输入信号的需求,在一些集成电路产品中把图2的电路改成了图6的形式,得到了电平触发的D触发器。

边沿触发的触发器

为了提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于CLK信号下降沿(或上升沿)到达时刻输入信号的状态。人们相继研制成了各种边沿触发(edge-triggered)的触发器电路。

目前边沿触发器有利用电平触发的D触发器构成的边沿触发器、维持阻塞触发器和利用门电路传输延迟时间的边沿触发器几种。

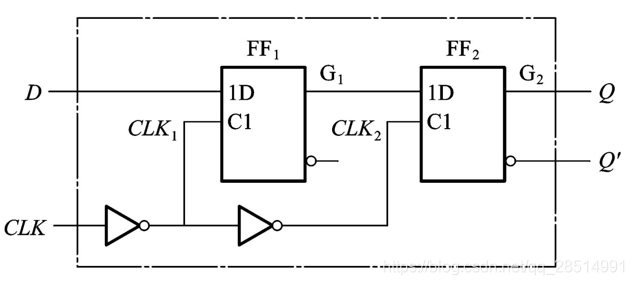

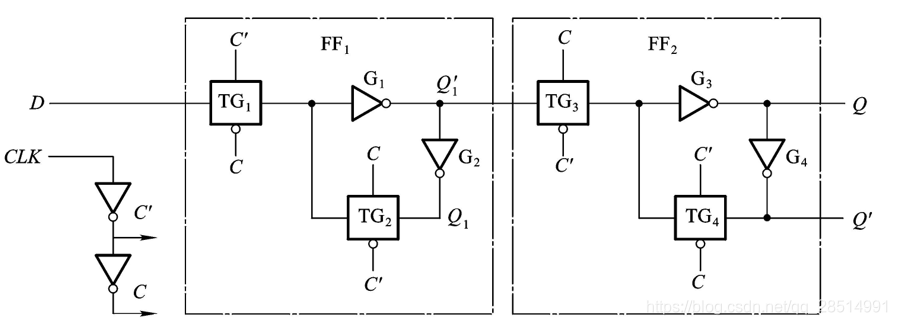

电平触发器构成的边沿触发器

图7是用两个电平触发D触发器组成边沿触发D触发器的原理性框图,目前在CMOS集成电路中主要采用这种电路结构形式制作边沿触发器。

工作原理

- CLK=0时,FF1开通,Q1随D变而变, FF2保持;

- CLK=↑时,FF1保持, FF2开通,Q=Q1;

- CLK=1时,FF1保持, FF2开通,不变。

动作特点

- Q的变化发生在CLK的上升沿或下降沿

- Q*仅取决于CLK边沿时的输入信号,而与之前、后的状态无关。

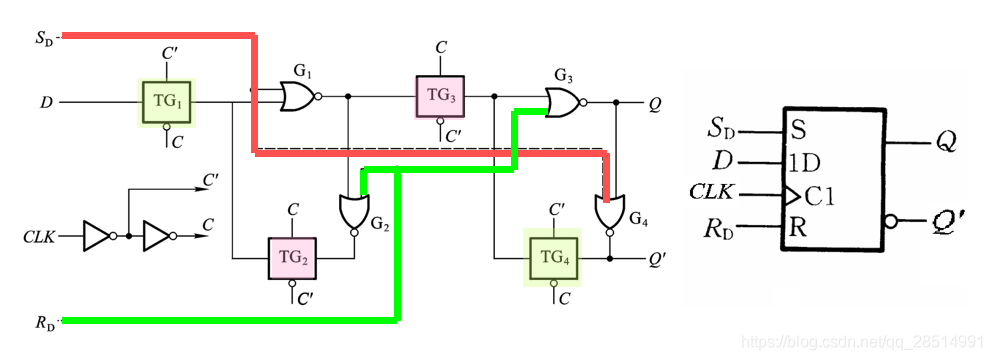

带异步置位和复位功能的CMOS边沿触发的D触发器

分析略

脉冲触发的触发器

为了提高触发器工作的可靠性,希望在每一个CLK周期里输出端的状态只能改变一次。在电平触发器的基础上又设计出了脉冲触发器(也称主从触发器)。

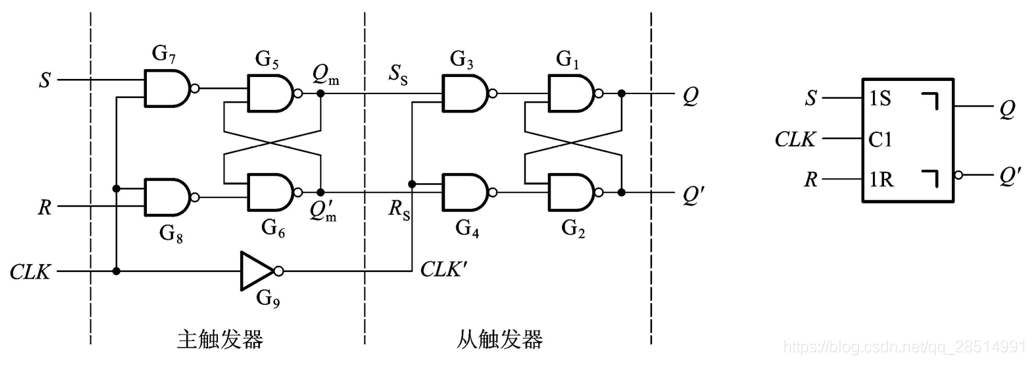

主从SR触发器

工作原理-总结

- 当CLK=1时,G7 、G8门被打开,主触发器状态翻转,G3 、G4门被封锁,从触发器状态保持;

- 当CLK=↓时,G7 、G8门被封锁,主触发器状态保持,G3 、G4门被打开,从触发器状态翻转;

- 当CLK=0时,G7 、G8门被封锁,主触发器状态保持,G3 、G4门被打开,从触发器状态不变;

总结:脉冲触发一时钟周期内只翻转一次,翻转发生在CLK下降沿↓的时候。

缺点:

- CLK=1期间内,Qm的状态仍然会随着S、R变化而变化。

- 仍要遵守 SR=0的约束条件

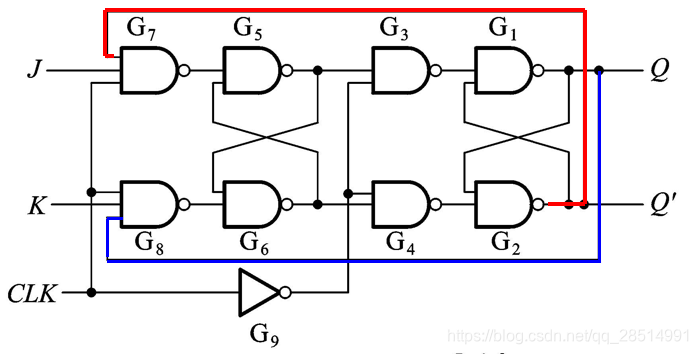

主从JK触发器

主从SR触发器仍要遵守 SR=0的约束条件,否则在 和

和 同时回到0后,无法确定触发器的次态。为了解除这一约束,如果我们规定当输入S=R=1时,触发器的次态为初态的反状态,即Q*=Q',这样触发器的次态也能确定了。不难想象,在SR触发器的基础上,如果当S=R=1时,将Q和Q'的接回到输入端,用Q'代替S端的输入,用Q代替R端的输入,就可以实现上述要求了。

同时回到0后,无法确定触发器的次态。为了解除这一约束,如果我们规定当输入S=R=1时,触发器的次态为初态的反状态,即Q*=Q',这样触发器的次态也能确定了。不难想象,在SR触发器的基础上,如果当S=R=1时,将Q和Q'的接回到输入端,用Q'代替S端的输入,用Q代替R端的输入,就可以实现上述要求了。

满足约束条件:SR=JQ’KQ=0。

触发器按逻辑功能的分类

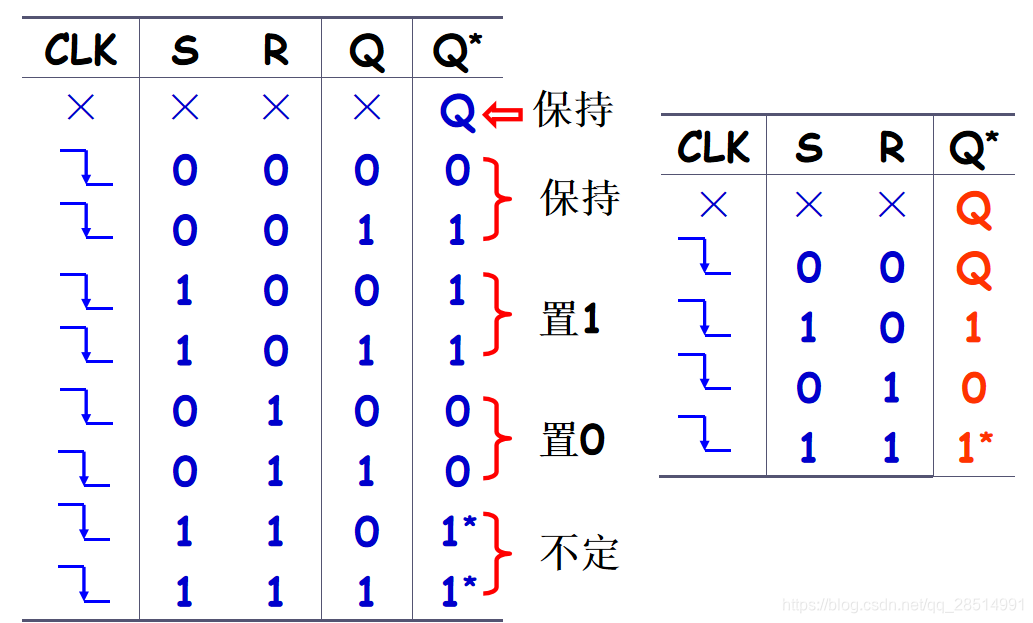

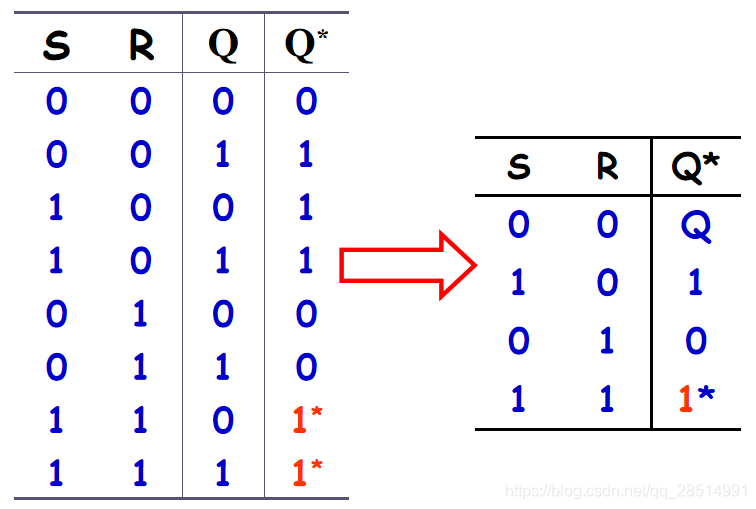

SR触发器

凡在CLK作用下逻辑功能符合下述特性表的触发器都属于SR触发器

特征方程

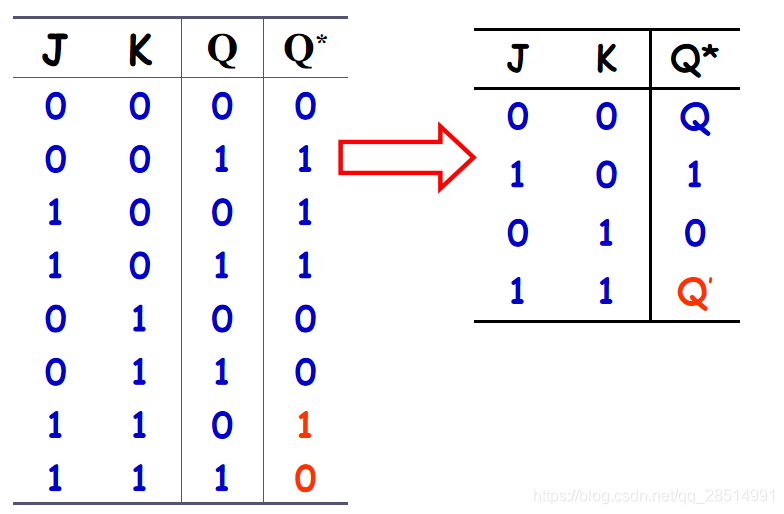

JK触发器

凡在CLK作用下逻辑功能符合下述特性表的触发器都属于JK触发器

特征方程

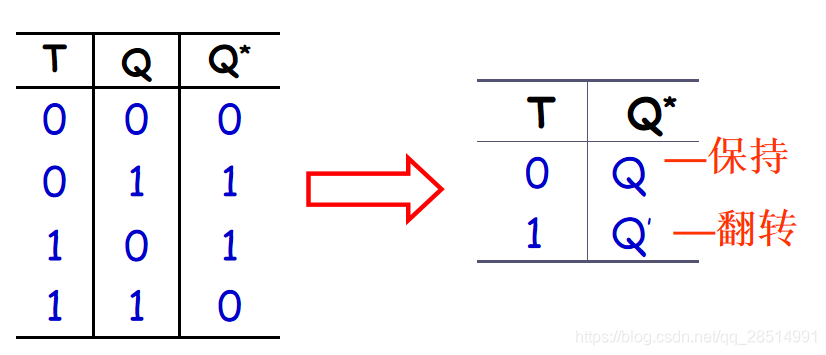

T和T’触发器触发器

具有保持和翻转功能的触发器称T触发器

特征方程

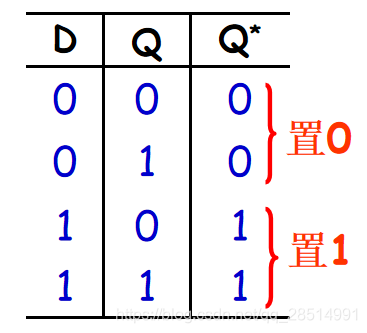

D触发器

凡在CLK作用下逻辑功能符合下述特性表的触发器都属于D触发器

特征方程

不同功能触发器的相互转换

- JK触发器的功能最强,包含了SR、D、T触发器所有的功能;

- 目前生产的触发器定型的只有D和JK触发器;

- 可用JK和D触发器实现其它功能触发器。

D - JK,T,T’

JK-D,T,T’

触发器的动态特性

建立时间 :输入信号先于CLK动作沿到达时间。

:输入信号先于CLK动作沿到达时间。

保持时间 :CLK动作沿到达后输入信号仍需保持不变的时间。

:CLK动作沿到达后输入信号仍需保持不变的时间。

传输延迟时间 :CLK动作沿开始到输出新稳态所建立时间。

:CLK动作沿开始到输出新稳态所建立时间。

最高时钟频率:触发器在连续、重复翻转的情况下,时钟信号可以达到的最高重复频率。

集成电路触发器产品的动态参数往往需要通过实验来测定。

寄存器

功能:用于存储一组二值代码的电路。一个触发器存储一位二值信号,N个触发器组成的N位寄存器,存储N位二值信号。

结构:输入输出直接引出。

实现:只要求有置1和置0功能的触发器都可以实现。

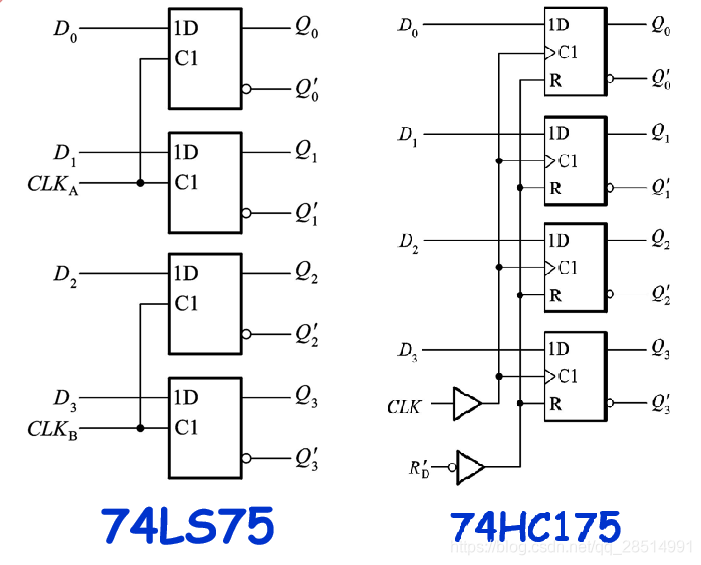

示例

存储器

功能:一种能存储大量二值信息(二值数据)的半导体器件。

结构:利用地址码分配输入输出。

分类:按存取方式:只读存储器ROM(Read Only Memory)和随机存取存储器RAM(Random Access Memory)。按半导体器件:双极型和MOS型。

静态随机存储器(SRAM)

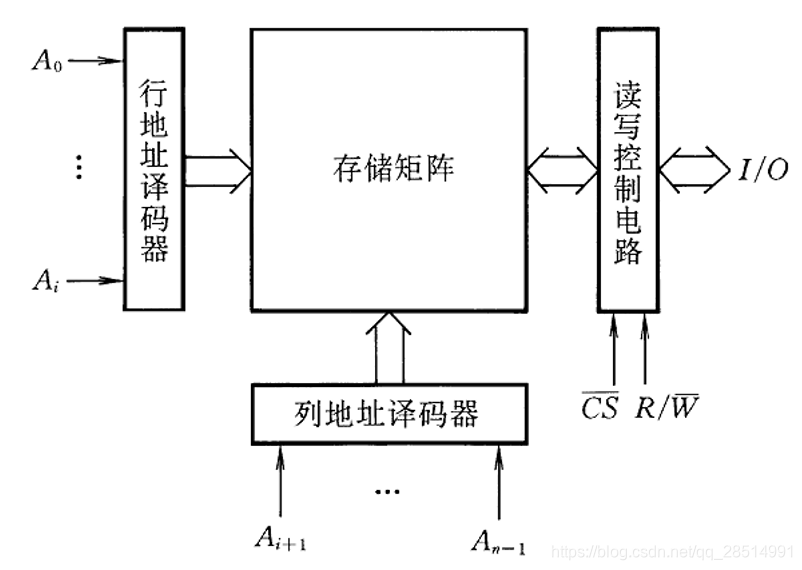

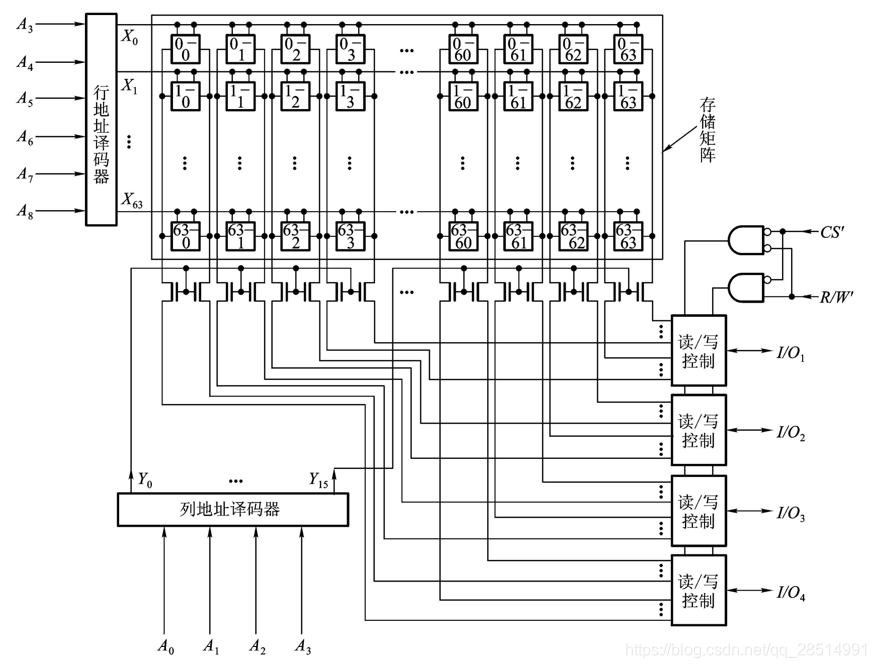

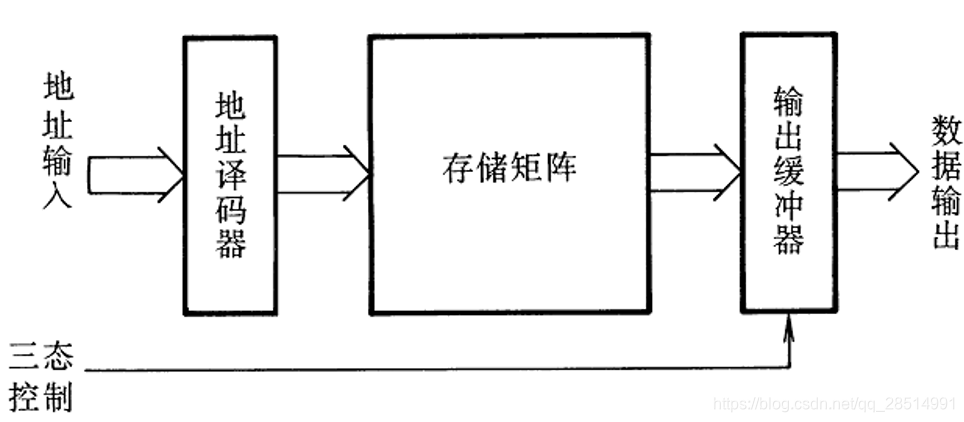

电路结构:SRAM电路通常由存储矩阵、地址译码器和读/写控制电路三部分组成。如图19所示。

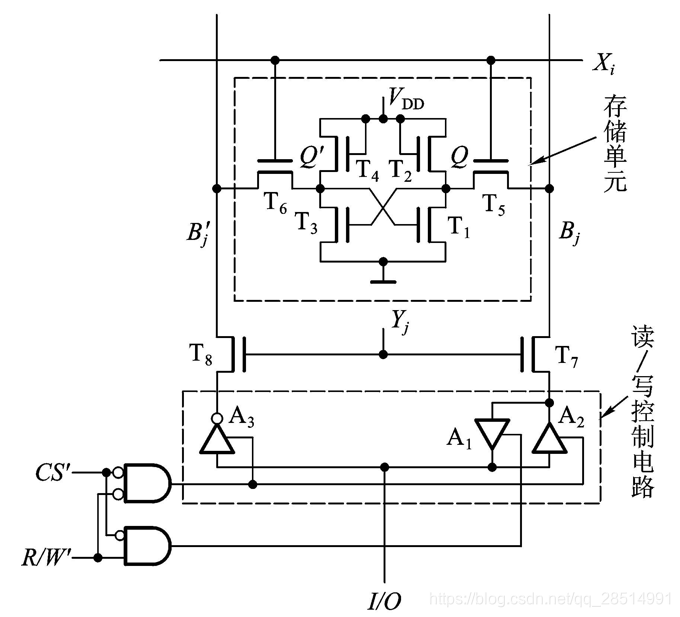

静态存储单元:

静态存储单元是在SR锁存器的基础上附加门控管而构成的,图21是用六只MOS管组成的CMOS静态存储单元。分析略。

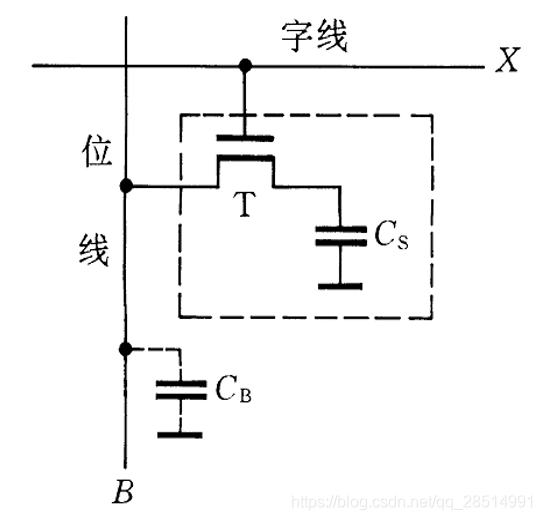

动态随机存储器( DRAM )

静态RAM存储单元所用的管子多,功耗大,集成度受到限制,为了克服这些缺点,人们研制了动态RAM。动态RAM存储数据的原理是基于MOS管栅极电容存储效应。由于漏极电流的存在,电容上存储的数据不能长久保存,因此必须定期给电容补充电荷,以避免存储数据的丢失,这种操作称为再生或刷新。

只读存储器ROM

在存储器的某些应用场合中,要求存储的是一些固定不变的数据。正常工作状态下,这些数据只供读出使用,不需要随时修改,为了适应这种需求,又产生了另外一种类型的存储器-只读存储器。

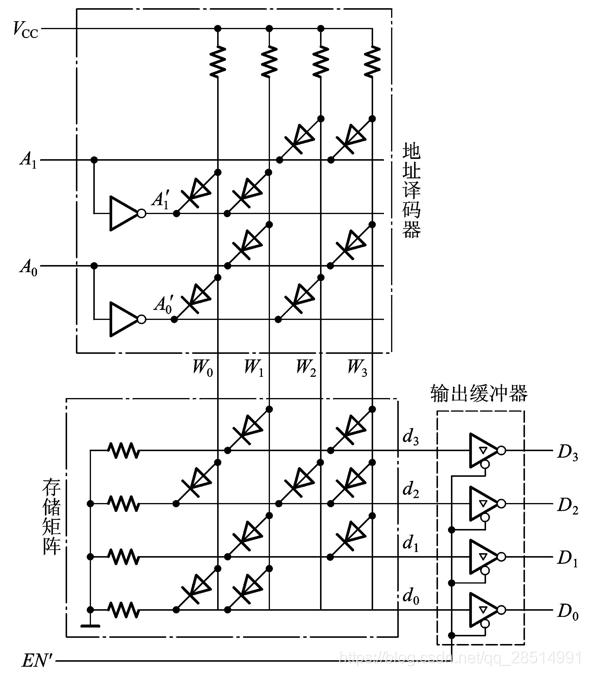

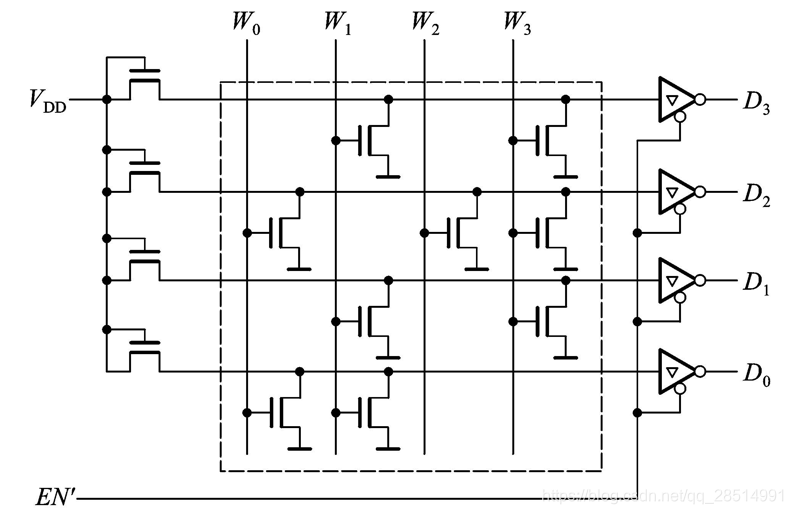

电路结构与原理

ROM的的电路结构包含存储矩阵、地址译码器和输出缓冲区三个组成部分,如图23所示。存储矩阵由许多存储单元排列而成。存储单元可以用二极管构成,也可以用双极型三极管或MOS管构成。地址译码器的作用是将输入的地址代码译成相应的控制信号,利用这个控制信号从存储矩阵中将指定的单元选出,并把其中的数据送到输出缓冲器。输出缓冲器的作用有两个,一是能提高存储器的带负载能力,二是实现对输出状态的三态控制,以便于系统的总线连接。

ROM的分类

掩模ROM(Mask ROM)

只读存储器(Read-Only Memory)是一种只能读取资料的存储器。在制造过程中,将资料以一特制光罩(mask)烧录于线路中,其资料内容在写入后就不能更改,所以有时又称为“光罩式只读内存”(mask ROM)。此内存的制造成本较低,常用于电脑中的开机启动如启动光盘,在系统装好的电脑上时,计算机将C盘目录下的操作系统文件读取至内存,然后通过cpu调用各种配件进行工作这时系统存放存储器为RAM。

可编程只读存储器(PROM)

可编程只读存储器(Programmable ROM,PROM)内部有行列式的熔丝,是需要利用电流将其烧断,写入所需的资料,但仅能写录一次。 PROM在出厂时,存储的内容全为1,用户可以根据需要将其中的某些单元写入数据0(部分的PROM在出厂时数据全为0,则用 户可以将其中的部分单元写入1), 以实现对其“编程”的目的。PROM的典型产品是“双极性熔丝结构”,如果我们想改写某些单元,则可以给这些单元通以足够大的电流,并维持一定的时间,原 先的熔丝即可熔断,这样就达到了改写某些位的效果。另外一类经典的PROM为使用“肖特基二极管”的PROM,出厂时,其中的二极管处于反向截止状态,还 是用大电流的方法将反相电压加在“肖特基二极管”,造成其永久性击穿即可。

可抹除可编程只读存储器(EPROM)

可抹除可编程只读存储器(Erasable Programmable Read Only Memory,EPROM)可利用高电压将资料编程写入,抹除时将线路曝光于紫外线下,则资料可被清空,并且可重复使用。通常在封装外壳上会预留一个石英透明窗以方便曝光。

一次编程只读存储器(OTPROM)

一次编程只读存储器(One Time Programmable Read Only Memory,OTPROM)之写入原理同EPROM,但是为了节省成本,编程写入之后就不再抹除,因此不设置透明窗。

电子式可抹除可编程只读存储器(EEPROM)

电子式可抹除可编程只读存储器(Electrically Erasable Programmable Read Only Memory,EEPROM)之运作原理类似EPROM,但是抹除的方式是使用高电场来完成,因此不需要透明窗。

快闪存储器(Flash memory)

快闪存储器(Flash memory)的每一个记忆胞都具有一个“控制闸”与“浮动闸”,利用高电场改变浮动闸的临限电压即可进行编程动作。

存储容量的扩展

当一片ROM或RAM不能满足存储容量要求时,就需要将ROM或RAM组合起来,组成一个容量更大的存储器。有位扩展和字扩展两种方法。

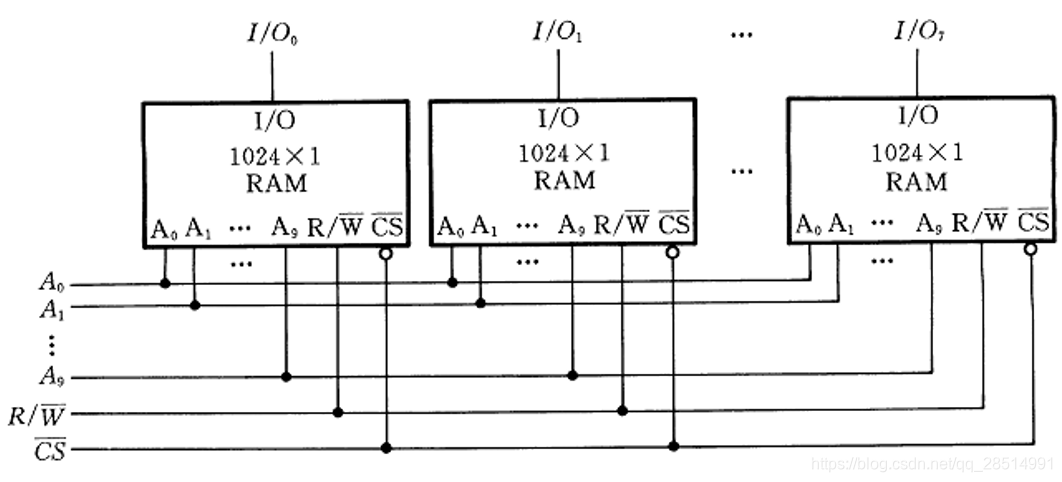

位扩展方式:地址线共用,而数据线并行使用。

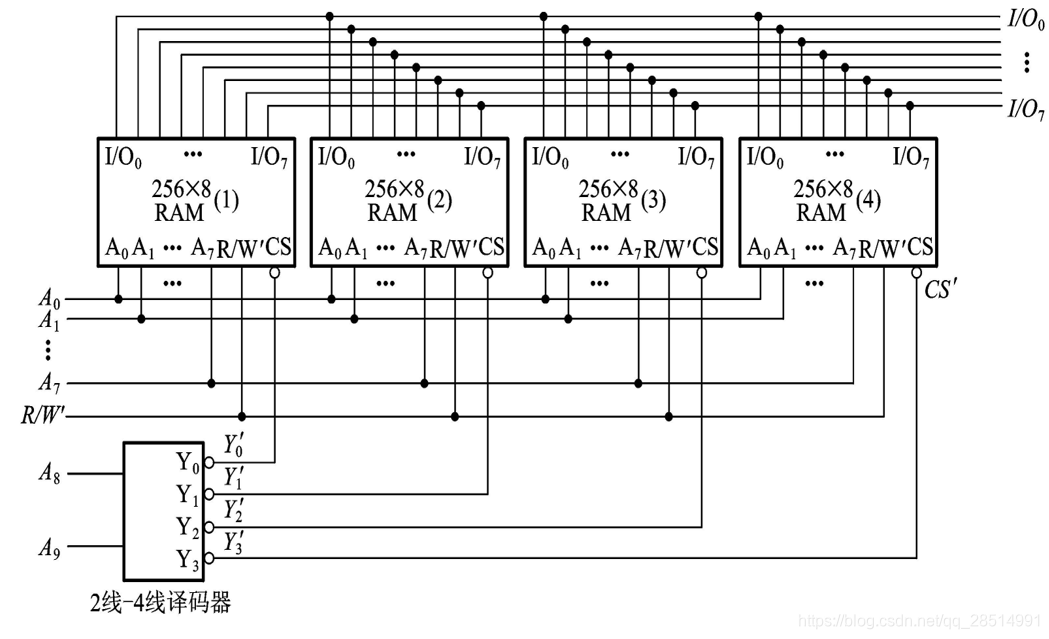

字扩展方式:数据线共用,地址线扩展。

用存储器实现组合逻辑电路

一个存储器在填入数据后可以看做一个真值表,即等价于一个逻辑函数。

参考链接

《数字电子技术基础》(第六版)高等教育出版社

https://wenku.baidu.com/view/b65eb61f5ebfc77da26925c52cc58bd6308693d8.html

https://wenku.baidu.com/view/e2d822440166f5335a8102d276a20029bd64633d.html

https://wenku.baidu.com/view/5026871e844769eae109ed0d.html

https://www.diangon.com/wenku/rd/danpianji/201505/00023800.html

https://baike.baidu.com/item/ROM/12424911

5850

5850

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?