这篇主要是翻译《Tessent MemoryBIST User's Manual For Use with Tessent Shell》的第二章前五节的内容,在这里作为一个学习的记录,仅供参考。(部分流程名词不作翻译,防止翻译不准引起歧义)

欢迎大家关注微信公众号“微电子之路”,后续继续更新关于TessentMBIST的学习记录。

2. Getting Started

本章介绍如何开始在Tessent Shell中插入 Tessent MemoryBIST,并包括显示最常见场景和用法的示例。如果您在具有可修复存储器的设计中插入memory BIST,一些流程步骤会有所不同,这也在下面进行了描述。

有关完整的包装器和属性描述,请参考《Tessent Shell Reference Manual》中“DftSpecification Configuration Syntax”、“PatternsSpecification Configuration Syntax” 和“DefaultsSpecification Configuration Syntax”部分的“MemoryBist”和“MemoryBisr”部分。在子块、物理块或芯片级插入memory BIST的流程和主要步骤是相同的。

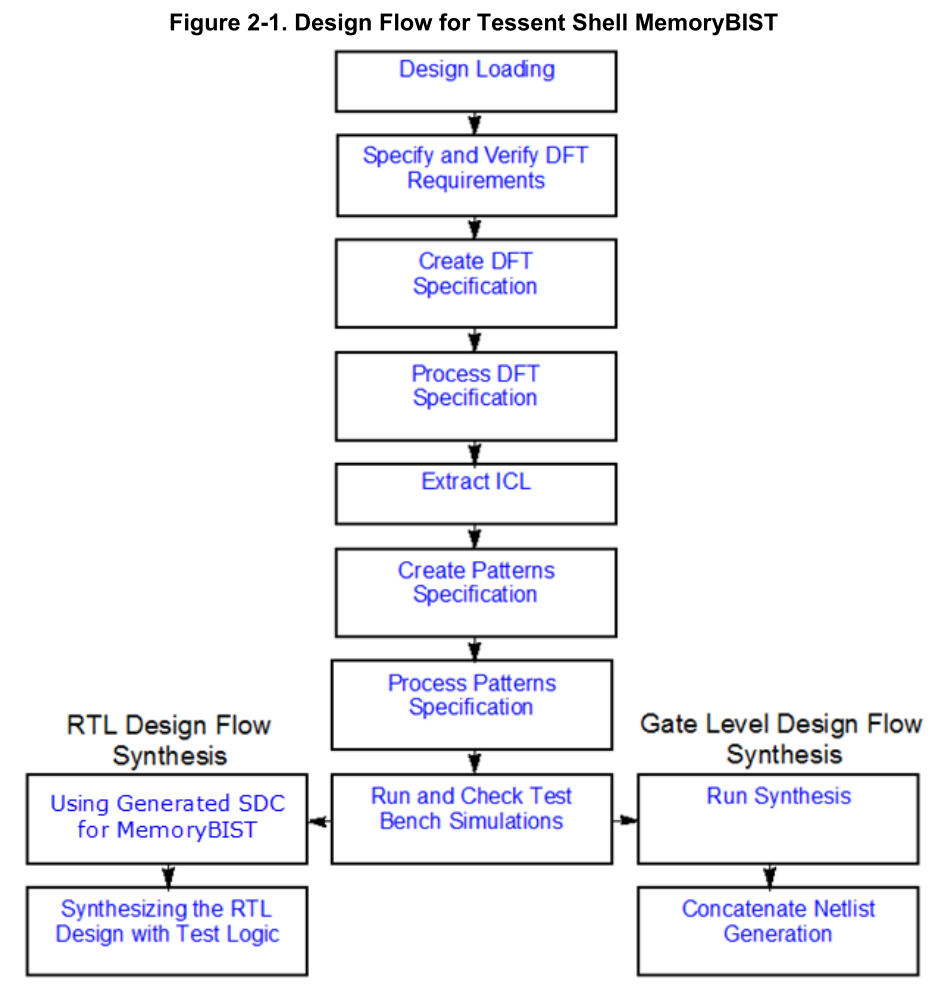

2.1 使用Tessent Shell的DFT流程

Tessent Shell中的Tessent MemoryBIST有一个高级别的流序列。图2-1说明了将内存内建自测试插入设计所需的高级步骤序列。图中的每一步都链接到关于测试设计流程的更详细的信息,包括示例。

2.1.1 Prerequisites

要在设计中插入memory BIST,您必须有一个RTL或门级网表以及memory BIST库。

如果设计包含标准单元,还需要Tessent 单元库或ATPG库。对于其他既没有RTL模型也没有库模型的IP块,可以使用带有-interface_only选项的read_verilog或read_vhdl命令加载仿真模型。这指示该工具忽略文件名参数中指定的所有模块的内部,只提取模块端口定义和参数。

2.1.2 Design Flow Dofile Example

本节中的dofile示例向您展示了如何设置设计流程。下面的dofile示例建立了图2-1中描述的设计流程。

1)Design Loading

set_context dft -rtl

read_cell_library ../library/adk.tcelllib

set_design_sources -format verilog -y {../library/mem ../design/rtl} -extension v

set_design_sources -format tcd_memory -y ../library/mem -extension lib

read_verilog ../design/rtl/blockA.v

set_current_design blockA

2)Specify and Verify DFT Requirements

set_design_level physical_block set_dft_specification_requirements -memory_test on add_clocks CLK -period 12ns -label clka check_design_rules

3)Create DFT Specification

set spec [create_dft_specification] report_config_data $spec

4)Process DFT Specification

process_dft_specification

5)Extract ICL

extract_icl

6)Create Patterns Specification

create_patterns_specification

7)Process Patterns Specification

process_patterns_specification

8)Run and Check Test Bench Simulations

run_testbench_simulations check_testbench_simulations

9)Test Logic Synthesis

run_synthesis

2.2 Design Loading(加载设计)

加载设计是使用Tessent Shell插入Tessent MemoryBIST的第一步。该步骤包括设置正确的context、读取库、读取设计和阐述( elaborating)设计。

2.2.1 Set the Context(设置context)

在Tessent Shell中,设置context意味着两件事。首先,您必须将context设置为dft,以便创建memory BIST硬件。第二,你必须指定要读入的设计类型是否用RTL书写。如果是这样,你必须指明 -rtl。如果要读入的设计是门级的Verilog网表,您应该指定-no_rtl。当使用-no_rtl模式时,级联网表在dft插入阶段结束时被写出。在rtl模式下,输入设计的文件结构被保留,只有修改后的设计文件在dft插入阶段结束时与新创建的测试IP一起被写出。要读入的网表可以是Verilog、VHDL或混合语言。

如果memory BIST已经被插入到一个现在集成到设计的更高层次的块中,您必须使用open_tsdb命令打开子块(memory BIST插入子块sub_block或物理块physical_block)的Tessent Shell Data Base(TSDB)。如果您对子代和父代使用相同的TSDB,则可以重用TSDB(默认为tsdb_outdir),并且不需要显式打开默认的TSDB,因为TSDB输出目录的现有内容对该工具是自动可见的。有关如何控制TSDB输出目录的名称和位置,请参见set_tsdb_output_directory命令描述。

1)例1

以下示例将context设置为dft,并指定要读入的设计是用RTL编写的。

set_context dft -rtl

2)例2

以下示例将上下文设置为dft,并指定将读入门级网表。

set_context dft -no_rtl

3)例3

下面的示例打开一个子级的TSDB目录,因此在父级公开它。

open_tsdb ../core_tsdb_outdir

2.2.2 Read the Libraries(读取库)

您可以使用read_cell_library命令在库文件中读取在设计中实例化的库单元。当将memory BIST插入到RTL-only设计中时,读取memory BIST库就足够了,但这并不典型,因为一些库单元在RTL设计中被实例化用于焊盘单元(pad cells)和时钟控制。当Tessent单元库不包含焊盘信息时,LV pad库本身受read_cell_library命令支持,可用于用焊盘信息扩充Tessent单元库。

Memory BIST库被认为是Tessent Shell中的Tessent核心描述(Tessent core descriptions,TCDs),被加载并被称为TCDs。LV flow的memory BIST模型与Tessent Shell兼容,无需修改,并在flow中被加载和称为TCDs。

1)例1

下面的例子显示了如何在Tessent单元库中读取pad IO macros(宏)。

read_cell_library ../library/adk_complete.tcelllib

2)例2

以下示例显示了如何在memory BIST模型中显式读取。

read_core_descriptions ../library/128x64_RAM.memlib

3) 例3

下面的例子展示了如何使用set_design_sources来引用memory BIST库。将tcd_memory类型用于-format选项向工具指示期望读入memory库文件。

set_design_sources -format tcd_memory -y ../library/memlibs -extensions memlib

4)Flow Variation for Repairable Memories(可修复存储器的流程变化)

用作Tessent MemoryBIST输入的memory库文件必须包含特定的包装器,以便能够生成和插入修复逻辑。

冗余分析(RedundancyAnalysis)包装器对于生成计算内存修复方案的BIRA逻辑是必要的。冗余分析包装器内的PinMap子包装器对于生成用于将修复解决方案转移到内存的BISR逻辑是必要的。

通常,内存BIST库文件由内存IP提供商提供和认证,无需进一步修改即可使用。

2.2.3 Read the Design

在Tessent Shell中,设置context并加载所需的库后,可以使用read_verilog命令读入设计。

在此步骤中还可以加载memory放置(DEF,Design Exchange Format文件)和电源域(power domain)数据(UPF,Unified Power Format和CPF,Common Power Format文件)。这些数据会影响memory分区和memory BIST控制器分配方面的memory BIST规划。

1)例1

以下示例显示了如何读入一个网表,它可以是RTL或门级。

read_verilog ../netlist/cpu_top.v

2)例2

下面的示例显示了如何指定一个文件和一个目录库来搜索Verilog模块。

set_design_sources -format verilog -v ../design/top.v -y ../design -extensions v gv

对于每种格式类型,set_design_sources只能设置一次。如果给定格式使用多个set_design_sources,将使用给定文件类型的最后一个set_design_sources。如果需要,-v和-y选项接受路径列表。

3)例3

以下示例显示了如何读入包含memory放置信息的DEF(Design Exchange Format,设计交换格式)文件和描述与存储器相关联的电源域(power domain)的UPF(Unified Power Format,统一电源格式)文件。

read_upf ../data/design/power/blockA.upf

read_def ../data/design/layout/blockA.def

2.2.4 Elaborate the Design

设计加载的下一步是使用set_current_design命令详细说明设计。

set_current_design命令指定所有将作用于的设计的根(the root of the design)后续操作。如果缺少任何模块描述,设计细化(design elaboration)会识别它们。对于memory BIST插入,如果模块不包含存储器或在存储器的扇入(fanin)中不包含时钟树元素,则允许模块没有定义。您可以使用add_black_box -module命令来指定它们。

例子

以下示例显示了如何使用set_current_design命令。

set_current_design blockA

2.2.5 Report the Design Data

您可以使用几个命令来检查加载的设计和关联的库。更常用的报告命令示例如下。

1)例1

以下示例执行set_design_sources,然后报告将被引用的设计源。

> set_design_sources -format verilog -y {../data/design/mem ../data/design/rtl} -extension v

> report_design_sources

// ICL search_design_load_path: activated

// BoundaryScan search_design_load_path: activated

// Scan search_design_load_path: activated

// ----------------------------------------------------

// format type path file extensions

// ------- ---- -------------------- ---------------

// Verilog dir '../data/design/mem' 'v v.gz'

// Verilog dir '../data/design/rtl' 'v v.gz'

2)例2

以下示例报告了当前加载进Tessent Shell的memory模型以及其他测试核心描述。使用-levels 1选项仅显示核心名称和类型。如果未设置此选项,将显示整个模型内容,

> report_config_data -partition tcd -levels 1

Core(SYNC_1R1W_16x8) {

Memory {

// Not shown

}

}

Core(SYNC_1RW_32x16) {

Memory {

// Not shown

}

}

Core(SYNC_2R2W_12x8) {

Memory {

// Not shown

}

}

如果加载了除memory以外的核心描述,它们也会显示在此报告中。

3)例3

下面的例子报告了在设计过程中发现的memory实例。

> report_memory_instances // // Memory Instance: blockA_l1_i1/blockA_l2_i1/mem1 // ---------------------------------------------- // bist_data_in_pipelining : off // physical_cluster_override : // power_domain_island : // test_clock_override : // use_in_memory_bist_dft_specification : auto // use_in_memory_bisr_dft_specification : auto // // Memory Instance: blockA_l1_i1/blockA_l2_i1/mem2 // ---------------------------------------------- // bist_data_in_pipelining : off // physical_cluster_override : // power_domain_island : // test_clock_override : // use_in_memory_bist_dft_specification : auto // use_in_memory_bisr_dft_specification : auto

此报告命令提供了附加属性信息以及memory实例路径。这些属性可以通过加载附加设计数据(如指定电源域岛(power domain islands)的UPF文件)来间接设置,也可以使用set_memory_instance_options命令显式更改

2.3 Specify and Verify DFT Requirements

在Tessent Shell中插入memoryBIST的下一步是指定DFT需求,添加约束,并通过运行DRC(设计规则检查)来验证指定的DFT需求是否正确。

2.3.1 Set DFT Specification Requirements(设置DFT规格要求)

要插入memoryBIST,必须使用set_dft_specification_requirements命令指定DFT规范要求。这使DRC专用于memoryBIST,并指示create_dft_specification命令包含memory BIST包装器。

例子

以下示例显示了如何指定memory BIST DFT规范要求,以及如何将设计级别定义为芯片级别。

set_dft_specification_requirements -memory_test on

set_design_level chip

Flow Variation for Repairable Memories(可修复memory的流程变化)

当设计包含可修复memory时,使用set_dft_specification_requirements命令时,必须考虑其他选项。

当使用 set_dft_specification_requirements -memory_test on 时,默认情况下,设置以下与可修复存储器相关的附加选项:

-memory_bisr_chains auto

-memory_bisr_controller auto

在大多数情况下,您不需要更改这些默认值。

当-memory_bisr_chains设置为auto时,如果当前设计实例化包含尚未连接到存储器BISR寄存器的可修复存储器的块,则添加BISR寄存器。当-memory_bisr_controller设置为auto,set_design_level设置为chip时,设计中会添加一个bisr控制器。

如果-memory_bisr_chains和-memory_bisr_controller设置为off,则不会在设计中插入bisr链和bisr控制器,从而有效地禁用整个设计的BISR。

要禁用特定memory实例的BISR寄存器生成,请使用set_memory_instance_options命令,并将-use_in_memory_bisr_dft_specification 选项设置为off。以下示例禁用memory实例mem4的BISR寄存器的生成,即使内存有修复资源。

SETUP> set_memory_instance_options blockA_clka_i1/mem4 -use_in_memory_bisr_dft_specification off

2.3.2 Add Properties and Constraints (添加属性和约束)

您可以添加或更改会影响DFT规范创建的属性和约束。

1)例1

要在芯片级插入memoryBIST,四个TAP引脚(TDI、TCK、TMS和TDO)必须在芯片级可用,并连接到pad IO macros。可选的TRST可以是上电检测器(power-up detector)的输出引脚。如果TAP引脚已经命名为tck、tdi、tms tdo和trst,则自动设置该功能。

以下示例显示了如何指定五个TAP引脚(tck_p、tdi_p、tms_p、trst_p、tdo_p)。

set_attribute_value tck_p -name function -value tck set_attribute_value tdi_p -name function -value tdi set_attribute_value tms_p -name function -value tms set_attribute_value trst_p -name function -value trst set_attribute_value tdo_p -name function -value tdo

2)例2

以下示例添加了额外的属性,用于连接芯片级的基本fuse box,这些属性不是从fuse box模型中推断出来的。

set_config_value -in /DftSpecification(top,rtl)MemoryBisr/Controller/repair_clock_connection clkb set_config_value -in /DftSpecification(top,rtl)MemoryBisr/Controller/programming_voltage_source vddq set_config_value -in /DftSpecification(top,rtl)MemoryBisr/Controller/repair_trigger_connection bisr_rstn

3)例3

您可以使用DefaultsSpecification包装器来更改许多内置默认值,以匹配您的首选项和要求。默认设置机制还带有一个DefaultsSpecification包装器的层次结构,使您能够拥有公司、组和用户级别的默认设置。

以下示例显示了如何创建公司memory BIST DefaultsSpecification。

生成一个包含memory BIST所有默认选项的文件:

report_config_syntax DefaultsSpecification/DftSpecification/MemoryBist > company.tessent_defaults

下面是company.tessent_defaults文件的一个片段:

DefaultsSpecification(<policy>) { // legal: company group user

DftSpecification {

MemoryBist {

clock_partitioning : <string>; // legal :

// (per_clock_domain)

// per_sync_clock_group

max_steps_per_controller : <int>; // default: unlimited

max_memories_per_step : <int>; // default: unlimited

max_test_time_per_controller : <time>; // default: 500ms {

// symbols: unlimited }

max_power_per_step : <milli_watts>; // default: 500

// { symbols:

// unlimited }

single_memory_dimension_per_step : <boolean>; // default: off

ControllerOptions {

...您可以使用此文件创建公司memory BIST默认值指定如下:

DefaultsSpecification(Company) {

DftSpecification {

MemoryBist {

clock_partitioning : per_clock_domain;

max_steps_per_controller : 5;

max_memories_per_step : 10;

max_test_time_per_controller : 1000ms;

max_power_per_step : 250;

single_memory_dimension_per_step : Off;

ControllerOptions {

... 可以通过在.tessent_startup文件中引用或显式使用read_config_data命令来自动读取创建的DefaultsSpecification。

2.3.3 Define Clocks

“ Specify and Verify DFT Requirements”中的下一步是使用add_clocks命令定义时钟。在详细设计时,Tessent Shell会自动跟踪从内存时钟引脚到时钟源的时钟。

有关定义时钟和相关时钟DRC的详细说明,请参考 Tessent Shell Reference Manual中的add_clocks命令。

1)例1

下面的例子表明,使用简单的时钟路径(在这种情况下,从主设计时钟引脚到由导线和缓冲器组成的memory的路径),您只需要定义时钟周期并参考时钟源引脚。原因是时钟路径将自动从被测memory跟踪到时钟源引脚。-label选项使您能够指定符号名称。如果不设置此选项,将自动生成标签名称。

add_clocks CLK -period 12ns -label blockA_ram_clk

2)例2

以下示例定义了一个来自锁相环的内部时钟源,用于驱动存储器。

add_clocks clk_ref -period 10ns -label clk_ref

add_clocks U_PLL/VCO -label clk_100mhz -reference U_PLL/REF -freq_multiplier 4

第一个add_clocks命令定义了作为锁相环参考的时钟源。第二个add_clocks命令定义内部时钟源,该时钟源参考同一实例的输入引脚驱动存储器。DRC将该参考引脚追踪到其源极,在这种情况下是clk_ref端口。

2.3.4 Run DRC

“Specify and Verify DFT Requirements”的下一步是运行设计规则检查(DRC),以确保所有约束都是正确的。一旦DRC被清除,Tessent Shell从SETUP 进入ANALYSIS提示。

check_design_rules

如果您的设计在memory时钟路径中包含时钟门控单元,请参见add_dft_clock_enables命令描述。如果您的设计包含必须控制的多路复用器,请参见add_dft_control_points命令描述。最后,要在存储器时钟路径中插入多路复用器,请参见add_dft_clock_mux命令描述。

如果设计设置有任何问题,例如时钟定义不正确,将会发生时钟DRC规则违规,您必须先解决这些问题,然后才能继续下一个流程步骤。

Flow Variation for Repairable Memories (可修复memory的流程变化)

BISR chains根据一个名为<design_name>.bisr_segment_order的文件的内容进行连接,该文件由DftSpecification/

MemoryBisr/bisr_segment_order_file属性指定。当运行check_design_rules时,该文件在当前工作目录中自动生成,并包含定义BISR链顺序的memory实例列表。默认情况下,列表按电源域岛(power domain islands)(如果加载了UPF或CPF)和内存实例名称排序。如果加载了DEF文件,顺序也会受到物理内存放置的影响。

如果默认的BISR chain order不令人满意,您可以通过以下两种方式之一影响BISR chain order。

第一种方法包括在执行process_dft_specification命令之前,手动修改<design_name>.bisr_segment_order文件中内存实例名称的顺序。如果您需要稍后在同一Tessent Shell调用或后续调用期间重新运行check_design_rules分析,以重用修改后的<design_name>.bisr_segment_order文件,则必须在仍处于setup模式时指定 set_memory_instance_options -bisr_segment_order_file 命令选项。

例如,下面的命令指示应该保留文件modA.bisr_segment_order,并在执行下一个check_design_rules命令时用于确定BISR链顺序。

SETUP> set_memory_instance_options -bisr_segment_order_file modA.bisr_segment_order

影响BISR链顺序的第二种方式包括使用read_def命令读取与设计相对应的DEF文件。在执行set_current_design命令后,该文件应在setup模式下加载到Tessent Shell中。例如,下面的命令读取对应于设计modA的DEF文件。基于在DEF文件中找到的memory放置信息来确定BISR链排序。

SETUP> read_def modA.def

bisr_segment_order_file的文件名是任意的,不需要是默认名称。

2.4 Create DFT Specification

下一步是创建一个DFT规范。

使用create_dft_specification命令,根据上一步中指定的DFT要求创建默认的DFT规范。您可以使用report_config_data命令来报告创建的DFT规范。有几种不同的方法可以编辑或配置DFT规范,以满足自定义要求。

2.4.1 Invoke create_dft_specification

基于上一步描述的DFT规范要求,使用create_dft_specification命令自动创建一个DFT规范。该DFT规范存储在memory中。

要在memory中报告DFT规范,请使用report_config_data命令。DFT规范包括用于指定编程BIST控制器所需的访问电路的IjtagNetwork包装器和用于指定MemoryBIST配置的MemoryBist包装器。IJTAG网络完全符合IEEE 1687标准。

例子

在下面的示例中,用create_dft_specification生成的DFT规范存储在一个名为dft_spec的变量中,以便该变量可以用于报告DFT规范。

set dft_spec [create_dft_specification]

report_config_data $dft_spec

2.4.2 Edit/Configure the DFT Specification According to Your Requirements

根据您的要求,使用以下方法之一编辑或配置创建的DFT规范。如果您想按原样使用默认配置,则不需要编辑DFT规范。

1)方法1:改变设计约束,重新生成DFT规范

在这种方法中,生成DFT规范后,返回setup模式,更改一个memory实例选项并重新生成DFT规范。在这种情况下,physical_cluster_size_ratio从默认值20%更改为40%。

set_system_mode setup

set_memory_instance_options -physical_cluster_size_ratio 40

check_design_rules

create_dft_specification -replace

2)方法2:使用图形用户界面编辑DFT规范

在这种方法中,您使用图形用户界面来编辑已经创建的DFT规范。

首先,用display_specification命令打开GUI。图形用户界面根据“指定和验证DFT要求”步骤中指定的DFT要求显示DFT规范。您使用图形用户界面进行的编辑和应用会更新memory中的DFT规范。如果您希望流程下次在没有图形用户界面编辑的情况下工作,并且更加基于脚本,您可以使用report_config_data命令显示您所做的编辑,然后您可以使用read_config_data命令将它们添加到DFT规范中。

3)方法3:修改memory中的DFT规范

另一种方法是使用add_config_element和set_config_value命令修改DFT规范。这样,每次运行同一个flow时,都会调用编辑,因此,如果需要的话,会使您的Tcl文件或dofile在迭代中可重复。

2.4.3 Validate the DFT Specification(验证DFT规范)

在此可选但推荐的步骤中,您可以验证对DFT规范所做的编辑,以确保在继续下一步之前不存在错误。

例子

以下示例显示了如何验证您的DFT规范,以便在处理之前检查问题或错误。

process_dft_specification -validate_only

2.5 Process DFT Specification

下一步是处理在上一步中创建、编辑和验证的DFT规范。此步骤为DFT规范中的所有组件创建并插入硬件。

2.5.1 Create DFT Hardware with the DFT Specification 使用DFT规范创建DFT硬件

使用process_dft_specification命令生成并在设计中插入DFT规范要求的所有DFT硬件。对于Tessent MemoryBIST,在芯片级插入时,会插入TAP控制器。当在物理和子块级别插入memory BIST时,会插入一个IJTAG主机扫描接口。

例子

以下示例显示了如何生成并在设计中插入DFT规范要求的硬件

process_dft_specification

2193

2193

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?