ICC学习——LAB2设计规划

学习目标:

1.定义核心和放置的行结构

2.定义信号,PG,corner pad的位置

3.插入filler pad cell

4.手动放置macro

5.应用宏放置约束

6.使用虚拟平面放置(VF)放置宏和标准单元

7.分析拥塞

8.在macro周围创建PG ring

9.使用PNS(power network synthesis)完成P/G ring和straps

10.使用PNA(power network Analysis)分析IR drop

11.分析时序

导入:本实验的目的是让你对ICC的设计规划功能更加熟悉。对于这个实验,将使用一个稍大一点的ORCA版本,他是处于芯片级,包括IO pad以及更加宏单元。这使得设计阶段阶段更加有趣。

答案和解决方案:

本实验后有一个“答案/解决方案”部分。鼓励经常参阅此部分,验证答案,或在执行某些步骤时获得帮助。

相关文件和目录:

此实验的所有文件位于目录下的lab2_dp目录中

lab2/dp

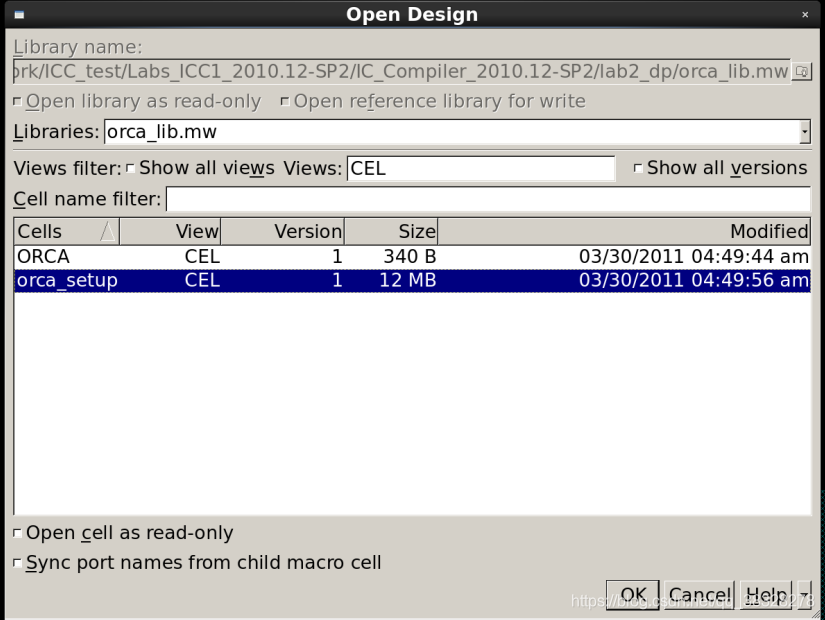

orca_lib.mw/CEL

orca_setup:数据设置后的ORCA设计,并以MIlkyWay的格式保存。

design_data/ 包含ORCA设计输入数据

ORCA_2.v 第二次通过verilog网表

ORCA_2.sdc 第二次通过sdc时序约束

scripts/ 包含各种各样的布图规划脚本

zns_pass_setup.tcl 执行第二遍数据设置脚本

connect_pg.tcl 以逻辑方式将所有pg pin连接到网络

insert_pad_filler.tcl 插入pad填充单元

keepout.tcl 禁止放置所有的宏

macro_place_cons.tcl 宏放置约束

macro_pg_ring.tcl 宏组周围创建pg ring

opt_ctrl.tcl 时序和优化控制

pad_cell_cons.tcl 定义pad单元位置

pns.tcl 电源网络约束/综合

prepare_macros.tcl 将三个宏连接到IO pad

如果遇到问题或者卡住了,可以使用完整的命令脚本去恢复

.solution/run.tcl

Task1 载入设计

1.切换到lab2_dp目录,启用ICC GUI模式

cd lab2_dp

icc_shell -gui

2.打开orca_lib.mw设计库中的orca_setup单元

Note:这个单元已经通过“data_setup”

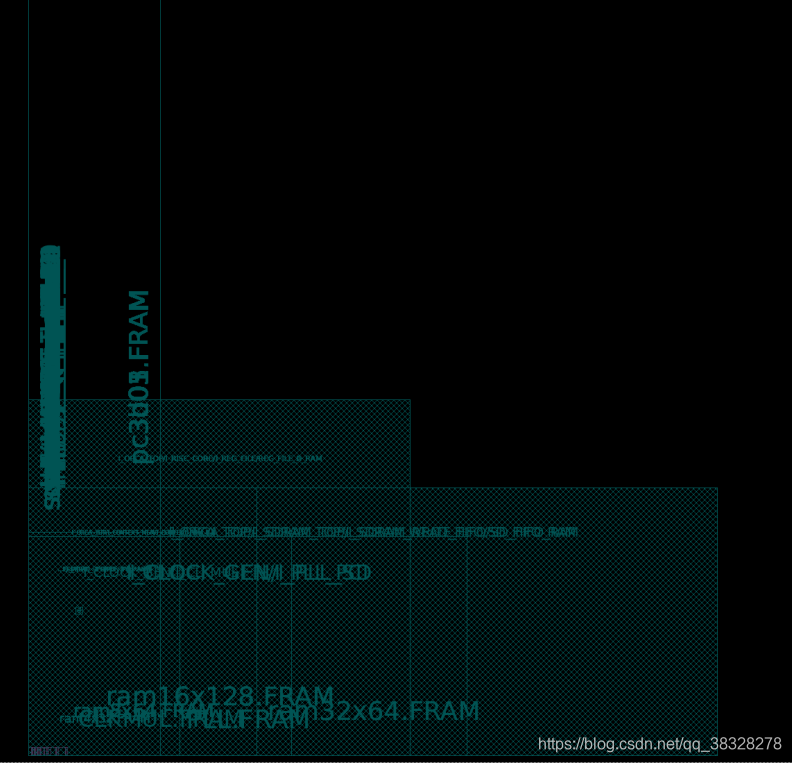

3.查看layout 窗口,大的蓝绿色矩形是宏和IO pad单元,左小角的小紫色矩形是标准单元(先看的更清楚可以放大)。所有的这些单元都是网表中实例单元。堆叠在原点(0,0)。

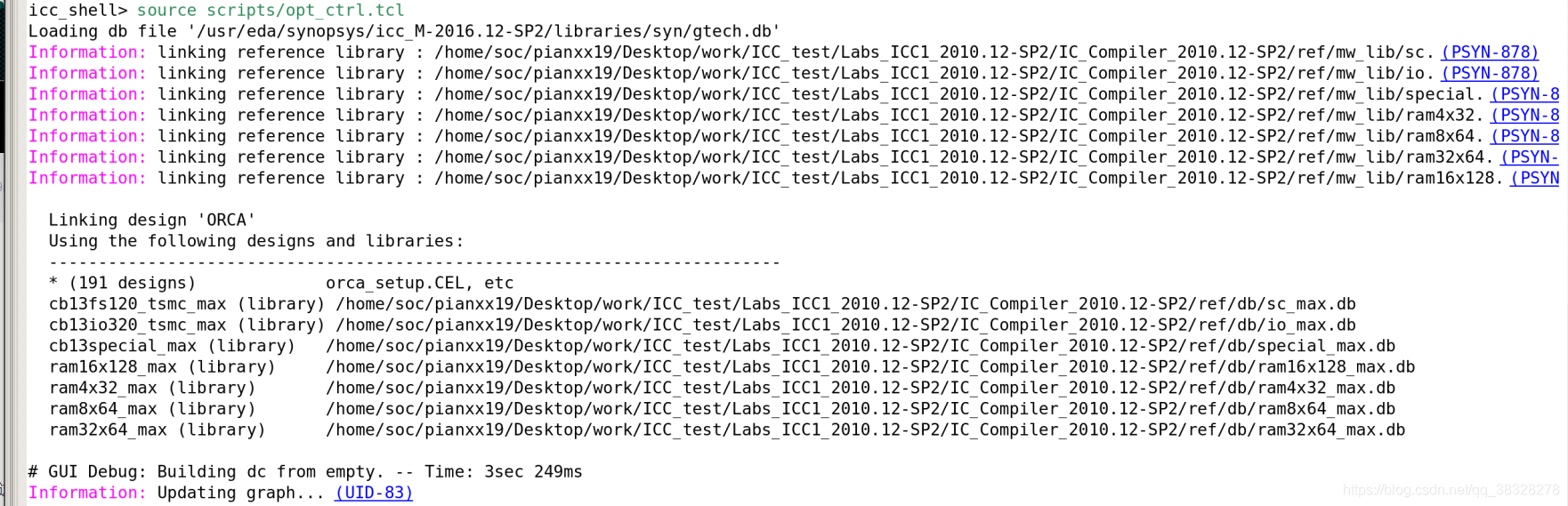

4.应用在./scripts/opt_ctrl.tcl的时序和优化控制

Note:大多数设置都在单元1附录被讨论,有些在后面单元被讨论。不需要花时间理解。

source scripts/opt_ctrl.tcl

5.通过选择以下选项切换到layout窗口中“Design Planning”任务菜单

File —> Task —> Design Planning

Task2 初始布局规划

1.来自综合的网表不包含物理单元,例如电源和地的pad cell或者corner pad cell。因此必须先创建这些额外的单元,然后才能将他们实际位置放在芯片外围区域。

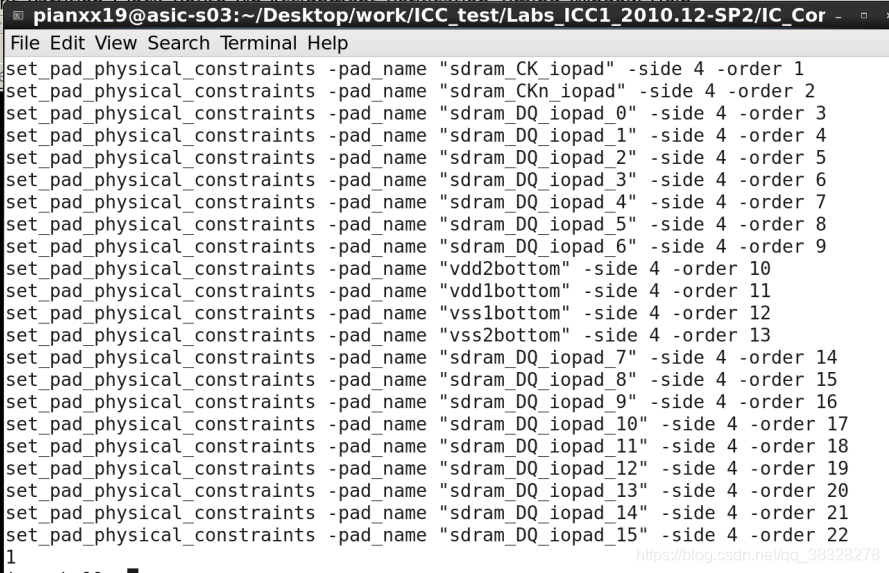

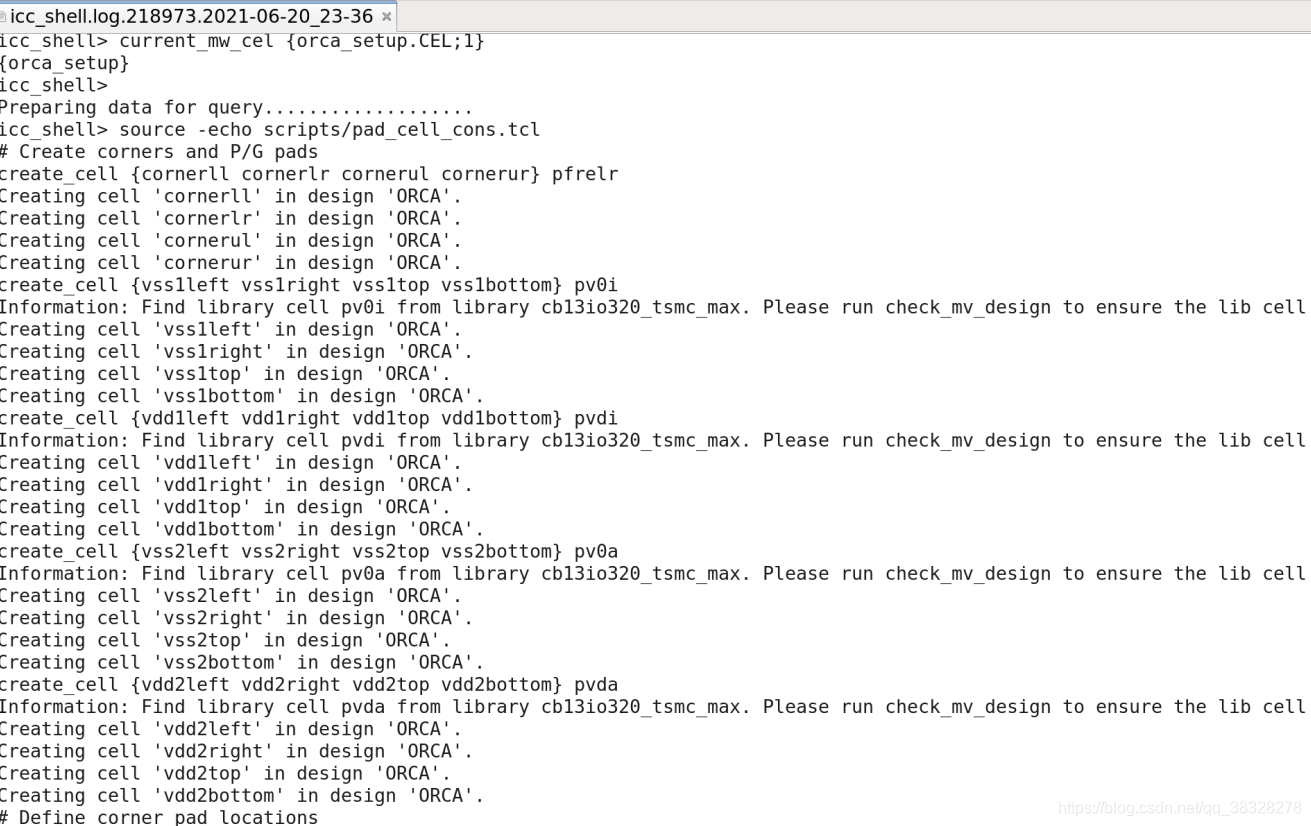

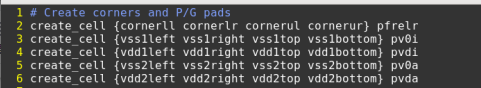

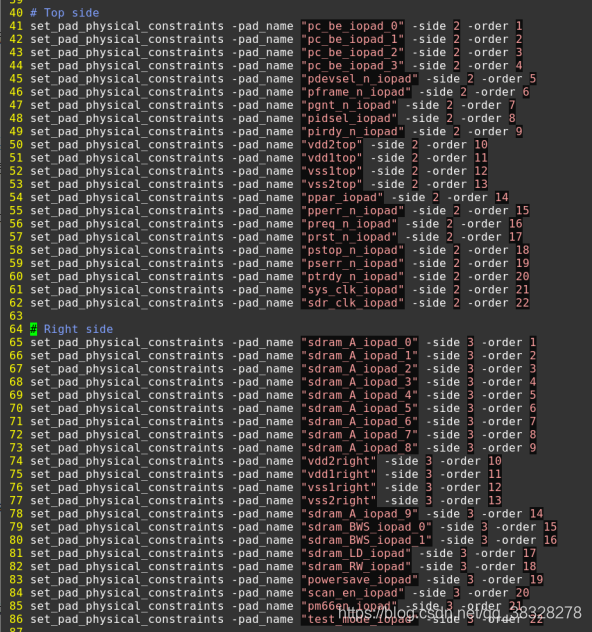

创建corner cell和pg cell,并且使用一个提供的脚本定义所有pad cell的位置:

提示:键入时,使用[Tab]键完成命令/选项/文件

source -echo scripts/pad_cell_cons.tcl

查看日志(log文件)输出,以验证这些单元是否已创建并受到约束。没有任何错误或者警告信息。

在一个单独的UNIX窗口中,查看上面的脚本回答以下问题。

问题1:使用参考单元pvdi创建一个名为VDD_TEST的pad cell

回答:

问题2:哪个边用于定义右上角corner cell的位置

回答:

2.初始化布局规划

菜单选择 Floorplan —> Initialize Floorplan

将核心利用率改为0.8(80%)

将核到左,右,底,上距离设置成30

点击OK

本文详细介绍了ICC设计规划实验的LAB2,涵盖了从初始布局规划到时序分析的全过程,包括宏和标准单元的放置、电源网络综合(PNS)、时序检查等关键步骤,旨在熟悉ICC的设计规划功能。

本文详细介绍了ICC设计规划实验的LAB2,涵盖了从初始布局规划到时序分析的全过程,包括宏和标准单元的放置、电源网络综合(PNS)、时序检查等关键步骤,旨在熟悉ICC的设计规划功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?