Fout=(Fclk*B)/2^N。

Fclk越大,Fout(max)越大。在DAC允许的范围内,尽可能去提高Fclk的值。

将Fclk提高到125M。

从硬件角度,开发板只有一个50MHz的有源晶振。

使用Verilog的方法从50MHz得到125MHz的时钟 信号是不可能的。FPGA内部逻辑是没办法得到这样一个时钟的,没办法把我们的低频率时钟往高频率时钟去变化。使用Verilog逻辑是做不到的,即使你能做到,得到的时钟质量也很差,根本就没法用。即使某些人利用网上某些资源确实实现了倍频操作,但它是利用了FPGA内部的一些延时,门级延迟等方法得到的。得到这样的时钟质量很差,拿来作为我们DDS对于时钟精读很高的应用里面是不可行的。

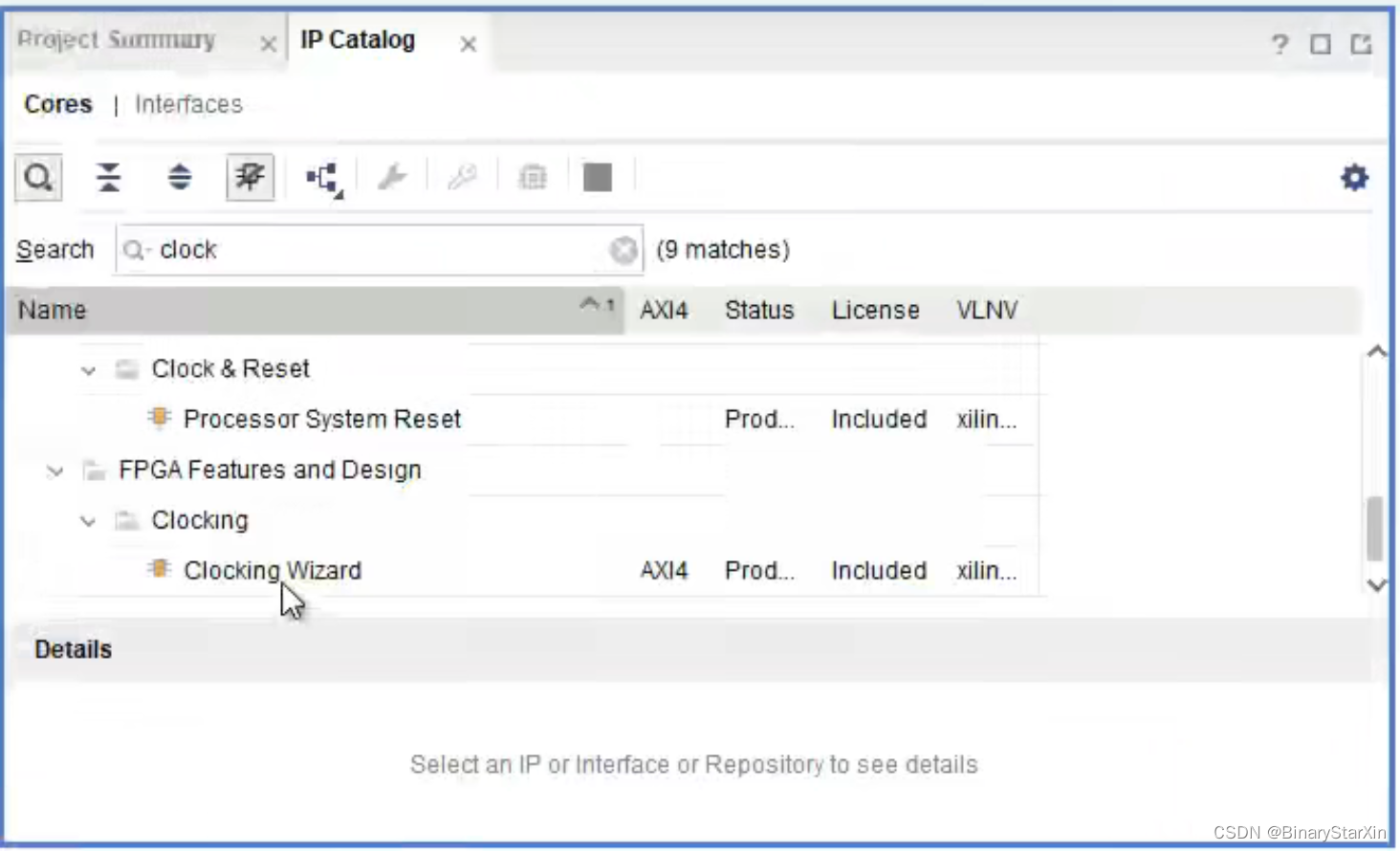

使用FPGA 内部的专用电路--锁相环来实现

时钟管理器:

功能:通过GUI的界面形式,帮助用户来创建自己的时钟网络,能够基于一个输入时钟源(晶振),进行分频倍频,得到其他频率、相位、占空比的时钟信号。这个时钟管理器根据用户的设置参数,去生成配置FPGA内部的时钟管理硬件资源。

50MHz与125MHz的最小公倍数是250MHz,50*5=250,(5倍频)250/2=125(2分频)

订阅专栏 解锁全文

订阅专栏 解锁全文

2627

2627

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?