目录

功能

支持的功能

- ID、数据和地址位宽可定制

- 支持地址空间的仲裁索引

- 支持跨时钟域转换

- 支持数据位宽转换

- axi_interconnect.v 模块支持软件生成的配置

缺陷

- 当前版本不支持乱序突发。

- 诸如缓存、锁定和服务质量(QoS)等辅助控制信号不支持对每个接口进行独立配置。

实现方案

使用方法

axi_interconnect 模块原理框图

┌───────────────┐

│ │

┌───────┐ │ AXI4 │ ┌───────┐

SAXI4_IN0──────►│Clock │──►│ Crossbar │──►│Data │──────►MAXI4_OUT0

│Conv(○)│ │ (路由核心) │ │Conv(○)│

└───────┘ │ │ └───────┘

│ │

┌───────┐ │ │ ┌───────┐

SAXI4_IN1──────►│Data │──►│ │──►│Clock │──────►MAXI4_OUT1

│Conv(○)│ │ │ │Conv(○)│

└───────┘ └───────────────┘ └───────┘

▲ ▲

┌───────┐ │ │ ┌───────┐

SAXI4_INn──────►│ │───┘ └───│ │──────►MAXI4_OUTm

│(可选) │ │(可选) │

└───────┘ └───────┘

axi_interconnect_crossbar_switch 模块原理框图

axi_interconnect_crossbar_switch

┌─────────┐ ┌─────────────┐ ┌────────────┐ ┌─────────┐

│ NUM_SLAVE│ │ sreq_arbit │ │ mreq_split │ │ NUM_MASTER

│ Slaves ├─────►│ (多到一仲裁) ├──────►│ (一到多解码)├───────►│ Masters │

└─────────┘ └─────────────┘ └──────┬──────┘ └─────────┘

│

▼ 状态记录

┌───────────────────┐

│ 事务ID映射表 │

│ (req_wren/req_id) │

└───────────────────┘

[响应通道] (Master→Slave方向)

┌─────────┐ ┌─────────────┐ ┌────────────┐ ┌─────────┐

│ NUM_MASTER│ │ mresp_arbit │ │ sresp_split│ │ NUM_SLAVE

│ Masters ├─────►│ (多到一仲裁) ├──────►│ (一到多路由)├───────►│ Slaves │

└─────────┘ └──────┬──────┘ └────────────┘ └─────────┘

▲

│

┌─────┴─────┐

│ 状态查询 │

│ (req_id) │

└───────────┘

使用方法

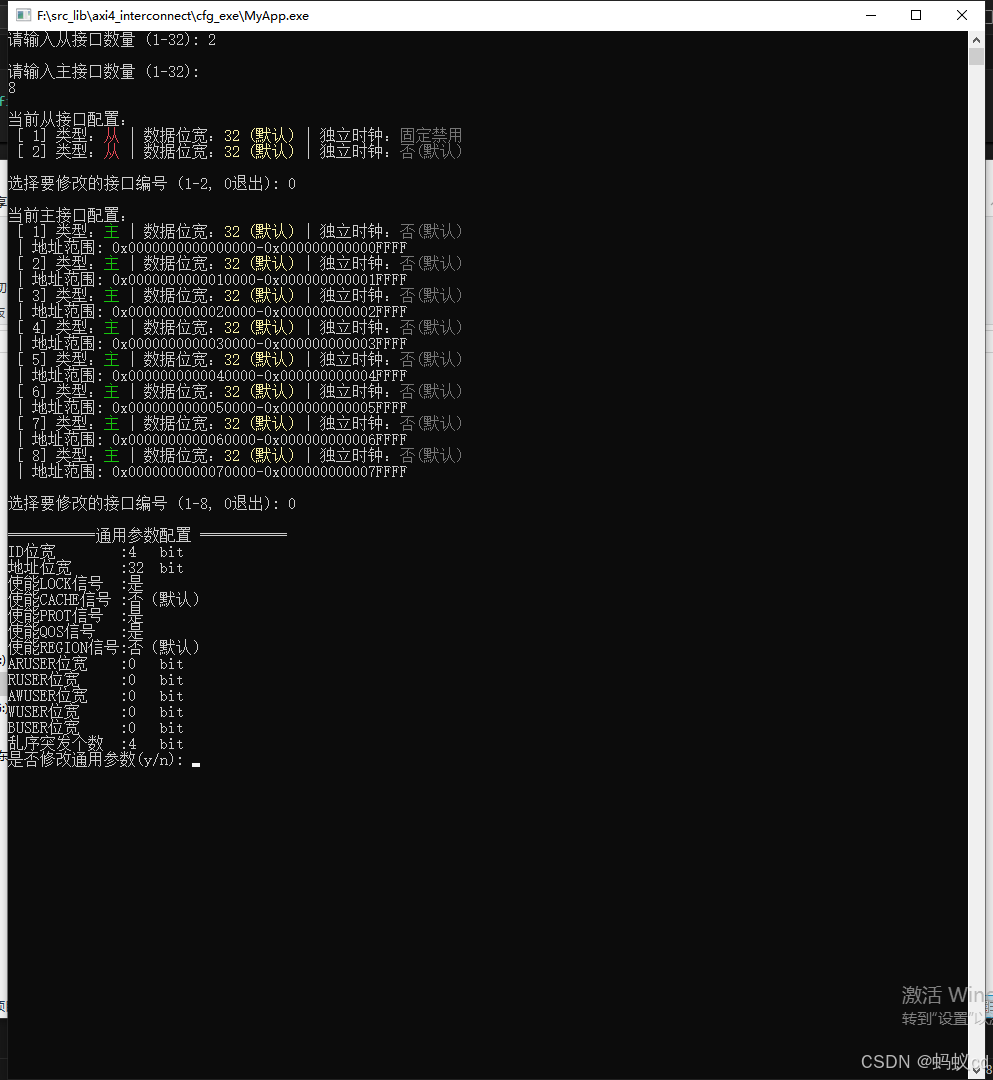

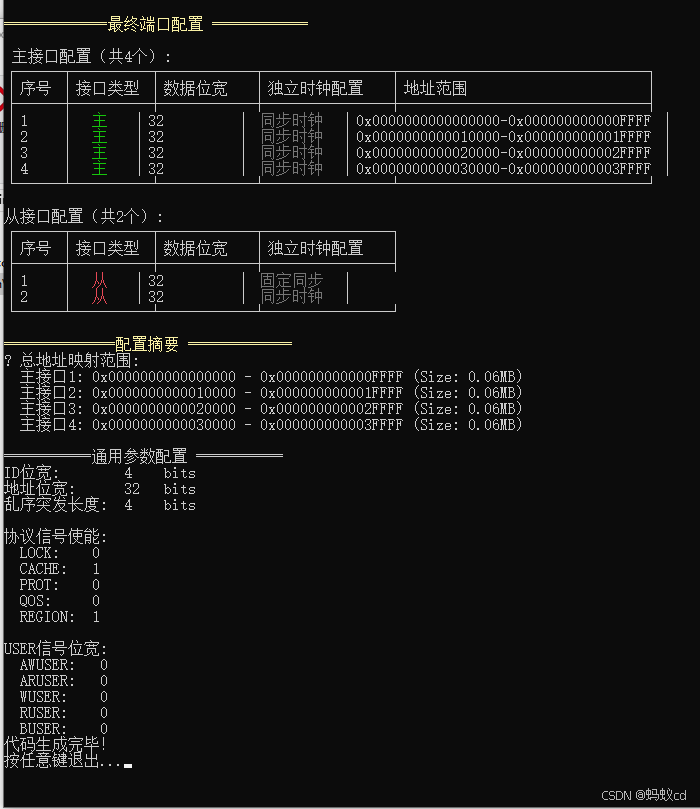

顶层模块名为axi_interconnect.v ,该模块可通过CodeGenV1_0.exe小工具生成。

生成步骤如下:

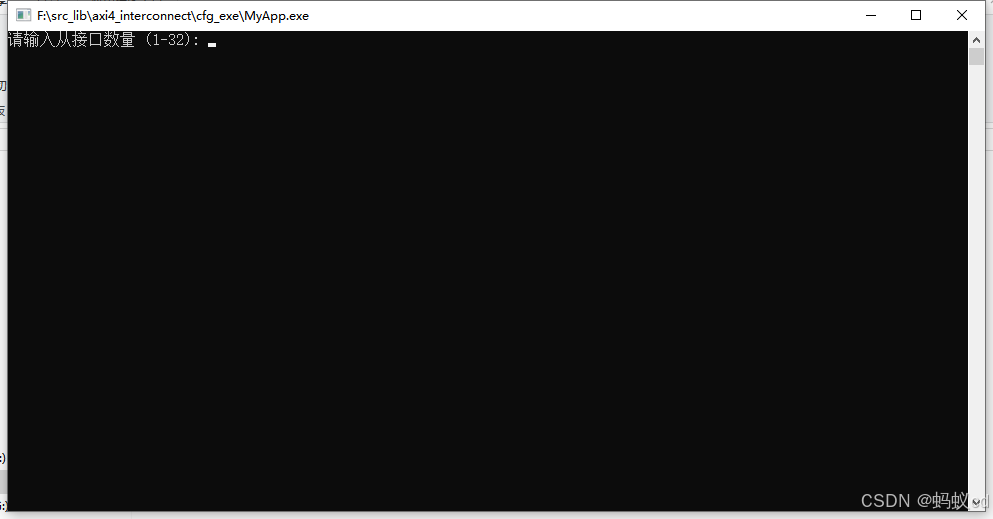

配置从机接口数量

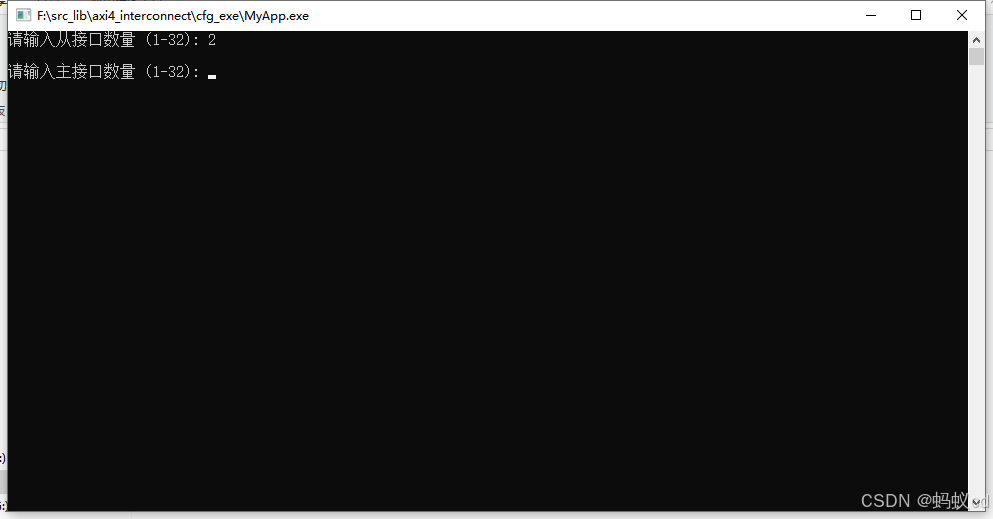

配置主机接口数量

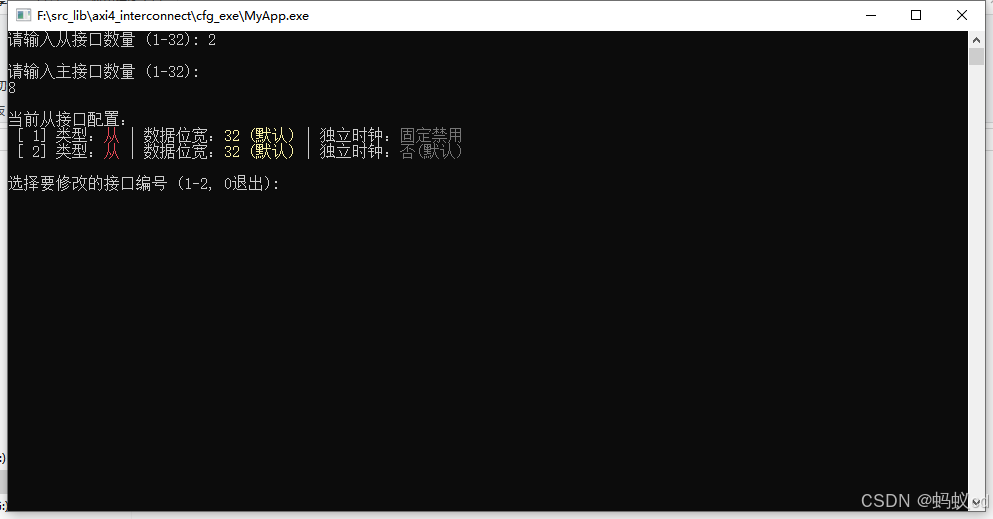

配置从机接口位宽及时钟域

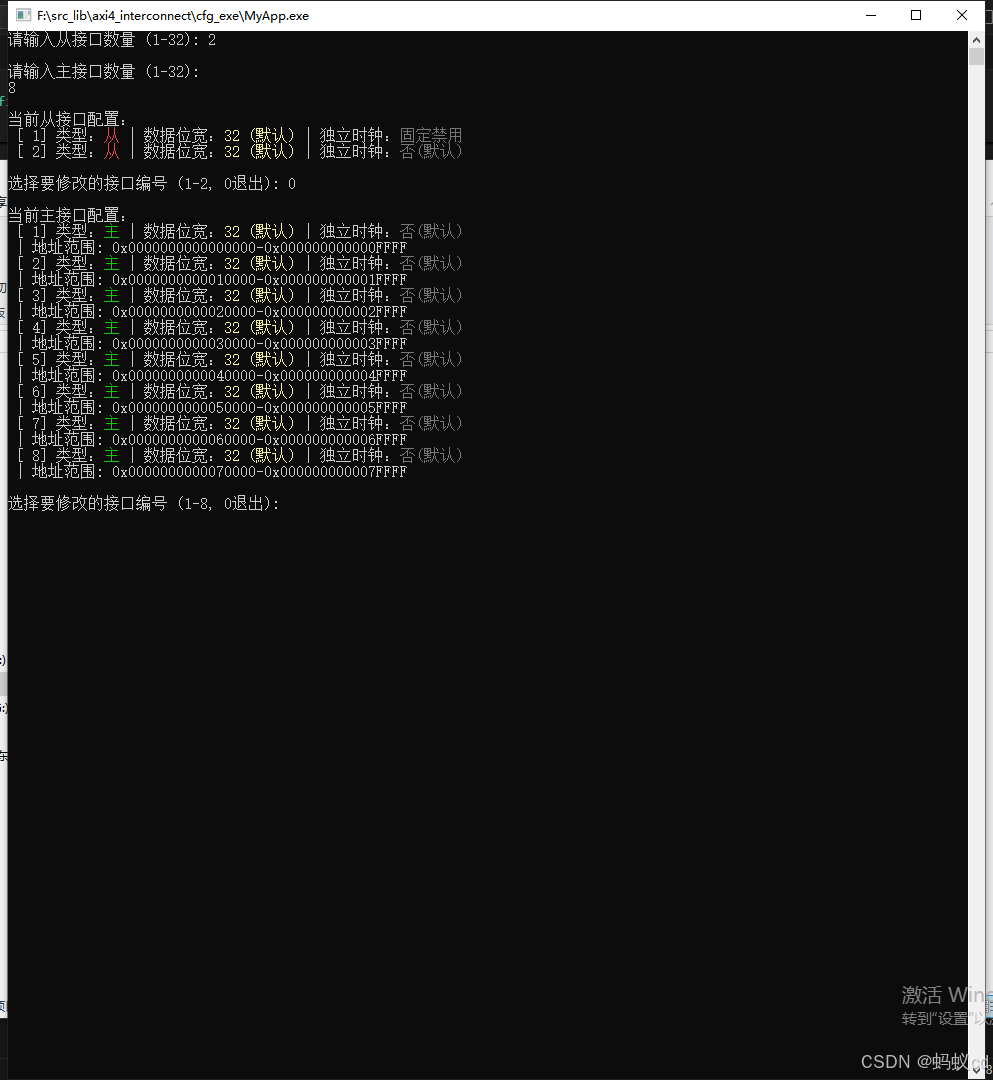

配置主机接口位宽及时钟域

配置地址位宽及其他辅助控制信号

配置完成效果

最终会在CodeGenV1_0.exe所在目录生成axi_interconnect.v模块

验证

功能仿真

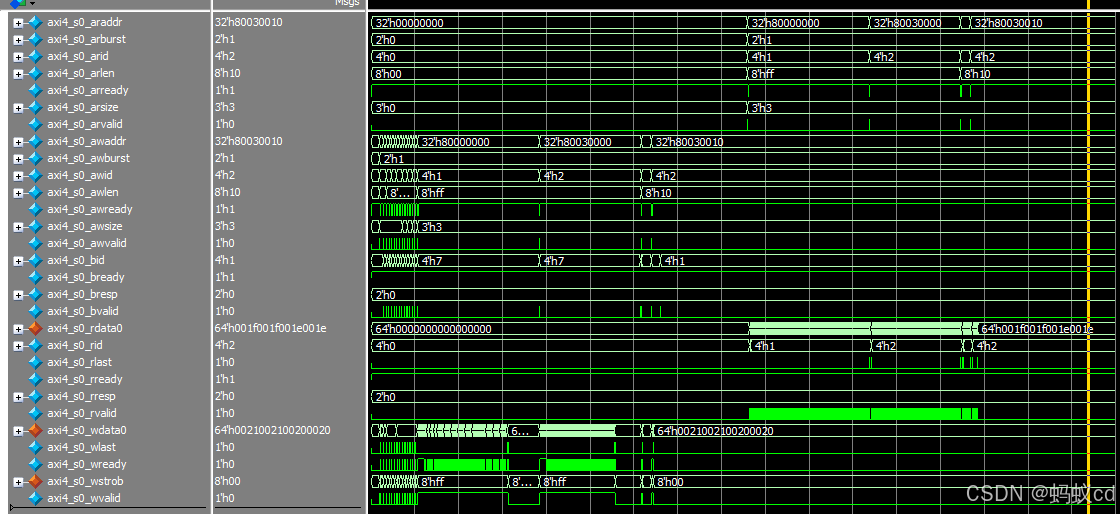

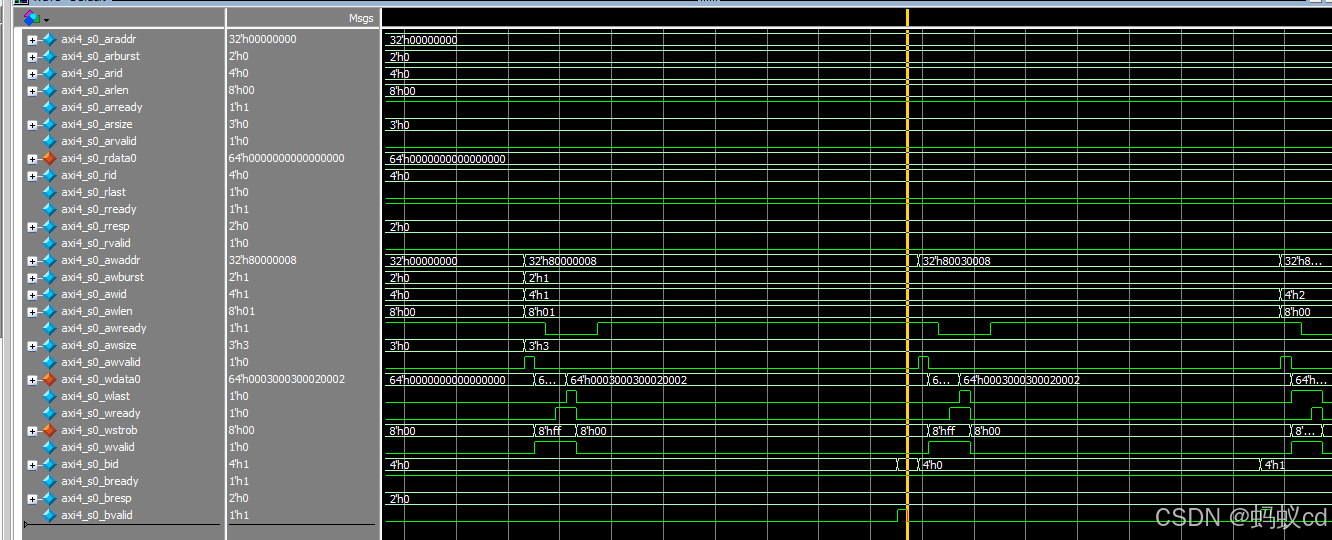

目前完成1从4主和2主4从两种情况的功能仿真。

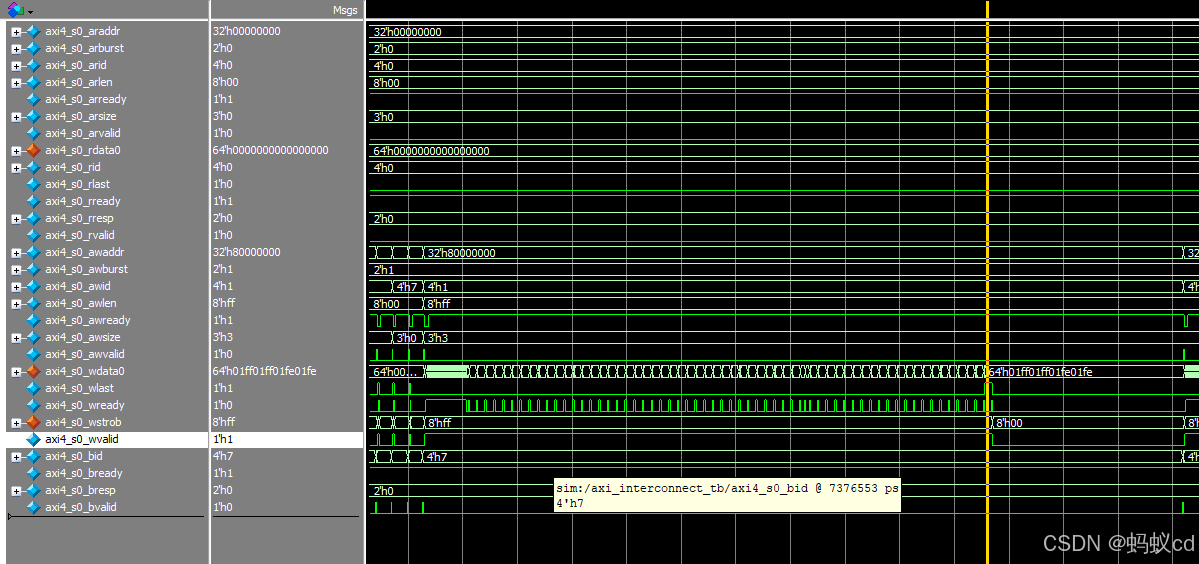

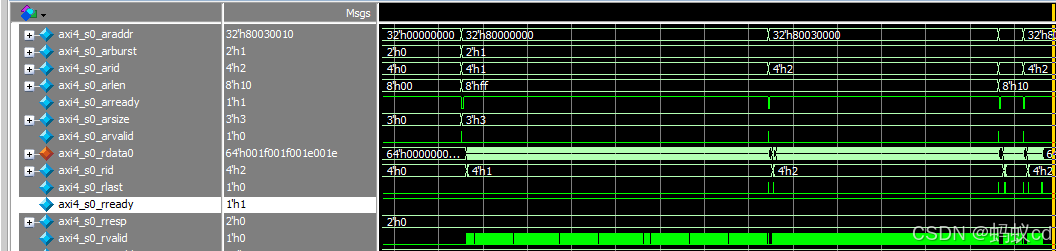

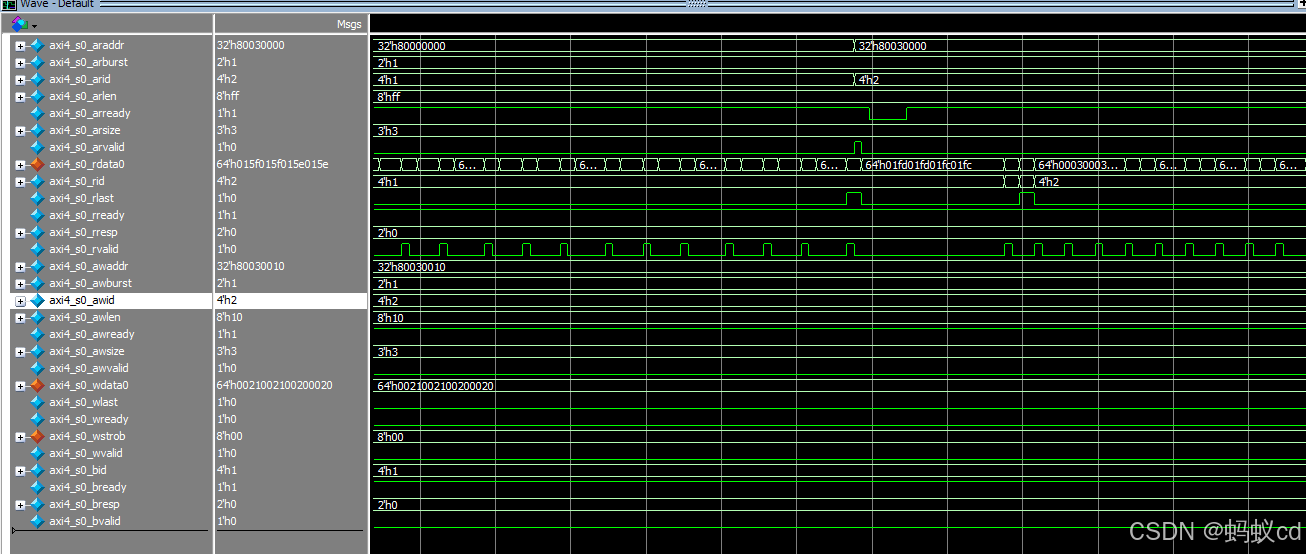

下面的仿真结果是1主(64bit),4从(32bit/32bit独立时钟/128bit/128bit独立时钟)部分读写结果

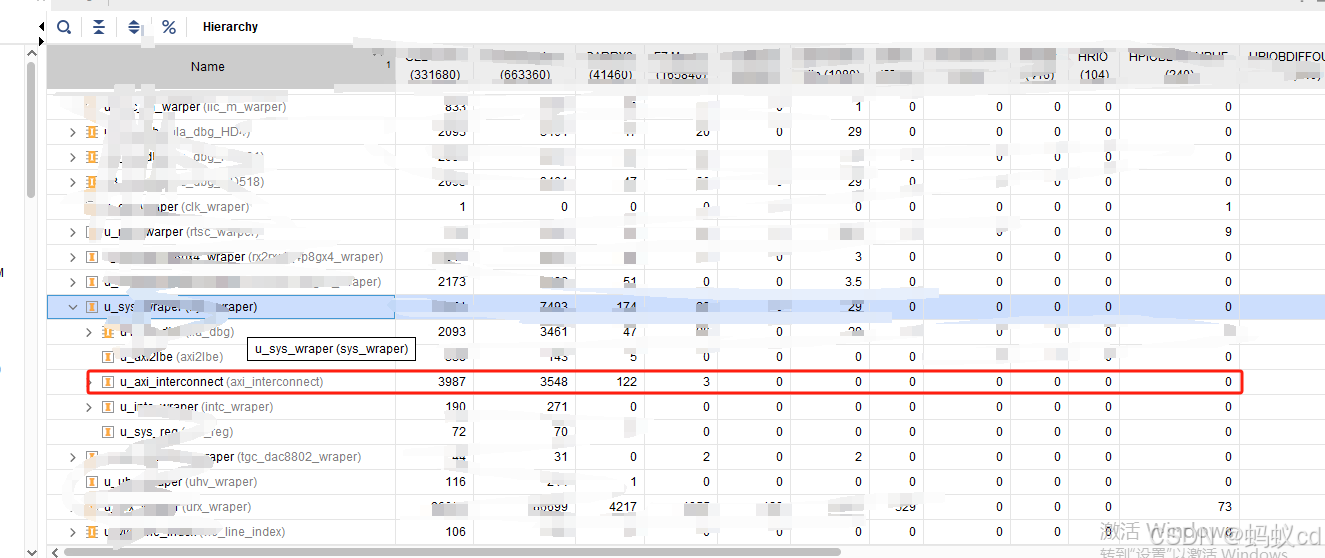

上机验证

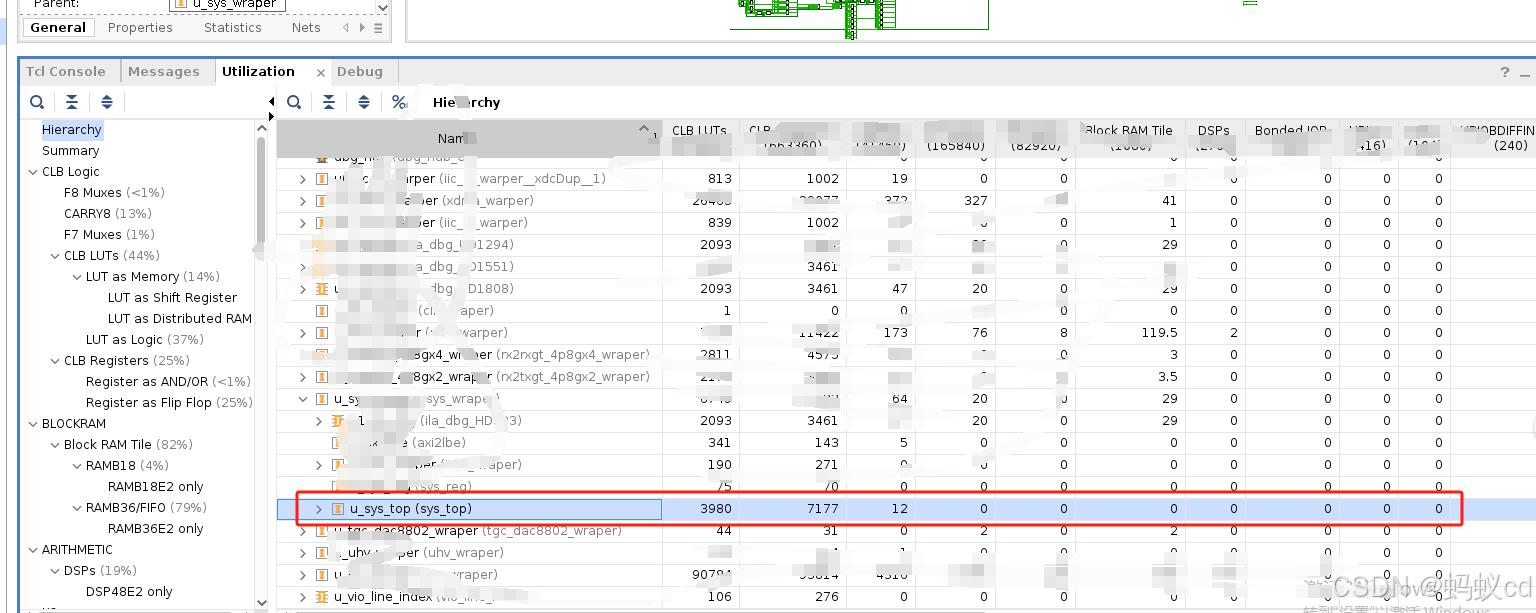

在现有项目上采用1主4从,替换掉Xilinx的IP文件,功能正常运行。

下面是资源对比:

xilinx IP核版本

源码版本

5933

5933

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?