参考文章链接:https://www.mianbaoban.cn/blog/452191-407048.html

在有些项目设计中,为了方便,将外部时钟信号不加处理直接引入FPGA芯片使用,有时候会导致意想不到的BUG发生,而且这种BUG是不可重复的。

将外部时钟直接连接到FPGA芯片的普通I/O管脚,而非专用时钟输入管脚,将会导致下面问题:

1.由于该时钟信号是通过各种长短布线资源,甚至经过LUT连接才能到达其驱动的各个寄存器,因此该时钟信号从进入FPGA管脚,到传递到各个寄存器的时钟输入端,其时间是很难保持相同的,距离的远近直接决定了该时钟信号的传输延迟(时钟延迟)。而这个传输延迟的差值,可能达到几纳秒甚至十几纳秒。这个差值,将直接影响数据的建立和保持时间,造成时序无法收敛,从而导致设计失败。

2.使用非全局布线资源,时钟信号在布线的过程中更容易受到周围信号的干扰。导致时钟质量变差。什么意思呢?打个比方,一只小鸟和一只兔子共同穿越一个满是灰尘的工地。工地上到处都是灰尘。小鸟从空中飞过,不直接与灰尘接触,因此基本不会沾到灰尘,因为它有自己独立的路线和空间。而兔子因为不会飞,因此只能跑着从工地中穿过,那么,不可避免的,兔子的脚上会沾上灰尘。导致当兔子穿过这个工地的时候,早已由小白兔变成了小灰兔。时钟信号也是如此,全局时钟资源有专门的时钟路径,在自己的空间走线,不穿过或很少穿过各种高速翻转的逻辑区域,因此很少受到污染。而非全局时钟资源没有专门的时钟路径,只能使用通用布线资源,而这些布线不可避免的会穿过很多高速翻转的逻辑区域。从而受到这些逻辑的翻转噪声的污染。最终时钟信号变的很差。例如边沿上升和下降更慢,占空比发生变化,时钟抖动增大等。

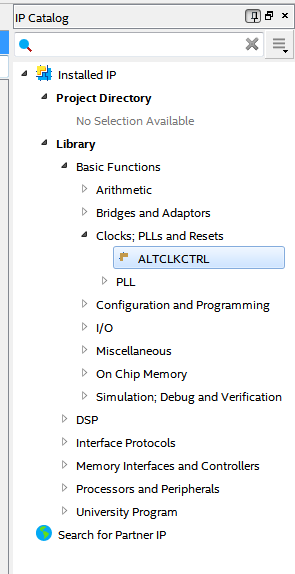

要想解决该问题,可以将普通I/O输入的外部时钟连接到全局时钟资源。具体做法是调用ALTCLKCTRL的IP核。如下图所示

1563

1563

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?