1.时钟信号的分类

1.1 外部时钟

外部时钟,即时钟来自FPGA外部。通常外部时钟源对FPGA设计来说是必须的,因为一般FPGA芯片内部没有能够产生时钟信号的选频和激励电路。因此,通常FPGA芯片都需要外部晶振以及电阻、电容、电感、三极管等器件,用于搭建产生时钟信号的电路。

另外,当用示波器观察外部时钟信号时,会发现波形是一个正弦波,不过模拟的时钟信号经逻辑门的驱动后,由于MOS电路的陡峭导通特性,会对时钟信号的边沿起到积极的缩减作用。

1.2 内部时钟

再生时钟:FPGA芯片内部通过输入时钟信号作为参考,再次基础上通过调整频率和相位产生的新时钟。目前FPGA中只有DCM和PLL能够产生再生时钟。

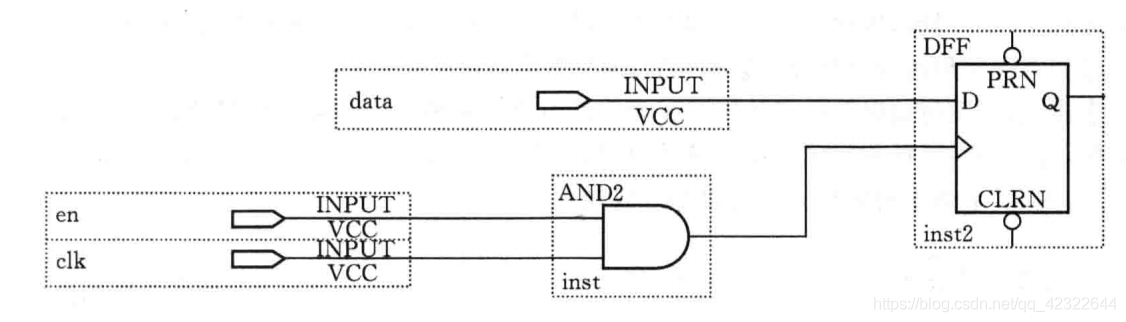

门控时钟:在外部输入时钟的基础上,由组合逻辑产生的时钟叫门控时钟。通常情况下,由于组合逻辑产生的竞争冒险现象,而寄存器对时钟边沿非常敏感,因此不建议使用门控时钟。

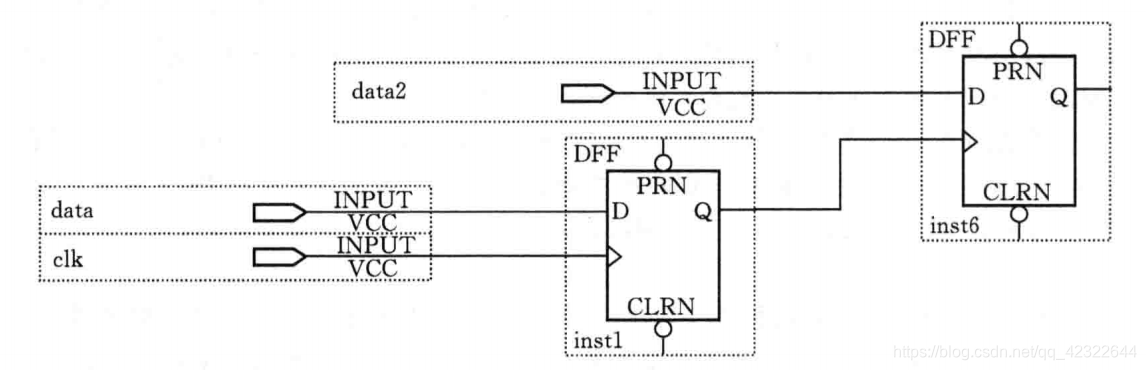

行波时钟:在外部输入时钟的基础上,由时序逻辑产生的时钟叫行波时钟。

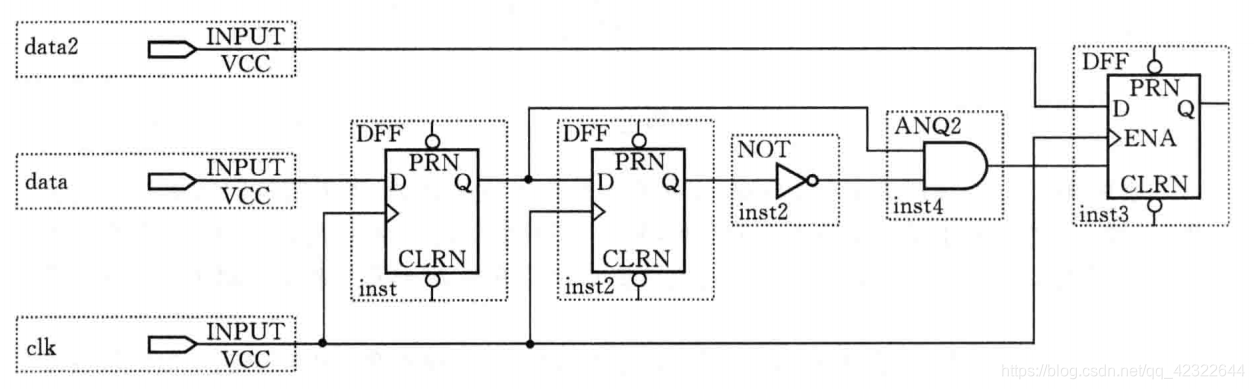

通常不建议使用行波时钟,因为会引入新的时钟域,增加时序分析难度。当需要为后续电路进行降频时,可采用控制后续电路使能端实现。如下图所示

2.时钟域

2.1 概念

时钟域即时钟信道的驱动范围。一个时钟域中只能存在一个时钟信号,但一个信号可以对应两个时钟域,即适中的上升沿和下降沿。

寄存器时钟域判断方法:看其输入时钟是哪个时钟信号的哪个边沿即可。

组合逻辑时钟域判断方法:如果一个组合逻辑的所有输入都来自同一个时钟域的寄存器的输出,那么该组合逻辑的输出变化必然随着该时钟跳动,所以该组合逻辑属于这个时钟域。

2.2 时钟树简介

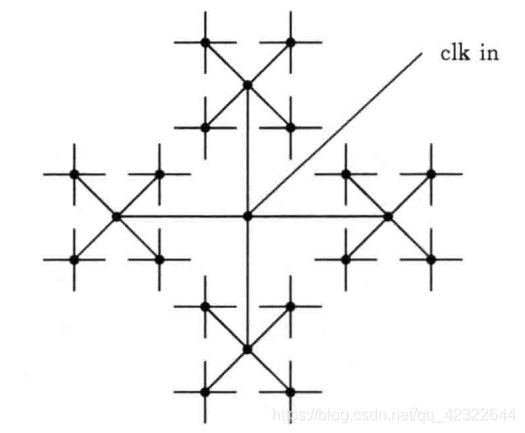

时钟树为大范围的时钟域提供时钟连接,这就需要时钟树有强大的扇出能力,同时保证时钟到达不同除法器时间差尽可能小。为了达到这两点要求,时钟树采用如下结构实现。

时钟信号由中间树根引入时钟树,并由不用级缓存扇出分别送往不同区域,如此往复,之道时钟信号达到触发器资源。由此可见,时钟树主要利用多级扇出来达到高扇出要求;通过每级扇出后的布线长度尽量保持一致来保证时钟尽可能同时达到各个触发器。

注意,如果两个时钟域分别对应一个时钟信号的上升沿和下降沿,则他们可以公用一个时钟。

注意,时钟树是为了保证时钟域不同触发器的始终到达时间尽可能一直,并不保证时钟信号到达触发器所消耗时间尽可能小。

2.3 时钟树分类

全局时钟网络资源:覆盖整个FPGA,可以保证时钟信号到FPGA上任意两个地方的延迟时间偏差最小。一般来说,全局时钟网络资源比较珍贵,使用时需要节省。

区域时钟网络资源:每个FPGA区域都有若干属于自己的区域时钟网络,可以覆盖的范围是整个区域甚至包括与本区域相邻的区域(一般来说,一个FPGA区域只包括一个IO bank)。区域时钟网络资源可以保证时钟信号到FPGA上该区域任意两个地方的延迟时间偏差最小。

IO时钟网络资源:前面所述网络资源针对的主要是FPGA的内部资源,而对于接口资源,则有专门的IO时钟网络资源来完成时钟信号承载工作。原因有三:第一,接口资源中的寄存器数量较少,不需要大型树状时钟网络来减少延迟差。第二,内部时钟网络资源由于规模大,范围广,往往不能承载频率太高的信号,而一些通信接口的时钟速率很高,远超出内部始终网络资源承受范围,因此需要专有的IO时钟网络资源。第三,高速接口逻辑一般有专用的接口资源,布局布线已固定,能够保证外部信号到达寄存器的延迟最短,对了配合达到高速信号传输,必须要求时钟信号所走路径最短,内部始终资源不合要求,因此只能用专有的IO时钟网络资源。

2.4 时钟树的正确使用

2.4.1 什么情况下应当使用时钟树

如果时钟用来驱动FPGA内部逻辑资源,则建议时钟上树;如果时钟信号时钟域太小,则不利用触发器也可能可以通过时序分析,但仍然建议使用时钟树。如果只有一个触发器,则没有所谓时钟差,也不需要上树。如果时钟信号仅仅为了为FPGA外围硬件提供时钟激励,则无需使用时钟树,因为时钟树无法延申到FPGA外部。

2.4.2 如何选择时钟树

区域大就选全局时钟树,区域小就选区域时钟树,区域特别小就选IO时钟树,这种思路是完全错误的。

IO时钟树:只分布在接口资源中,FPGA内部资源无法使用该时钟树。

全局时钟树:覆盖范围广但数量有限,尽量充分使用。

区域时钟树:优先使用全局时钟树,全局时钟树不够时与区域时钟树配合使用。使用区域时钟树可以让资源的分布在物理上更加紧凑,同时有些功能要求必须使用区域时钟树和IO时钟树配合完成。

2.4.3 如何使用时钟树

2.4.3.1 全局时钟资源

一,通过正确的物理连接

如果时钟信号是FPGA外部产生的,则只需要将时钟信号连接到专门为全局时钟设计的管脚即可。这些特定管脚也可以接入普通信号,FPGA会对接入信号进行分析,此时不会为其分配时钟域资源。

二,通过恰当的代码描述

当时钟信号没有通过正确管脚引入FPGA,或者时钟由FPGA内部产生,则需要用原语。

BUFG onTree(.O(globalClk), .I(innerClk));

2.4.3.1 区域时钟树、IO时钟树

与全局时钟类似,FPGA也有专门为区域时钟和IO时钟设计的专用管脚,但是仅仅连接在这些管脚不一定能完成相应时钟树的应用,必须在代码中用原语描述才可以。例如BUFIO分配IO时钟树,BUFR分配区域时钟树。

2.4.4 被“拉下树”的信号

时钟树仅能提供对时钟信号的传递作用。因此,凡是对时钟树上的时钟信号进行任何的逻辑操作,生成新的信号,那么新的信号就不在时钟树上了(原始时钟信号仍在树上)。如果希望新的信号作为时钟驱动一些逻辑,则必须重新调用原语让新的信号上树。

3.DCM与PLL

3.1 PLL

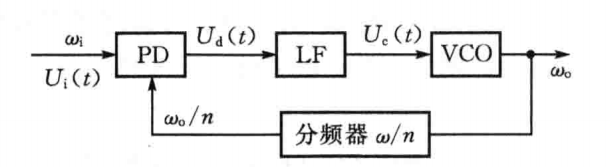

锁相环,PLL包含了模拟电路部分。基本原理如下:

PLL只有一个输出端口,但是可以通过外接分频器和移相器实现多路输出,因此PLL的输出往往是受限的、相关的。

3.2 DCM

DCM为纯数字电路。

3.3 应用

待完成

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?