本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

7.8 设计规则检查

STA中两个常用的设计规则是最大过渡时间-max_transition和最大电容-max_capacitance。这些规则将会检查设计中的所有端口和引脚是否满足过渡时间和电容的规定约束。这些规则可以使用以下命令指定:

-

set_max_transition

-

set_max_capacitance

作为STA的一部分,任何设计规则的违例(violation)均以裕量(slack)的形式报告。以下是些例子:

-

set_max_transition 0.6 IOBANK

-

set_max_capacitance 0.5 [current_design]

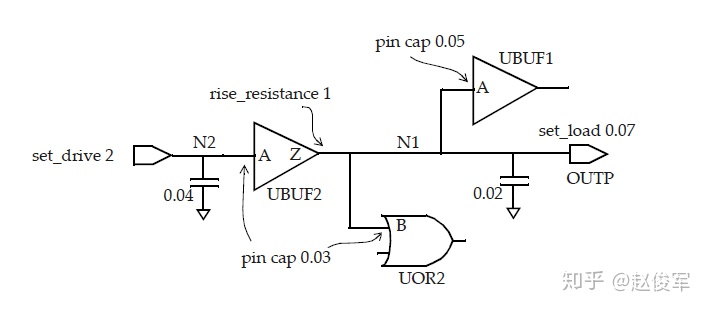

网络上的电容是通过将所有引脚电容加上任何IO负载再加上网络上的任何互连电容的总和计算得出的。下图7-32为一个示例:

- 网络N1的总电容 = UBUF1的A引脚电容 + UOR2的B引脚电容 + OUTP的输出负载电容 + 走线互连电容

= 0.05 + 0.03 + 0.07 + 0.02 = 0.17 pF

- 网络N2的总电容 = UBUF2的A引脚电容 + 走线互连电容

= 0.03 + 0.04 = 0.07 pF

过渡时间是延迟计算的一部分。对于图7-32中的示例(假设UBUF2单元使用线性延迟模型):

-

UBUF2的A引脚过渡时间 = 2 * 网络N2的总电容 = 2 * 0.07 = 0.14ns = 140ps

-

输出端口OUTP过渡时间 = UBUF2的Z引脚的驱动电阻 * 网络N1的总电容

= 1 * 0.17 = 0.17ns = 170ps

还可以为设计指定其他设计规则检查,比如:set_max_fanout(指定设计中所有引脚的扇出约束),set_max_area(用于设计)。但是,这些检查适用于综合(synthesis)而非STA。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

839

839

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?