同步复位

同步复位:是指当复位信号发生变化时,并不立即生效,只有当有效时钟沿采样到已变化的复位信号后,才对所有寄存器复位。

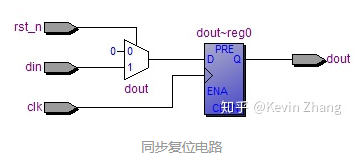

同步复位电路如下图所示:

always @(posedge clk) begin

if(!rst_n)

dout <= 0;

else

dout <= din;

end

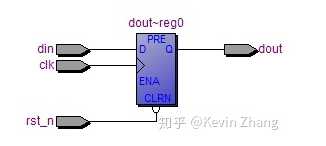

异步复位

异步复位: 无论时钟沿是否到来,只要复位信号有效,就对系统进行复位

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

dout <= 0;

else

dout <= din;

end优缺点比较

异步复位,同步释放

什么情况下要用异步复位,同步释放

为了防止复位信号在撤除时产生亚稳态事件。

1)电路目的:防止复位信号撤除时产生亚稳态事件。

2)什么是异步复位和同步释放:是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

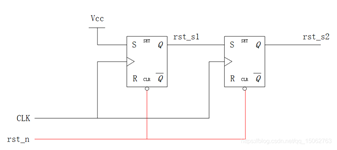

下面说明一下如何实现异步复位和同步释放的。

异步复位:显而易见,rst_async_n异步复位后,rst_sync_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号rst_async_n撤除时,由于双缓冲电路(双寄存器)的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件,但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D触发器输出高电平“1”,此时第二级触发器也会更新输出,但是输出值为前一级触发器clk来之前时的Q1输出状态。显然Q1之前为低电平,顾第二级触发器输出保持复位低电平,直到下一个clk来之后,才随着变为高电平。即同步释放。

module reset_gen ( output rst_sync_n, input clk, rst_async_n);

reg rst_s1, rst_s2;

wire rst_sync_n ;

always @ (posedge clk, posedge rst_async_n)

if (rst_async_n)

begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else

begin

rst_s1 <= 1'b1;

rst_s2 <= rst_s1;

end

assign rst_sync_n = rst_s2; //注意这里的rst_sync_n才是我们真正对系统输出的复位信号

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?