大家在进行FPGA逻辑设计时肯定经常会用到复位,学习者在入门学习时发现相关的代码实例几乎都是用的异步复位,很多学习者没有太注意这块的内容,都是直接照搬例程,也没有深究其原因,就以为异步复位就是约定成俗的习惯性写法,其实这是不对的。

为什么需要复位呢?这个很容易理解,就是让系统在复位时能够初始化后回到正常状态。我们使用的复位往往都是全局复位,复位有两种,一种是同步复位,一种是异步复位。

同步复位:是指当复位信号发生变化时,并不立即生效,只有当有效时钟沿采样到已变化的复位信号后,才对所有寄存器复位。

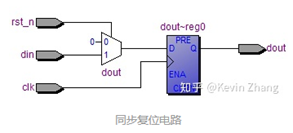

同步复位电路如下图所示:

always @(posedge clk) begin

if(!rst_n)

dout <= 0;

else

dout <= din;

end

异步复位: 无论时钟沿是否到来,只要复位信号有效,就对系统进行复位

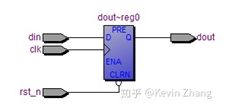

异步复位电路

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

dout <= 0;

else

dout <= din;

end我们现在对异步复位和同步复位有了一定理解后,其实这两种电路都有存在着一定的优缺点。

为了防止异步复位信号在撤除时产生亚稳态事件,出现了异步复位和同步释放电路来解决这个问题。关于为什么异步复位信号在撤除时产生亚稳态事件,可以参考下面的博客

http://www.elecfans.com/d/1231006.html

异步复位和同步释放:是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

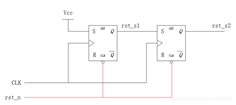

异步复位同部释放电路

reg rst_s1, rst_s2;

wire rst_sync ;

always @ (posedge clk, negedge reset_n) begin

if(!reset_n)begin

rst_s1 <= 1'b1;

rst_s2 <= 1'b1;

end

else begin

rst_s1 <= 1'b0;

rst_s2 <= rst_s1;

end

end

assign rst_sync = rst_s2; //注意这里的rst_sync才是我们真正对系统输出的复位信号

目前已经对上面的复位电路有了大概的认识,那在实际的系统中如何做复位设计呢,我们需要首先需要看我们使用的那个厂家的FPGA芯片,不同厂家的复位设计还不相同。

其中Altera器件中的基本单元就是由异步复位且低有效结构的寄存器组成的,如果不按照这个现有的资源来设计我们就需要额外使用其他的资源,从而造成浪费,所以这就是我们所“默认”Altera器件中往往都是异步复位低有效的原因。

但是在使用Xilinx的芯片时规则又变了,官方文档《Vivado使用误区与进阶》中明确说明尽量避免使用异步复位,且如果使用复位就用高复位,因为作为xilinx 7系列触发器,其 R 端口既可用作同步置位/复位端口,也可用作异步预设/清除端口,但无论哪种方式,都是高电平有效。巧的是刚好和Altera推荐的规则相反,也是因为内部结构决定的,所以我们在开发Altera和Xilinx的芯片时复位要区别对待。

在这里主要谈谈Xilinx FPGA复位如何设计,在《Vivado使用误区与进阶》中提到我们要遵循 Xilinx FPGA 建议的复位准则如下:

(1)尽量少使用复位;

(2)必须复位时采用同步复位;

(3)确保使用高电平有效的复位;

(4)避免异步复位(RAMB 和 DSP48 模块中不支持异步复位)。如果不用复位那寄存器的初值我们怎么给呢?在代码中定义寄存器的时候直接在变量名后赋初值即可,Verilog-2001标准支持这种写法。

Xilinx 的复位准则必须严格遵守,根据现场支持的经验来看,很多设计性能的瓶颈就在于设计源代码时没有考虑底层实现器件的硬件结构特点,尤其以复位信号的实现问题最为突出。

在Xilinx的官方手册UG949中也写道关于复位的问题,Xilinx器件提供专用的全局置位/复位信号(GSR)。在器件配置结束时,该信号将器件配置中所有顺序单元的初始值。如果未指定初始状态,则为顺序原语分配默认值。在大多数情况下,默认值为零。 FDSE和FDPE 原语是例外,默认为逻辑1。每个寄存器在配置结束时将处于已知状态。因此没有必要单独为初始化加电器件编写全局复位代码。

Xilinx强烈建议用户仔细判断设计何时需要复位,何时不需要复位。大多数情况下,在控制路径逻辑上可能需要复位以确保正常运行。然而在数据路径逻辑上通常不需要复位。

所以在Xilinx FPGA设计中牢记以上的四个复位准则,这样可以让你的设计达到更快的时序收敛。我们也可以通过学习官方的例子程序中的复位设计。

《Vivado使用误区与进阶》这本电子书总结了很多的FPGA设计经验和方法,这些方法也都是在大量的客户实践经验中总结的,有很好的参考建议。

下载链接如下:

链接:https://pan.baidu.com/s/1GWpu3QIuCMEREgieOm9BTw

提取码:98p4

1305

1305

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?