概述

这段时间做FPGA原型验证,发现有个复位信号经过跨片后由管脚输入到另外一片FPGA,信号经过IBUF后插入了BUFG再route到对应的寄存器。由于输入复位管脚非时钟专用管脚,导致vivado综合会报错,需要以下加额外的约束才能跑过去。之前一直以为BUFG是时钟专有布线资源,没想到复位也会走BUFG。

![]()

什么时候复位会走全局时钟网络?

高电平复位与低电平复位有何区别?

FPGA中使用复位需要注意些什么?

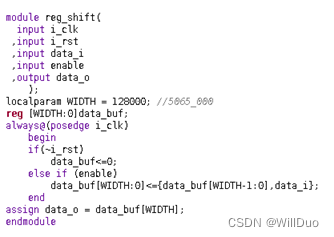

带着疑问写个简单测试用例用vivado综合验证下:

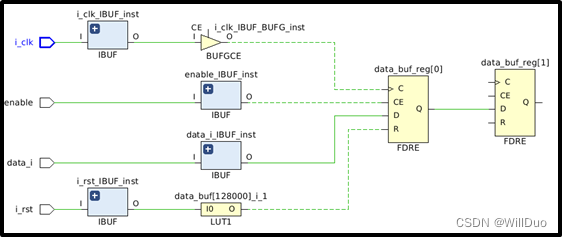

上图代码为12800位宽移位寄存器,用vivado综合synthesis后网表为下图:

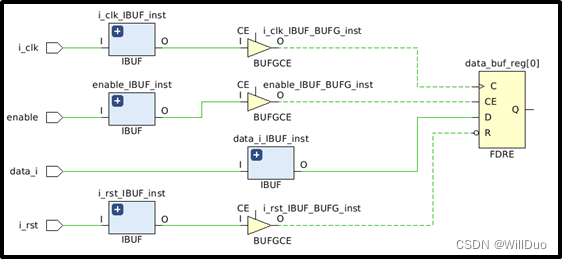

implememtation后网表

对比synthesis和implememtation网表可以看出:

- 低电平复位并不会增加额外的逻辑,而是触发器属性配置为复位低电平有效。

虽然在synthesis网表看低电平复位会增加一个lut查找表取反,但是到了implememtation阶段会优化取反的lut,把触发器属性变为低电平有效。

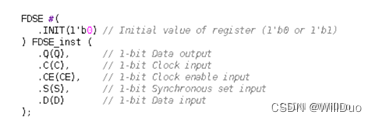

下图是xilinx ultrascale系列FPGA同步触发器例化源语,由此可见FDRE触发器可配置clk/data_in/reset输入的有效极性。当IS_R_INVERTED配置为1,表示寄存器低电平复位有效。所以ultrascale系列低电平复位不会增加额外的资源。

下图xilinx 7系列FPGA同步复位寄存器源语,没有IS_R_INVERTED配置参数,由此可见该系列存储器件不支持低电平复位,如果是低电平有效复位,会在寄存器复位前加lut实现复位反向,这种情况会增加FPGA逻辑资源消耗。

2,implememtation阶段会对高扇出信号做优化,会在CE和RESET路径上插入BUFGCE, 走全局网络route。这样可以降低route延时。

重新做个实验,当把移位寄存器位宽降低到1000时候,也就是说降低net fanout后,CE和 RESET不会在路径上插入 BUFGCE。验证之前想法。

FPGA复位总结:

- 不要异步复位,异步复位没办法优化控制集,例如把复位映射到数据路径去。除此之外xilinx FPGA Block RAM 和 DSP只支持同步复位,如果使用异步复位寄存器,则无法利用设备资源,或者这些资源的配置不够优化。

- 尽可能避免使用复位逻辑。复位逻辑会增加控制集复杂度和route复杂度,FPGA中每个寄存器在上电都有默认初始值,所以数据通路可以不需要复位。状态机寄存器等控制寄存器则必须需要复位,否则状态会乱。

- 对xilinx FPGA尽可能描述高复位,高使能,虽然对于ultrascale系列FPGA来说低复位并不会增加逻辑资源消耗,但是低复位寄存器内部会加反向逻辑影响电路性能。需要注意的是Altera FPGA寄存器用低电平复位。如果反了会则内部会加反向逻辑影响电路性能,甚至有的会在寄存器外面加lut实现反向功能,增加逻辑资源。

- 如果实在需要异步复位,一定需要则使用异步复位、同步释放的方法,并将复位信号局部化,避免高扇出。

238

238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?