文章目录

前言

锁存器和触发器是具有记忆功能的二进制存贮器件,是组成各种时序逻辑电路的基本器件之一。

一、D锁存器

1. 什么是锁存器

锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。

锁存器在不锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓存器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。因此锁存器也称为透明锁存器,指的是不锁存时输出对输入是透明的。

2. 锁存器的工作原理

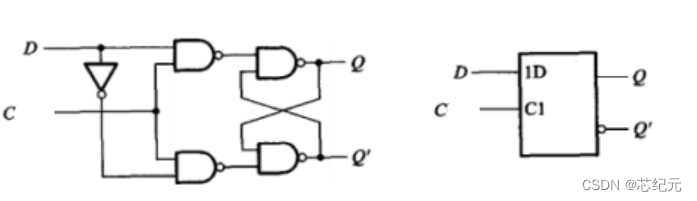

D锁存器的电路图如下图所示:

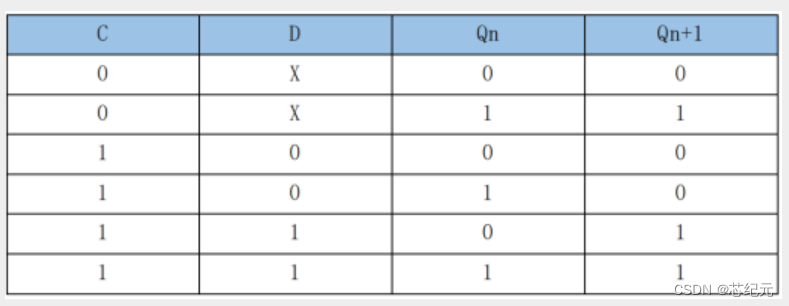

D锁存器的特性表如下所示,Qn指触发前的状态,Qn+1指触发后的状态:

当C为0时,Qn+1=Qn,即保持之前的状态;当C为1时,Qn+1=D,即状态由D来决定。

D锁存器

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3079

3079

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?