提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

当数据无效时,将寄存器时钟关闭能够有效降低功耗, 是低功耗设计的重要方法之一。门控时钟就是当寄存器的输入数据无效时,将寄存器的输入时钟置为0,而此时寄存器值保持不变,减小功耗。

一、为什么要加clock gating?

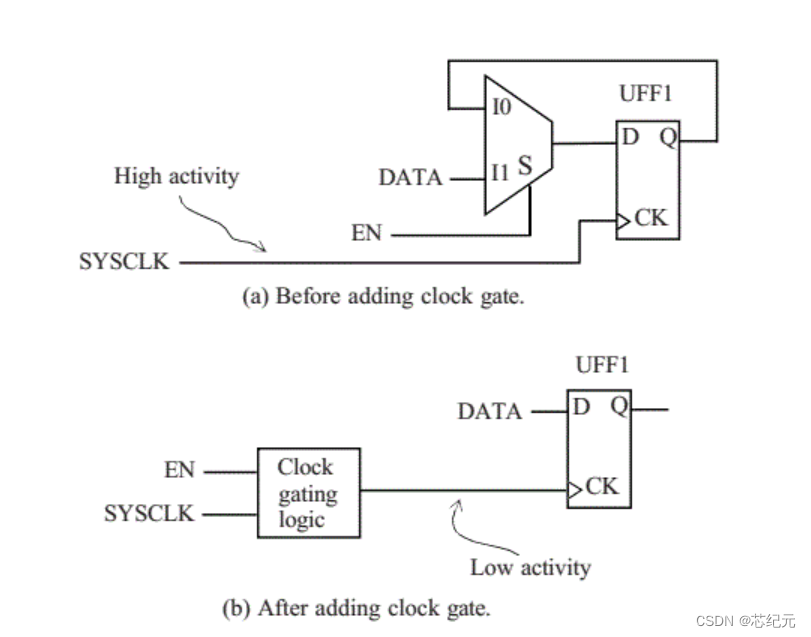

芯片中接近40%甚至更多的功耗是由时钟树消耗掉的。如下图(a)所示,当EN信号为0时,虽然clock toggle, 但flip-flop Q的value仍保持不变,但是由于clock存在,仍有power dissipation; 因此clock gating的目的就是当flip-flop的input不变的时候,把clock关掉来降低功耗,如下图(b)所示。

因此clock gating就是用来保证只有当flip-flop的data input有新的data available的时候,flip-flop的clock pin才toggle。

二、如何判断是不是clock gating?

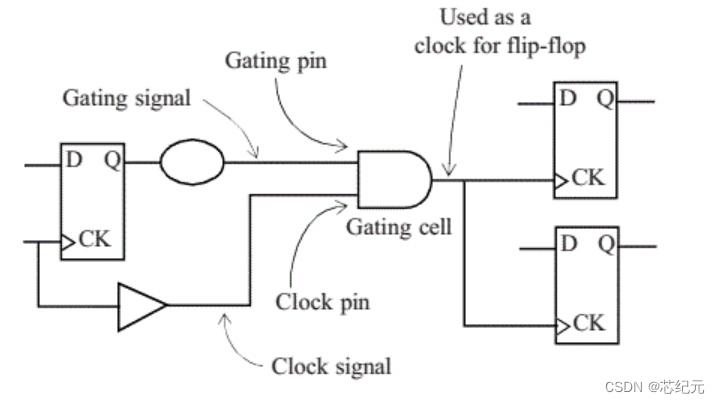

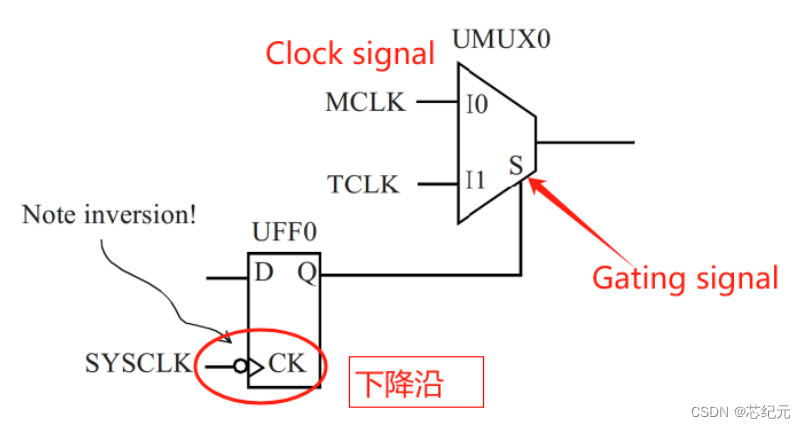

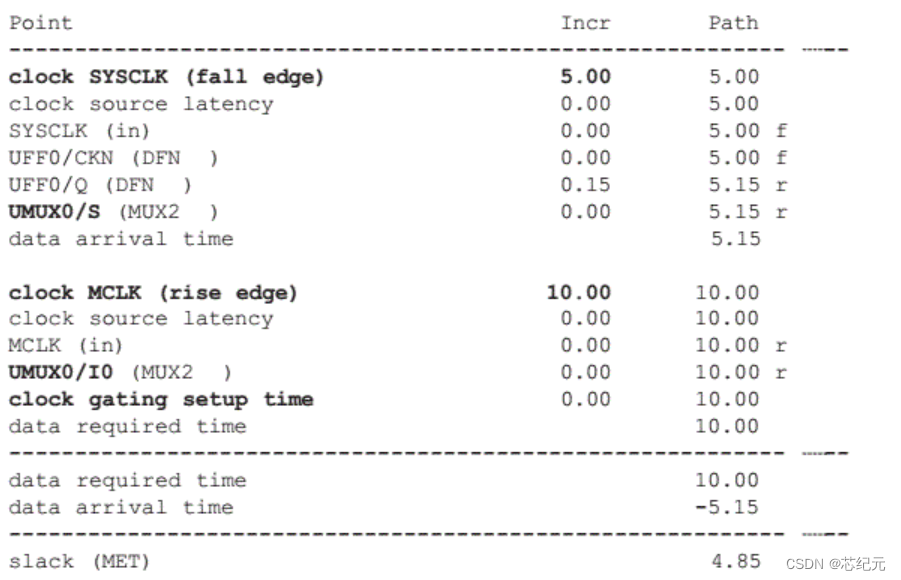

clock gating包括三部分:clock pin, gating pin和gating cell。logic cell的input连接到clock的pin称为clock pin; logic cell的input连接到gating signal的pin称为gating pin; 发生clock gating的logic cell称为gating cell,如下图所示。

如果是clock gating必须满足下面两个条件:

- 穿过gating cell的output 必须 used as a clock downstream。The downstream clock usage 可以是flip-flop的clock端或者output port或者generated clock的master。否则,no clock gating check is inferred。

- gating signal不应该为clock,因此,当gating signal为clock时,必须保证it should not be used as a clock downstream,即gating signal的fanout不能是flip-flop的clock端或者output port或者generated clock的master。否则,no clock gating check is inferred,gating cell的output会被当成generated clock。

三、clock gating的结构有哪些?

1. 纯组合逻辑构成的clock gating

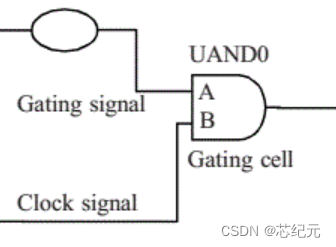

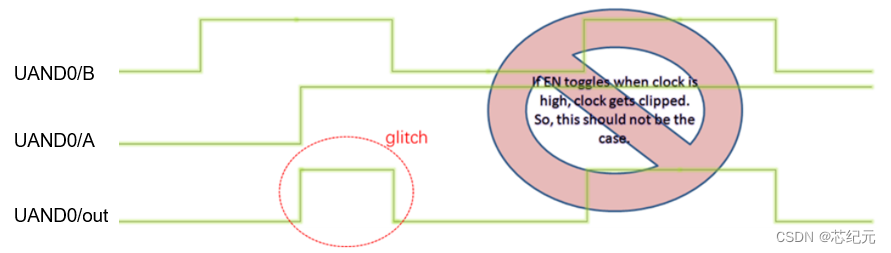

(1)与门AND

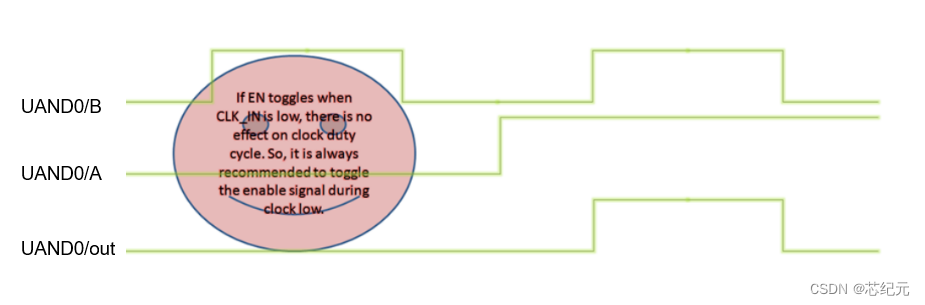

对于AND的clock gating, 当Gating signal为1时, 门控打开,Clock signal可以通过AND传递出去;当Gating signal为0时, 门控关闭,Clock signal无法传到AND的output。

AND的clock gating是高电平有效的clock gating,因此Gating signal的切换必须发生在Clock signal的低电平区间,否则在AND的output可能会出现glitch。

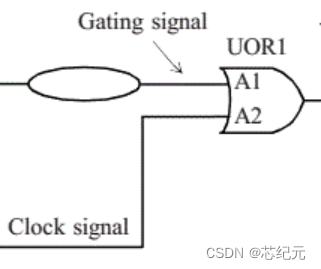

(2) 或门OR

对于OR的clock gating,当Gating signal为0的时候,能采到clock signal的上升沿和下降沿的变化,门控打开,Clock signal可以传递出去;当Gating signal为1的时候,OR的output clock一直为高,没有toggle,门控关闭,Clock signal则无法通过门控传递出去。

OR的clock gating是低电平有效的clock gating,因此Gating signal的切换必须发生在Clock signal的高电平区间,否则在OR的output可能会出现glitch。

(3)多路复用器MUX

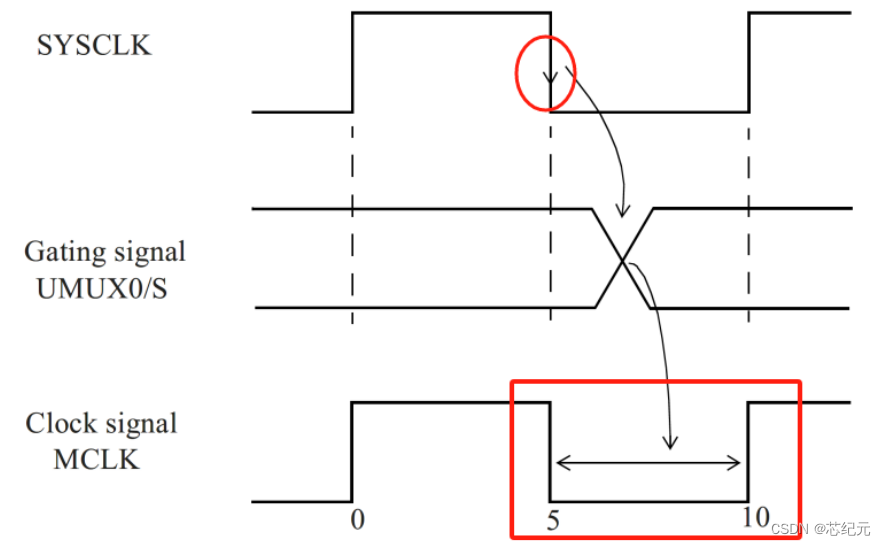

当I0和S分别为Clock signal和Gating signal, 首先要保证S切换的时候TCLK为0,其次需要在MCLK为低电平区间;同理,当I1和S分别为Clock signal和Gating signal, 首先要保证S切换的时候MCLK为0,其次需要在TCLK为低电平区间。mux的clock gating is similar to AND clock gating,是高电平有效的clock gating。

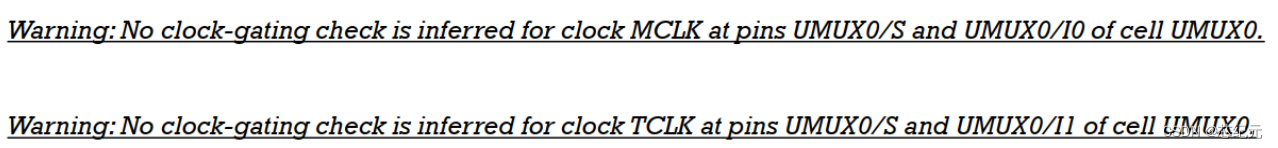

由于门控单元是一个多路复用器(mux),STA不会自动推断为是一个clock gating check,如下图所示。

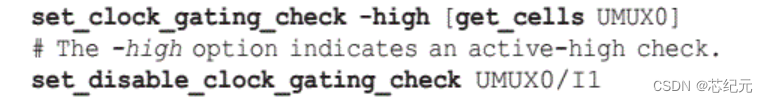

如果让工具去做clock gating check,需要通过set_clock_gating_check命令,command 如下图所示。

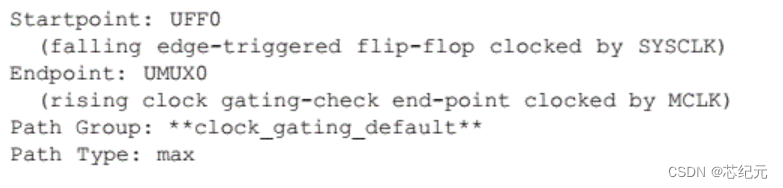

添加上面的commands之后,mux的 clock gating setup timing check report如下所示。

2. 时序+组合逻辑构成的clock gating

(1)Register + AND

上升沿触发

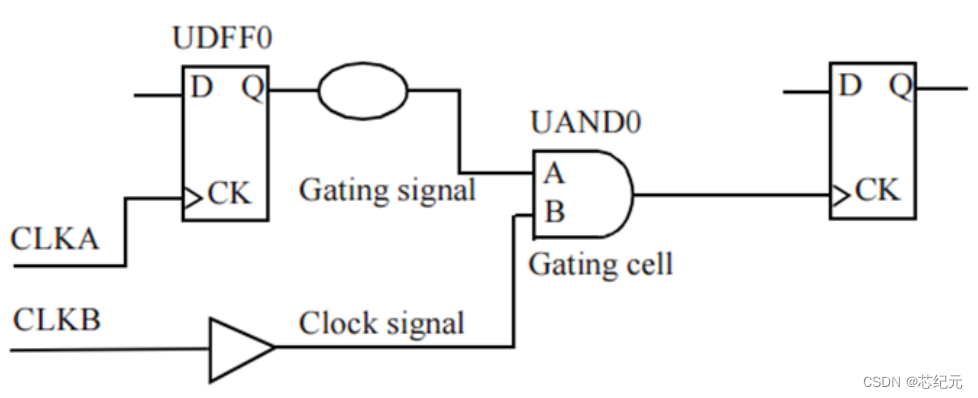

在上图中,UAND0/B 是Clock signal,而Gating signal则由UDFF0/Q经过组合逻辑后传到UAND0/A 。

根据之前讨论的结果,AND Gating signal的切换必须发生在Clock signal的低电平区间。如果Gating signal来自上升沿触发的寄存器,则对于setup check来说,要求Gating signal在Clock signal上升沿之前到达;而对于hold来说,则要求Gating signal只能在Clock signal下降沿之后发生变化。

因此,针对上图电路中的UAND0/B,CLKA发出的Gating signal只能在5 – 10ns的范围内达到,才能满足时序要求,如下图所示。

此时,setup是一个周期check;但是hold不是同沿而是半周期check,比较难meet。

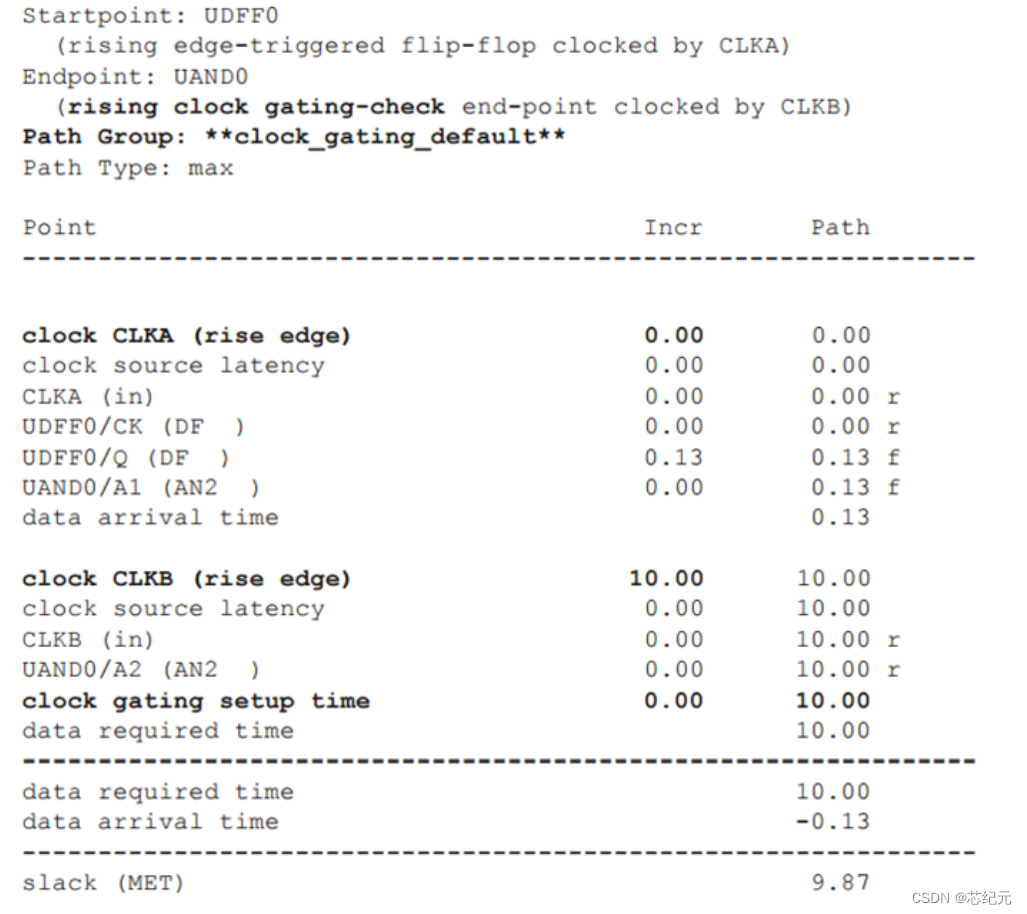

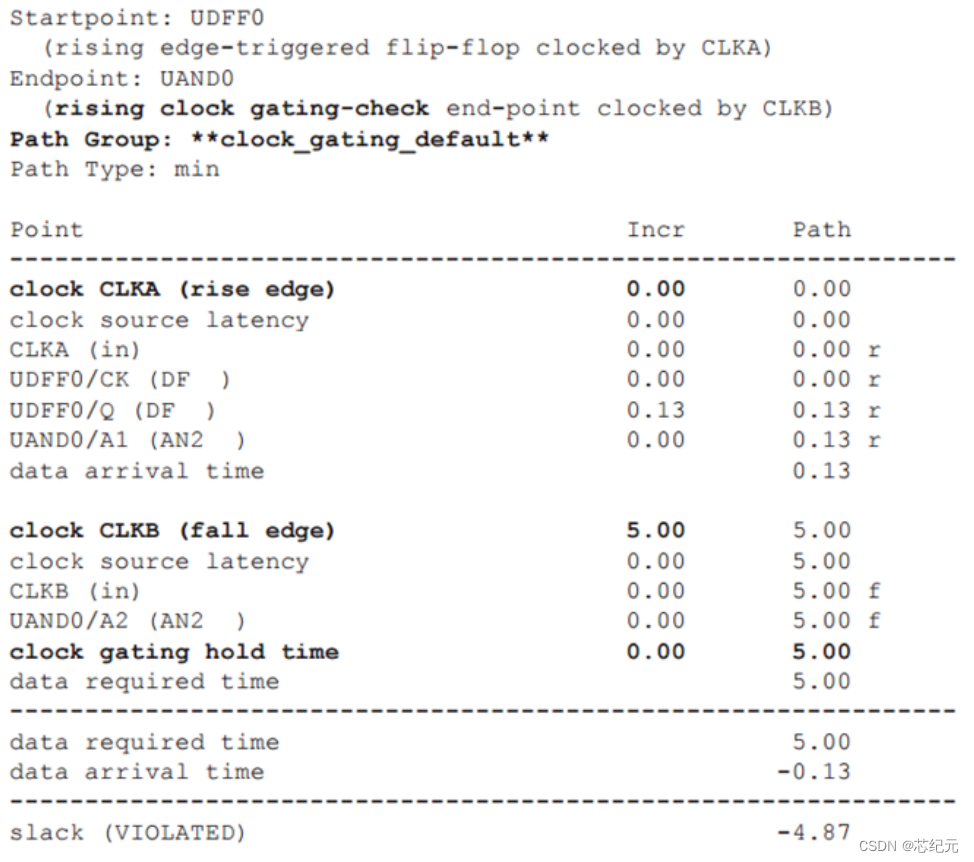

下面是setup/hold timing check report:

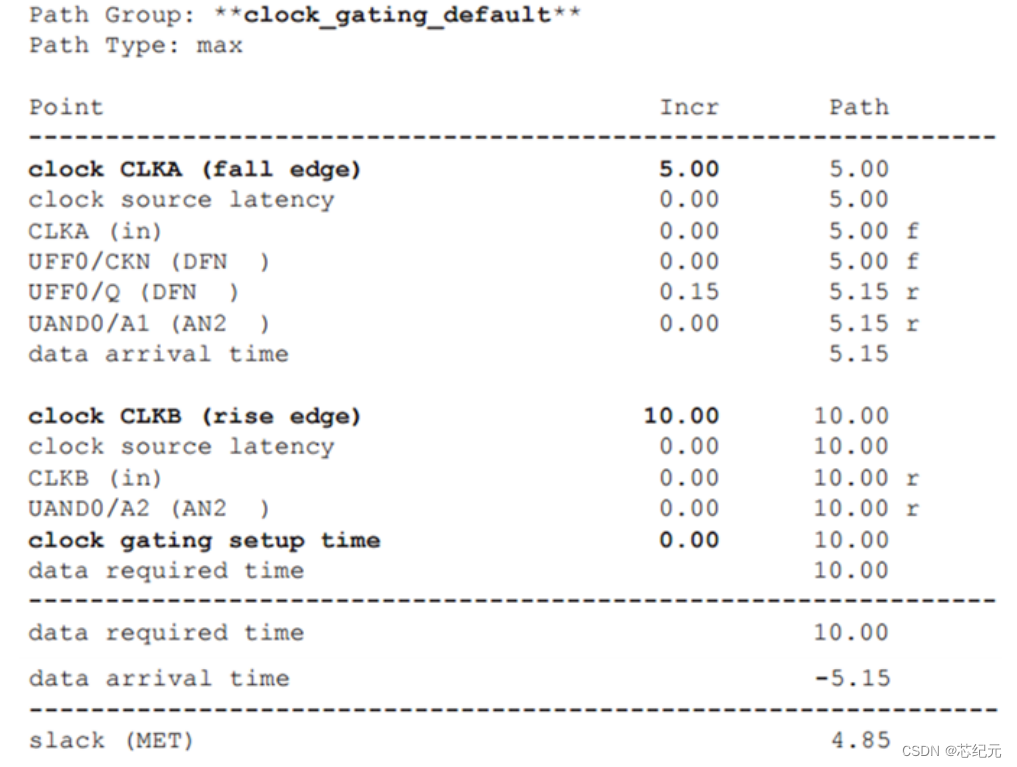

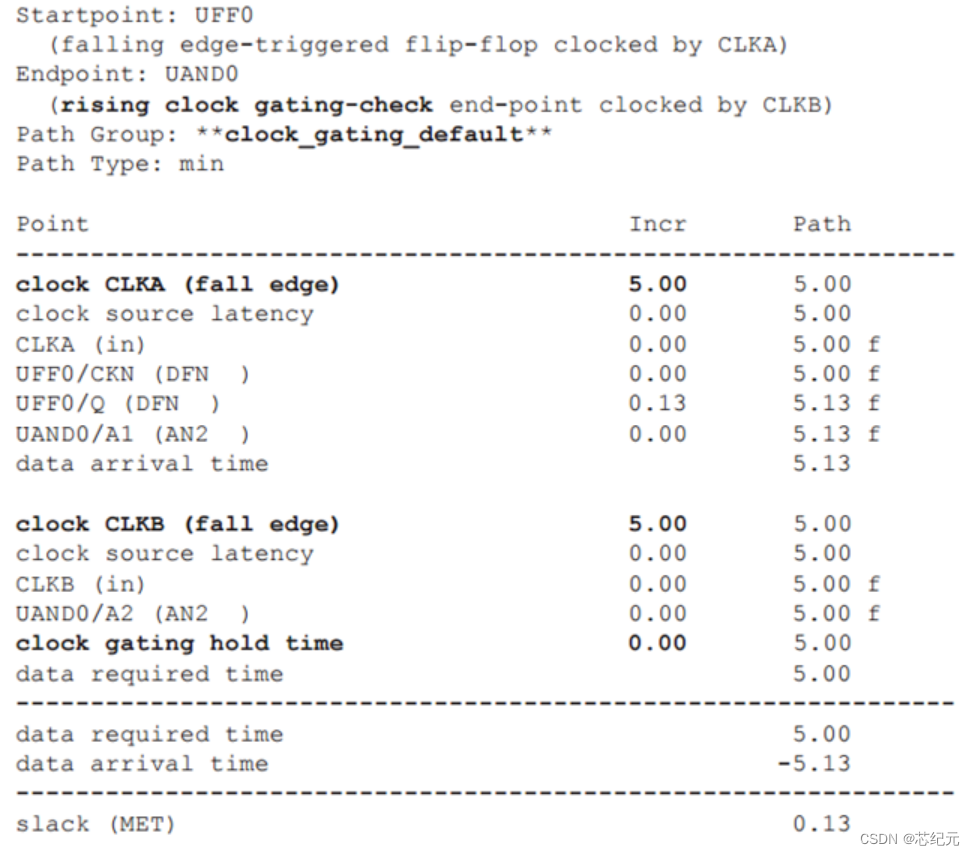

下降沿触发

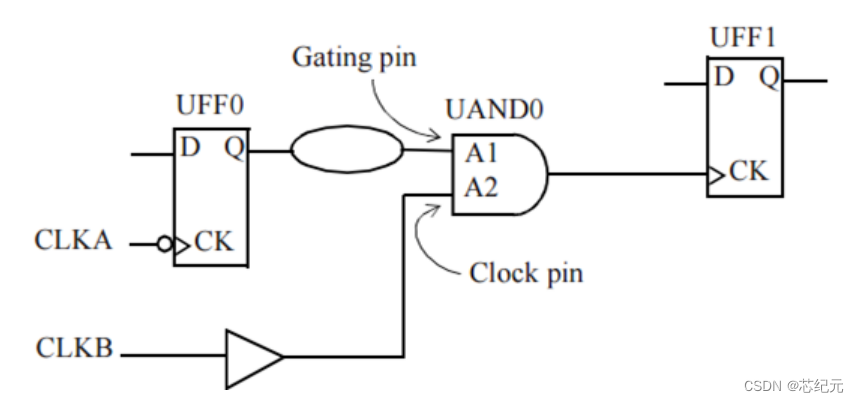

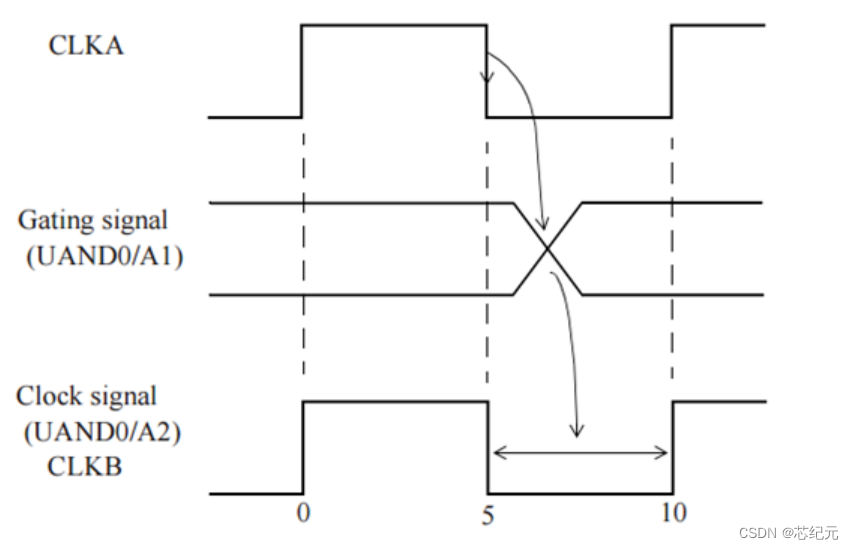

在上图中,UAND0/A1 是Clock signal,而Gating signal则由UDFF0/Q经过组合逻辑后传到UAND0/A2 。

根据之前讨论的结果,AND Gating signal的切换必须发生在Clock signal的低电平区间。

因此,即使使用下降沿触发的寄存器产生Gating signal,对于基于AND的clock gating,Gating signal依然需要在5 – 10ns之间到达,以满足时序要求。

此时,setup是半周期check;但是hold是同沿check。

下面是setup/hold timing check report:

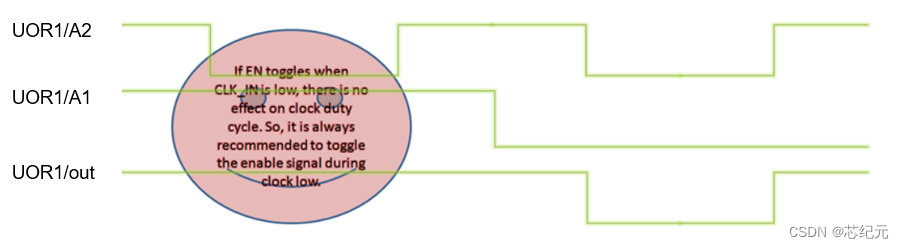

(2)Register + OR

上升沿触发

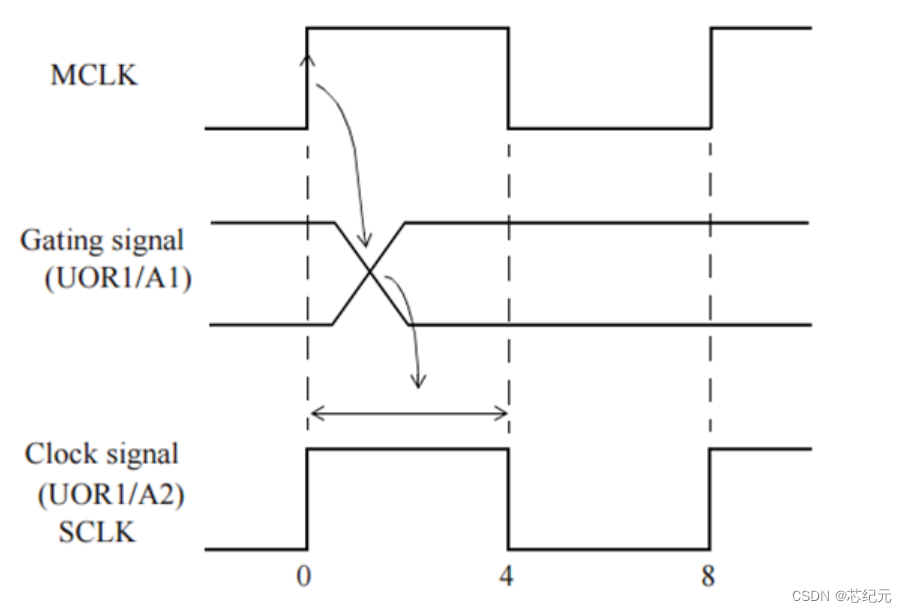

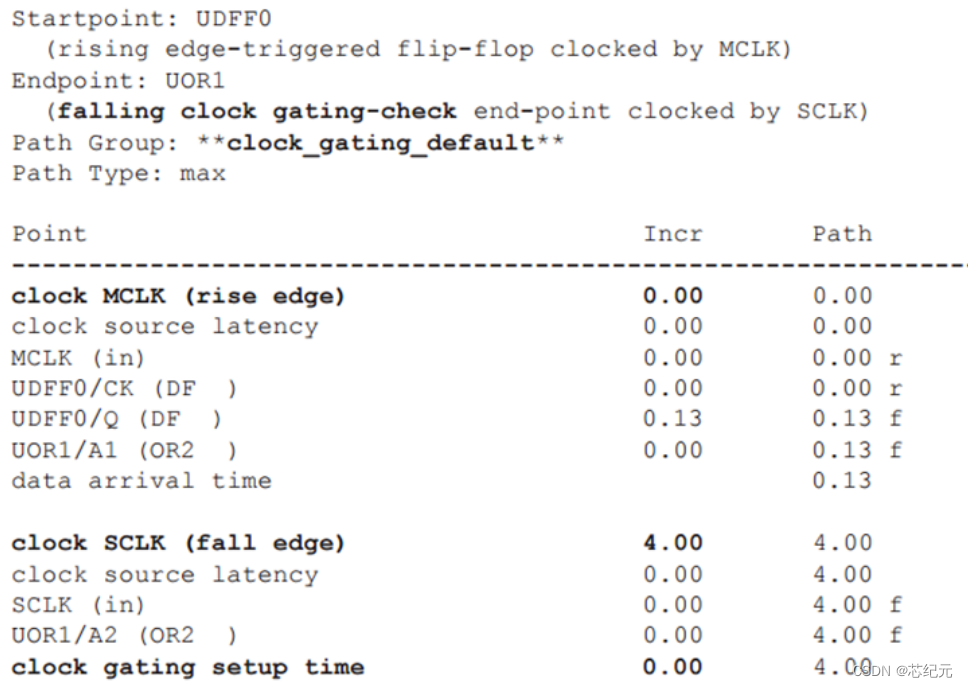

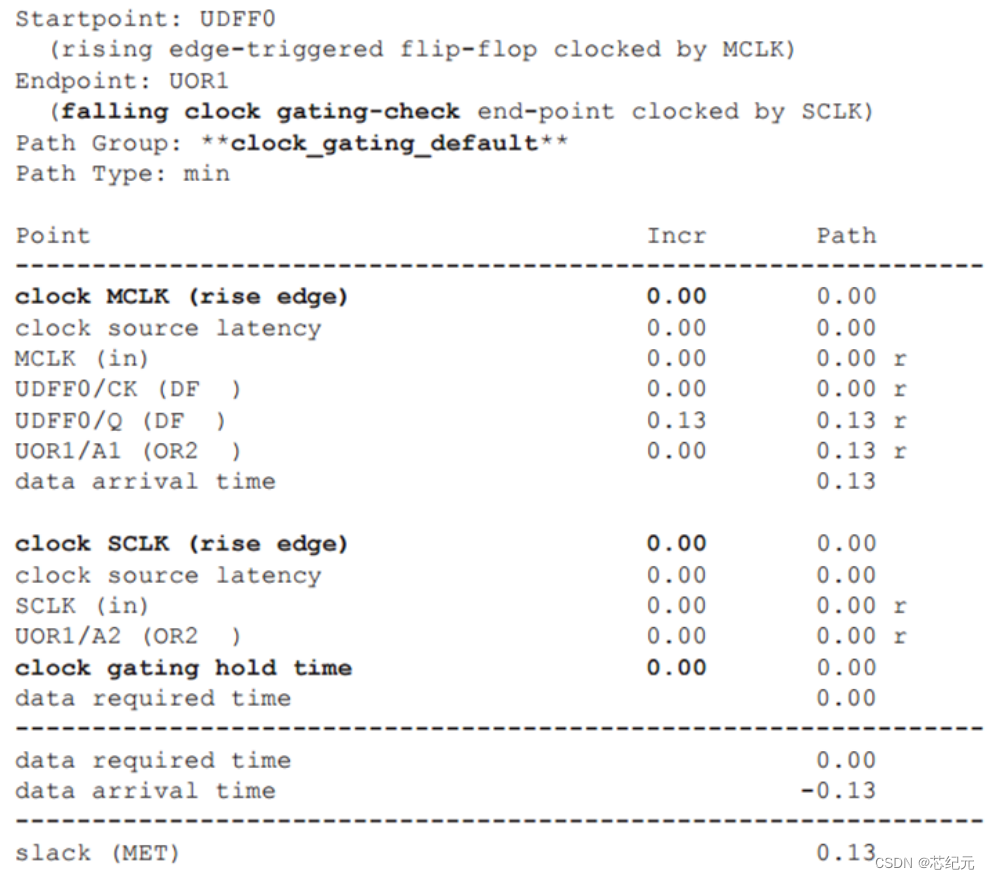

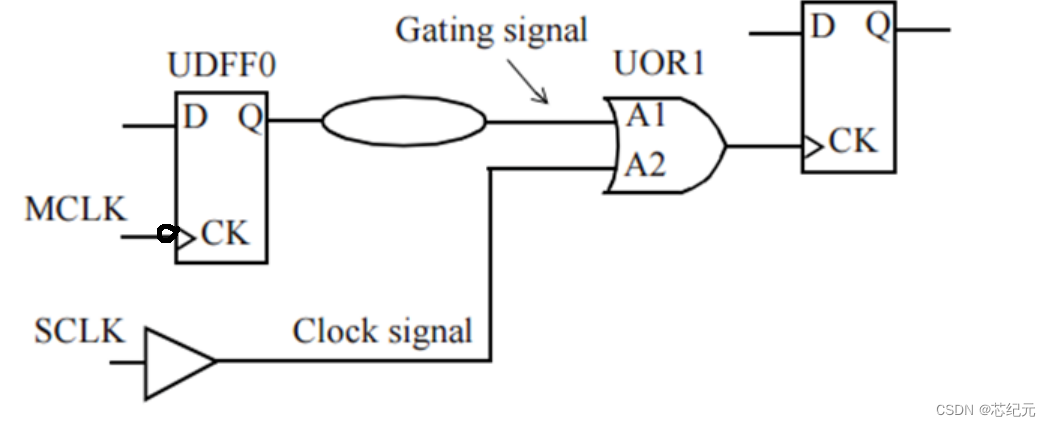

在上图中,UOR1/A2 是Clock signal,而Gating signal则由UDFF0/Q经过组合逻辑后传到UOR1/A1 。

根据之前讨论的结果,OR Gating signal的切换必须发生在Clock signal的高电平区间。如果Gating signal来自上升沿触发的寄存器,则对于setup check来说,要求Gating signal在Clock signal下降沿之前到达;而对于hold来说,则要求Gating signal只能在Clock signal上升沿之后发生变化。

因此,针对MCLK发出的Gating signal,需要在0 – 4ns的范围内到达,才能满足时序要求,如下图所示。

此时,setup是半周期check;但是hold是同沿check。

下面是setup/hold timing check report:

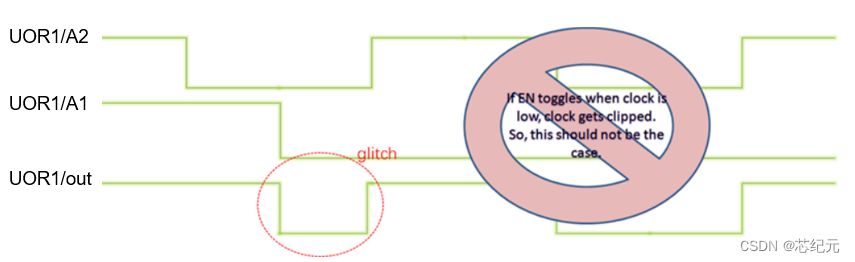

下降沿触发

在上图中,UOR1/A2 是Clock signal,而Gating signal则由UDFF0/Q经过组合逻辑后传到UOR1/A1 。

与之前讨论类似,如果Gating signal来自下降沿触发的寄存器,则setup为 1个周期check,但是hold为半周期check,比较难meet。

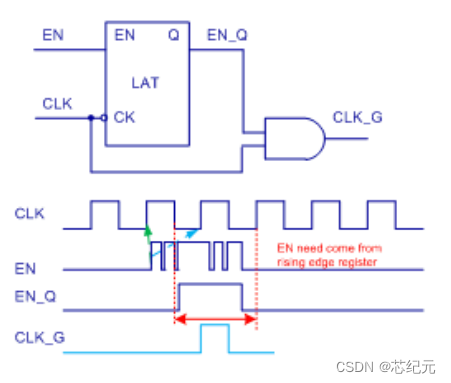

(3)Latch + AND

低电平有效的latch,当 E = 0 时,latch直传(transparent),D端信号的变化会即时反应在Q端;当 E = 1 时,latch关断(closed),Q端保持关断瞬间D端的值。

设计中使用Latch的好处是,相比寄存器的面积更小,功耗更低,可以从后级电路进行time borrowing,更容易满足setup time。

如上图所示,在AND门前面加入low-active latch。当时钟信号是低电平时,latch处于透明状态,根据输出等于输入;当时钟信号从低电平变为高电平时,latch会读取数据输入端的输入信号,并将其保存在锁存器内部的状态中。由于是低电平有效的latch,因此在时钟高电平期间,即使gating信号存在glitch,也不会影响latch的输出。

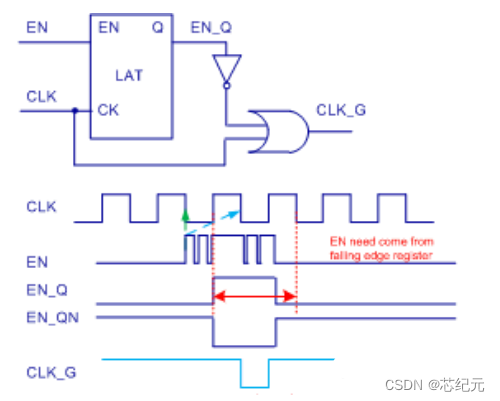

(4)Latch + OR

高电平有效的latch,当 E = 1 时,latch直传(transparent),D端信号的变化会即时反应在Q端;当 E = 0 时,latch关断(closed),Q端保持关断瞬间D端的值。

如上图所示,与latch + AND门不同的是,latch + OR需要使用high-active latch。

总结

因此,在基于AND门的gating技术中,建议使用下降沿触发的寄存器或来低电平有效的latch产生gating信号;在基于OR门的gating技术中,建议使用上升沿触发的寄存器或高电平有效的latch来产生gating信号,以确保满足时序的要求。

1490

1490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?