在某工程中,用到两组DDR3,每组4片。单组DDR3的测试工程都正常,但是两组一起用时工程出现了问题。解决过程记录如下。

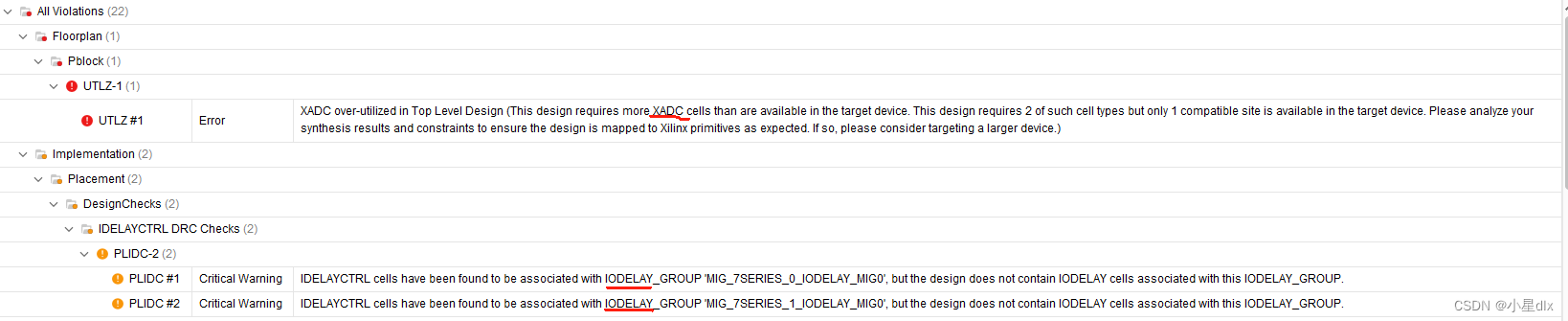

首先使用了创建两个DDR3 IP核,然后进行两次例化,在运行implementation过程中报错。习惯性打开synthesized design,运行drc检查。drc有一条错误和两条严重警告信息,错误信息是关于XADC的,两条严重警告是关于IDELAY的。

可以看到报错信息里说明目标器件只有一个XADC,但是使用了两个XADC,所以报错;严重警告信息是说组名为MIG_7SERIES_0_IODELAY_MIG0以及MIG_7SERIES_1_IODELAY_MIG0的IDELAYCTRL cell没有相对应的IODELAY cell。(可以看到,IP核设计会根据IP名去命名IDELAY组名避免冲突,以防止编译时不知如何放置IDELAY)这个严重警告先不管。

消除XADC的冲突,先尝试用一个IP核,然后包含两个DDR控制器,到分配管脚这一步时发现无论如何无法通过UCF文件识别到管脚,总报错。后发现这种情况下,有些管脚下拉列表里面根本没有,看来一个IP包含两个DDR控制器还是有些限制的。

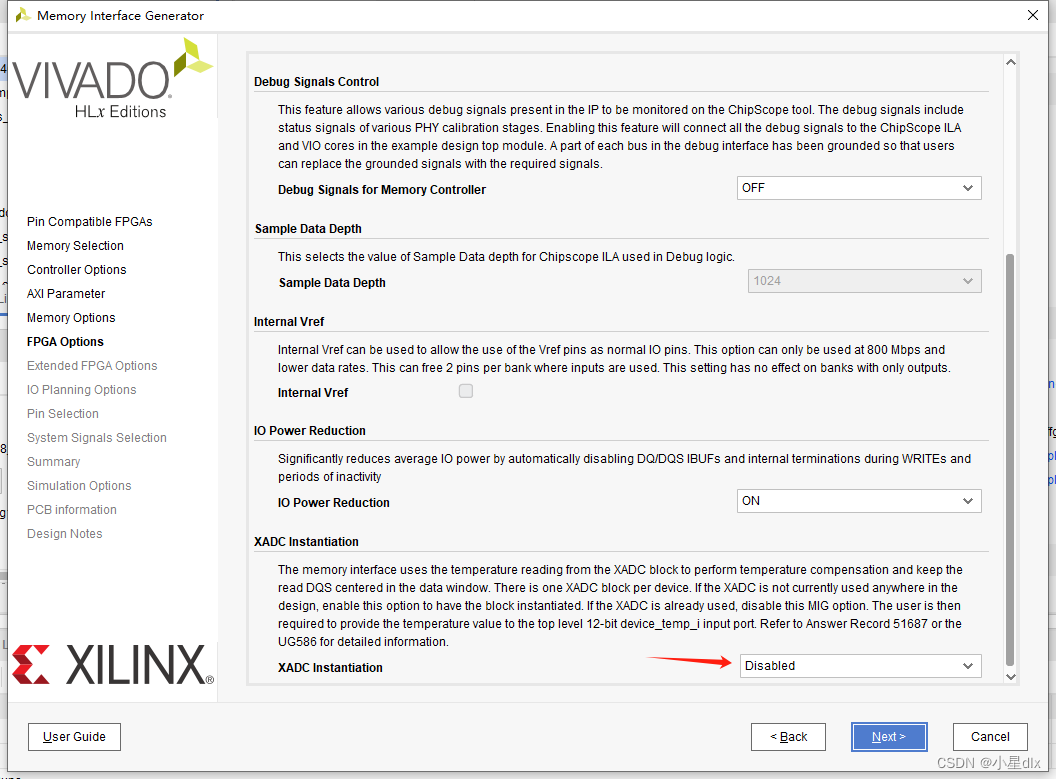

然后尝试将XADC从DDR IP核里面拉出来,开关处于下图所示,选择disable即可。需要注意的是,要把原来的IP删除掉,重新建立IP核,不然会报奇怪的错误。

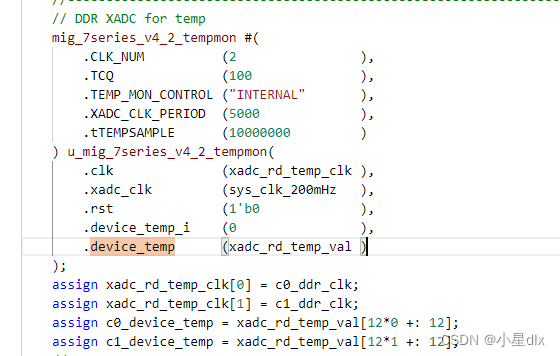

然后将IP核目录下面的mig_7series_v4_2_tempmon.v文件拷贝出来一份,做一些修改。因为我这里要把一个温度数据传给两个DDR IP核,所以需要把温度跨时钟同步到两个时钟下面。关于rst管脚直接给的0,(可能也可以用!locked),时钟需要看源代码用的哪个,我的工程当中用的是ui_clk。(注,我是将IP核目录用vscode打开然后全局搜索关键字去定位的)。

这样修改后,再检查一下时序,如果有跨时钟的,做一下时序约束,跨时钟处理已经在这个里面处理过了。当然,如果XADC还用作它用,可以自行研究XADC。经过前面的修改后,已经可以正确编译通过了。

文章讲述了在工程中遇到的问题,即两组DDR3集成时XADC冲突和IDELAY命名冲突。通过单独使用IP核、调整管脚配置、修改时钟同步及时序约束,解决了这些问题并成功编译工程。

文章讲述了在工程中遇到的问题,即两组DDR3集成时XADC冲突和IDELAY命名冲突。通过单独使用IP核、调整管脚配置、修改时钟同步及时序约束,解决了这些问题并成功编译工程。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?