在对一个设计块进行仿真时,需要准备一个测试模块。该模块大致由三部分组成:第一部分实例引用被测试的模块(即设计块)。第二部分是给输入信号赋各种不同的组合值,即激励信号。第三部分指定测试结果的显示格式,并指定输出文件名。由于测试模块的主要任务是给设计块提供激励信号,所以也称为激励块。

激励块通常是顶层模块,同样用 Verilog HDL来描述。它是以module 开始并以end-module 结尾的,内部包括模块名、数据类型的声明、低层次模块的实例引用和行为语句块(initial或者always),但是不需要声明端口。

在激励块中,通常会使用编译指令timescale 将时间单位与实际时间进行关联。编译指令(compiler directives)为仿真工具提供有关如何解释 Verilog模型的附加信息。编译指令放在模块定义之前,并以反引号(即)开头。timescale的格式为:

timescale time_unit/time_precision

其中,tine_unit为仿真时间单位,time_precision为仿真时间的精度(即最小分辨度)。注意,时间单位通常大于或等于时间精度。

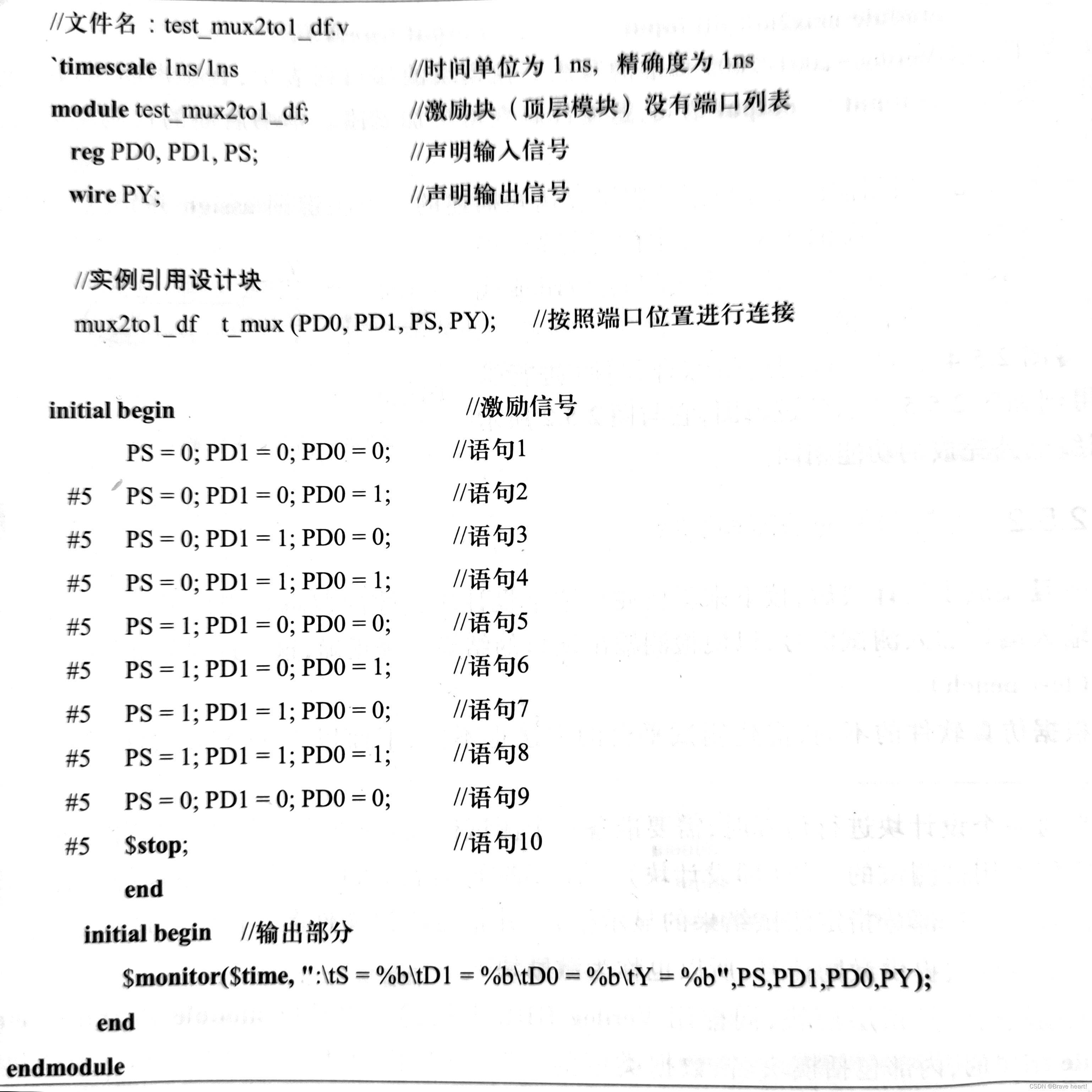

激励块代码如下

接着,声明激励块的名称为test_mux2to1_df。在激励块中,可以重新定义一套信号端口名称,也可以与设计块中的端口名相同,但输入信号的数据类型要求为reg,以便保持激励值不变,直至执行到

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7345

7345

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?