1.1 建立时间与保持时间

理解时序路径,首先要理解寄存器的建立时间和保持时间,一个边沿触发的寄存器为什么要有建立时间和保持时间,因为边沿触发的寄存器在时钟有效沿到来时,依据自身的采样能力和驱动能力,要求输入到D端的信号要尽可能保持稳定,如果输入到D的信号不稳定,则会造成信号的错误采样,导致该寄存器输出到Q的信号形成不定态,因此衍生出建立时间和保持时间的概念。

建立时间(Setup Time):在时钟有效采样沿到来之前,输入到寄存器D端的信号应该要保持稳定的时间;

保持时间(Hold Time):在时钟有效采样沿之后,输入到寄存器D的信号应该要保持稳定的时间。

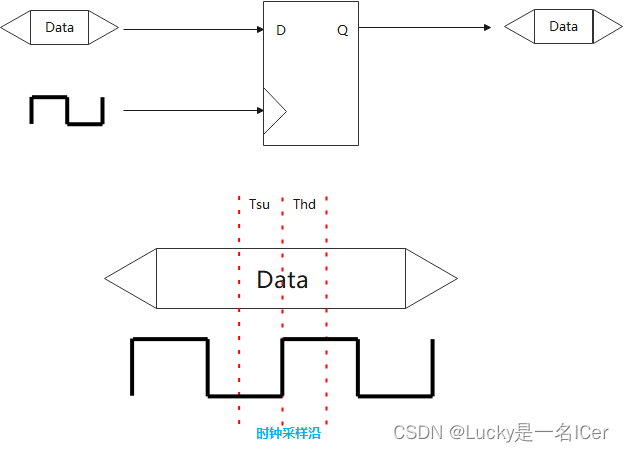

图1.1.1 寄存器的Setup Time 和Hold Time

如图1.1.1所示,寄存器的时钟采样沿到来时,输入数据到达D在沿前和沿后应该保持稳定的时间即为寄存器的Setup Time 和Hold Time,这两个时间组成一个时间窗口,在这个时间窗口内,输入如果是保持稳定不变的,我们认为寄存器能够稳定采样输入D的信号,如果在窗口内数据发生跳变,则认为此处存在亚稳态,即此时寄存器的输出Q有可能是不确定的状态,形成Violation。

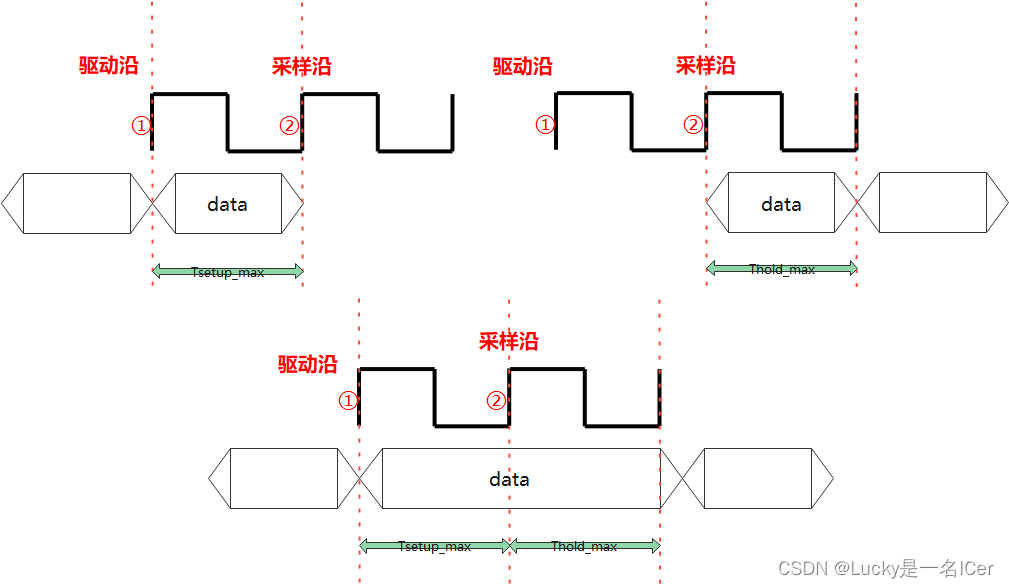

根据SetupTime和HoldTime的定义,可以推测出,理想的建立时间最大值和理想的保持时间最大值如图1.1.2所示,从理想的角度看,建立时间最大值为时钟采样沿前的一整个周期,而保持时间最大值为时钟采样沿后的一整个周期,即横跨两个时钟周期。

图1.1.2 最大建立时间和最大保持时间关系

1.2 基本的时序路径

STA的宗旨,就是在研究两个寄存器之间数据的delay,对于寄存器的边界,认为外部时序是不可见的,但仍然可以抽象为模块或者单元或者芯片外部有一个寄存器,只不过外部寄存器的时延无法通过本芯片或者本模块的lib/db中的Timing Ack所体现,称之为input或者output delay建模。而STA的底层逻辑,就是建立芯片或者模块两个寄存器(在时钟的有效沿作用下)间延时模型。能够引入的延时有:

- 组合逻辑的延时

- PR在走线时引入的信号buf延时

- 板级走线延时

- 时钟有效沿到驱动信号到寄存器输出Q的延时

- IO延时

- 外部器件延时

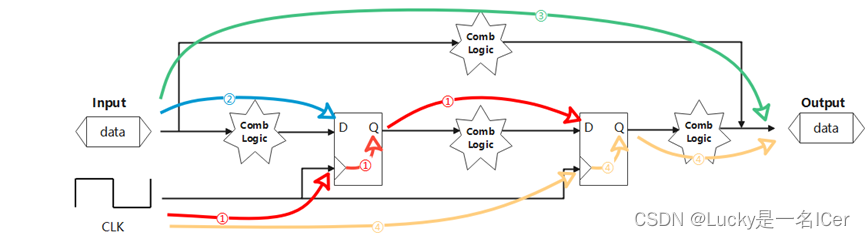

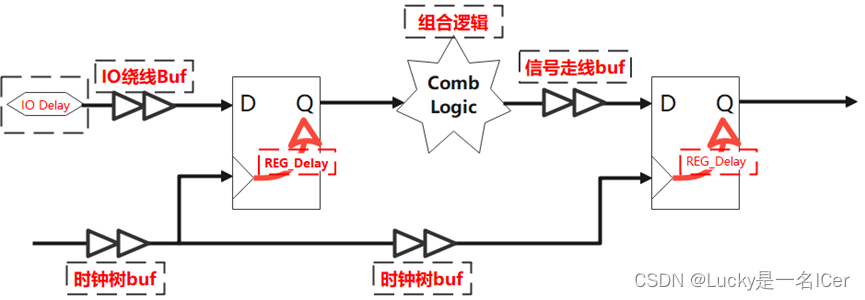

对于芯片内部时序路径的抽象,即可体现为如图1.2.1的时序路径说明。

图1.2.1 基本时序路径

图1.2.1 基本时序路径

对于当前模块、芯片或者harden,基本的时序路径为如下4条:

- 输入时钟经过寄存器的延时,经过组合逻辑延时到寄存器D端

- 输入时钟经过寄存器的延时,经过组合逻辑延时到输出

- 输入信号经过组合逻辑到寄存器D端

- 输入信号经过组合逻辑到输出

因此可以作为路径终点的point为:芯片输出,寄存器的D端。

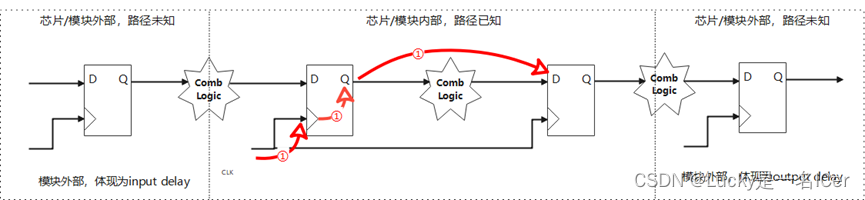

为什么一个模块,或者芯片的时序路径只有这四条,底层逻辑其实就是两个寄存器之间的路径,如图1.2.2所示。

图1.2.2 时序路径建模

图1.2.2 时序路径建模

对于外部路径,可以假象芯片或者模块互连的外部存在一个寄存器,经过走线(可能是板级走线,也可以能是die内的PR走线,等价为组合逻辑延时)进入到芯片内部的寄存器D;因为模块外部路径,对于本模块的STA分析不可见,因此等价为输入方向的input delay,在同步设计下,clk和data的delay要耦合到时序路径上做分析;对于输出方向,可以假想模块外部存在一个寄存器,模块输出经过组合逻辑到外部假想模块的寄存器D,经过了走线,或者组合逻辑,或者IO等延时,这些延时均可等价建模为组合逻辑延时,因为模块外的信号时序不可见,因此对于输出可等价建模为output delay。穿模块的组合逻辑同理,可以认为模块内外存在两个寄存器,即驱动寄存器和采样寄存器,路径可简化为核心的驱动采样寄存器建模图,即图1.2.1所示。

理解最核心的驱动采样时序分析图后,对于各类型的约束,如IO约束,综合的过约,PR做树,修Timing的理解,即可得心应手。

1.3 时序路径中的延时

时序路径中的延时模型,可以分为两大类:一类是寄存器本身带来的延时,主要是时钟驱动沿到来时,数据到寄存器Q端的输出延时;另一类可归类为组合逻辑延时,主要包括前端写的组合逻辑延时,PR在Routing阶段插入的buf延时,IO的延时,板级走线的延时,做时钟树(CTS)阶段,PR在时钟路径上插入的buf同样也可以认为是组合逻辑延时。延时分析如图1.3.1所示。

图1.3.1 时序路径上的延时模型

如图1.3.1所示,延时模型中,黑色虚线框可归类为组合逻辑延时,而红色虚线框中的延时为reg类型延时,底层逻辑均可建立为lunch reg capture reg模型(LRCR),实际情况都是围绕LRCR模型的变种。

2.1 寄存器之间的setup余量计算

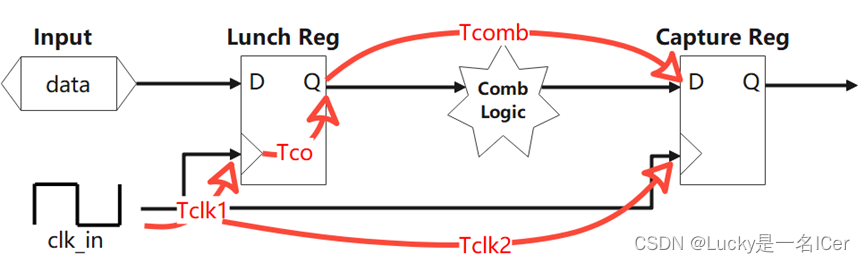

前文叙述了lunch reg capture reg模型为STA底层的核心逻辑,那么对于setup余量的计算公式即可根据LRCR模型计算而来,首先给出setup slack的定义:要求数据到达的时间与实际数据达到时间之间的差值,此处要求数据达到的时间定义为数据刚刚好满足capture reg能够采样到稳定data的时间点,而实际数据达到时间是指数据经过实际的器件延时后到达的时间点。如图2.1.1所示的延时模型图。

图2.1.1 路径延时模型

如图2.1.1所示,Tclk1为输入时钟到Lunch Reg的走线延时,Tco表示为Lunch Reg的寄存器传输延时,Tcomb为组合逻辑延时,Tclk2为输入时钟到Capture Reg的走线延时。Setup计算要满足在一个周期内,要求数据到达的时间要大于实际数据应该到达的时间,即Require减去Arrival,也就是说,实际到达时间要比要求达到的时间短,才可以满足Capture Reg的采样要求。

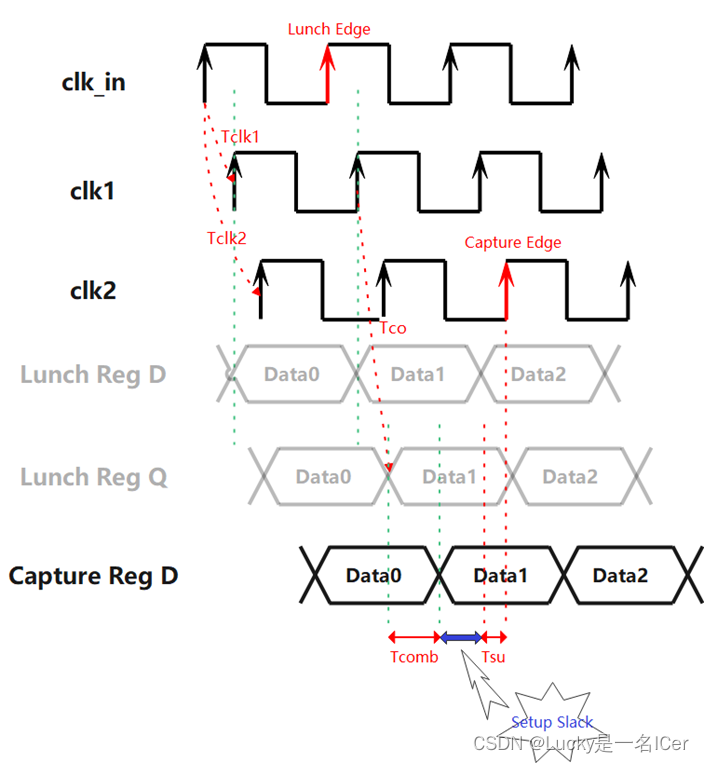

图2.1.2 建立时间余量说明

图2.1.2 建立时间余量说明

如图2.1.2所示,信号从lunch沿到Capture沿,假设时钟周期为T,数据要求到达的时间为:

Trequire=T+Tclk2-Tsu

而数据实际达到时间为:

Tarrival= Tclk1+Tco+Tcomb

而setup slack为:

Setup Slack= Trequire- Tarrival=(T+Tclk2-Tsu)-(Tclk1+Tco+Tcomb)

Setup Slack= (Tclk2-Tclk1)+ T-Tcomb-Tco-Tsu

分析:

如果Setup slack为负数,则证明有setup违例,路径存在问题,需要优化Timing。

- 首先看时钟周期对setup的影响,时钟周期越大,即频率越低,Setup余量越大,因此降频对Setup十分友好;

- 再看Tcomb,Tcomb越小,则setup slack越大,因此前端在RTL设计时,应尽量减少关键路径的组合逻辑深度,对Setup友好;

- 再看lunch reg和capture reg的时钟走线延时,Tclk2越大,Tclk1越小,Setup Slack越大,因此Capture reg的时钟推树路径越长,对Setup越友好,但是对Hold越不友好,在后续hold分析中探讨,因此PR在做时钟树时,先要尽可能把时钟树做平,即时钟在同步路径的分叉点越晚越好,以减少因时钟走线对setup和hold的影响。

- 最后看Tco和Tsu,这两个参数为器件参数,即stdcell的工艺参数,工艺节点越先进,Tco和Tsu越小;在相同工艺节点下,LVT器件比HVT器件的Tco和Tsu小,因此DC综合策略为在关键路径上采用LVT,而时序不紧张的路径使用HVT,但LVT又会引入面积和功耗的开销,因此DC在PPA的角度权衡HVT和LVT的使用;同样这两个参数在不同Corner下也不一样。

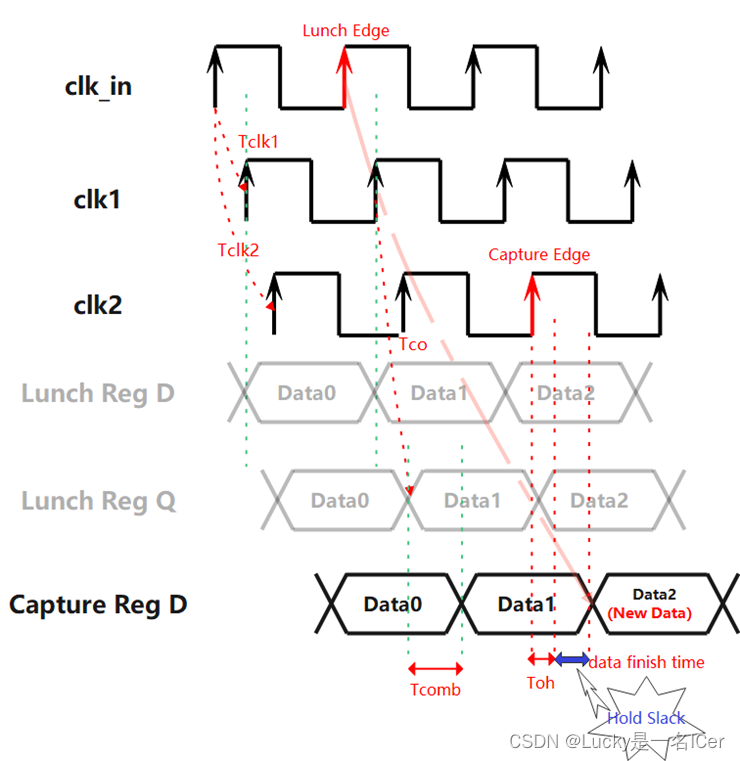

2.2 寄存器之间的hold余量计算

Hold Slack的定义为:数据实际结束位置和要求结束位置之间的差值。如果数据实际结束的位置小于数据要求结束的位置,则认为Capture寄存器的Hold Time不满足,容易形成Hold违例,因为Hold要求数据在寄存器采样时钟沿之后应该保持的时间。基于图2.1.1的LRCR模型,可抽象出Hold Time的计算时序如图2.2.1所示

如图2.2.1 保持时间余量说明

如图2.2.1 保持时间余量说明

如图2.2.1所示,假设时钟周期为T,对于Lunch沿的数据实际结束时间为:

Tarrival=Tclk1+ Tco+ Tcomb+T

而数据要求的结束时间为:

Trequire= Tclk2+ Tho+T

而Hold Slack则理解为数据实际达到时间减去数据要求达到时间:

Hold Slack= Tarrival-Trequire=Tclk1+ Tco+ Tcomb+T-(Tclk2+ Tho+T)

Hold Slack=Tclk1- Tclk2+ Tcomb+ Tco- Tho

分析:

如果Hold Slack为负数,则证明Hold存在违例,当前路径的Hold有问题,需要修复Hold。

- 先看公式,从公式上发现,整个Hold Slack与时钟周期没有关系,因此时钟周期不会影响hold,因此降频或者提频,对Hold Time都不影响

- 再看Tcomb,可以发现,组合逻辑级数越大,对于Hold越友好,但上文所述,组合逻辑级数越大,对于Setup越不友好,因此通常的做法是,前端仅需保证Setup有余量,修hold可以在相关违例路径上插入buf,借setup的余量来修hold

- 再看Tclk1和Tclk2,正如前文setup分析结果,Tclk1的增加对Hold友好,而Tclk2的增加会恶化Hold,而却有利于setup,因此PR在做时钟树时,会优先把树做到尽量平,以减少时钟走线对Setup和Hold的影响。当然在实际工程中,大多是时钟树无法做很平,此时就会在一些违例的路径上做优化微调,针对hold违例还是setup违例,调整Tclk1和Tclk2,也可以在数据路径上借setup余量来修hold

- 最后看Tco和Tho,两个参数是器件的参数,分析与setup的分析相同,即工艺越先进,对Hold越友好

2.3 Setup余量和Hold余量的理解

通过上两个小结的分析发现,setup余量和hold余量的加和为:

(Tclk2-Tclk1)+ T-Tcomb-Tco-Tsu+ Tclk1- Tclk2+ Tcomb+ Tco- Tho =T- Tsu- Tho

即两个余量的加和刚好等于一个时钟周期减去对应reg的setup时间和hold时间,此时也可以解释为什么后端修hold违例的时候可以借setup的时间,因为整体的余量为一个时钟周期,setup余量大了,那hold的余量就会小,而hold的余量大了,setup的余量就会小。

当然在实际工程中,也会出现setup和hold余量加和不为一个T,即hold违例很大,而setup余量很小,无法借setup来修hold,这类问题多和时钟相关,时钟存在抖动或者时钟树在不同路径的延时模型不同,会造成这类问题的发生,实际工程应当杜绝这种情况出现,因为这种情况会造成timing无法修复,一般要检查STA的约束是否合理。

4191

4191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?