总结课程的文章推荐:http://t.csdn.cn/fWPf9

塞琳思:XDC,DC:SDC 都是以这节课为基础。——目标:为DC做准备! check 寄存器的setup/hold。 了解 clock:占空比、延迟等。 高级STA:如 on-chip variation, 静态时序分析——On-chip Variation OCV, CPPR模式 - 简书

目录

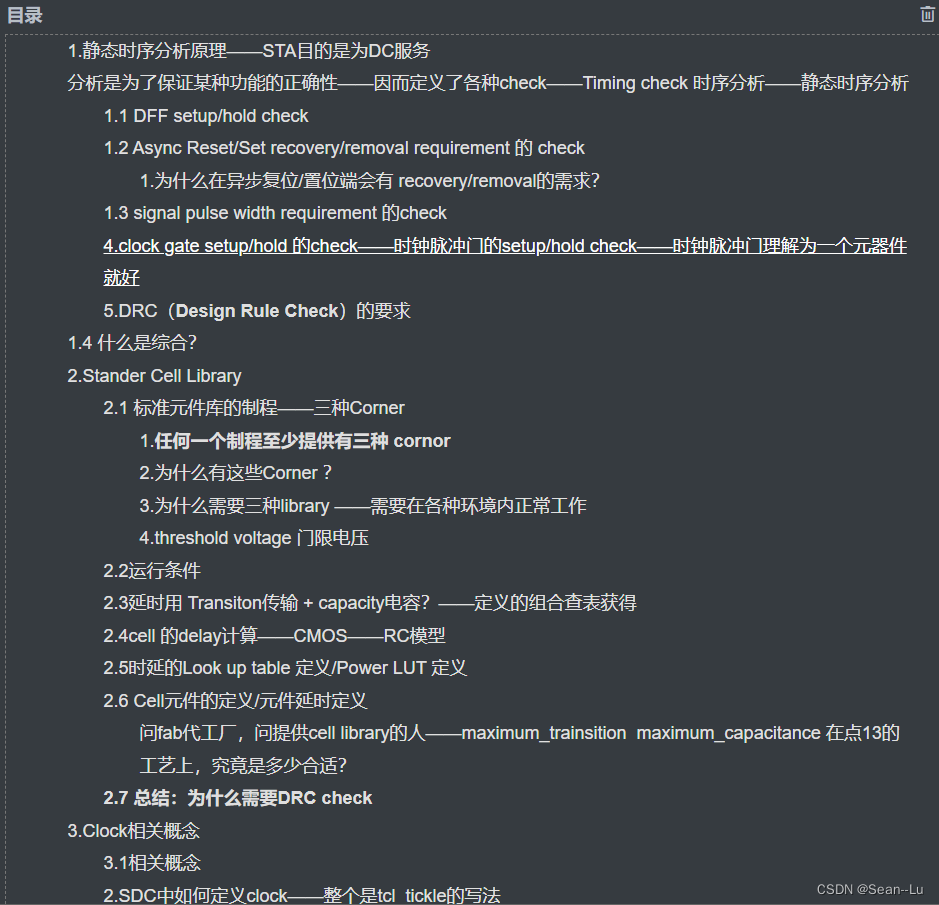

分析是为了保证某种功能的正确性——因而定义了各种check——Timing check 时序分析——静态时序分析

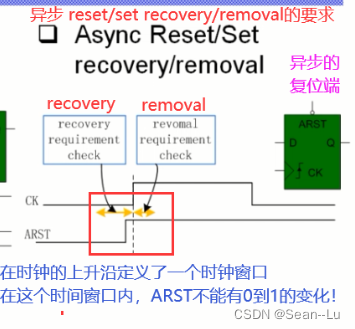

1.2 Async Reset/Set recovery/removal requirement 的 check

1.为什么在异步复位/置位端会有 recovery/removal的需求?

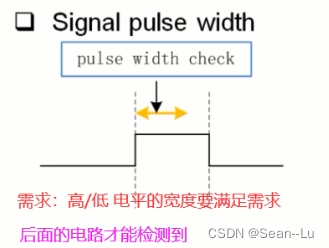

1.3 signal pulse width requirement 的check

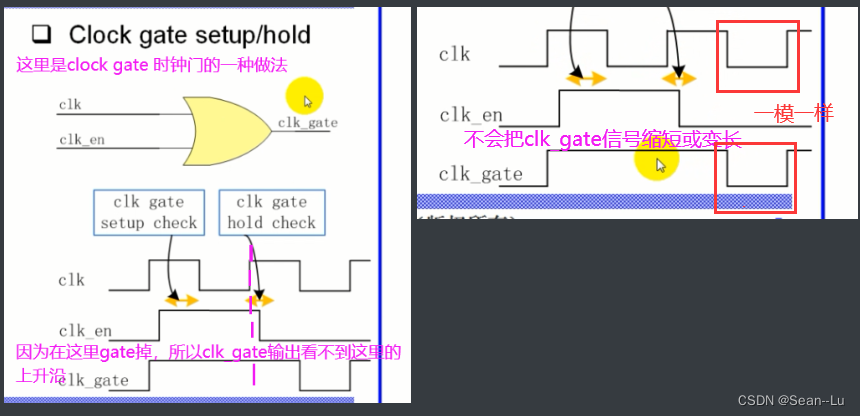

1.4 clock gate setup/hold 的check——时钟脉冲门的setup/hold check——时钟脉冲门理解为一个元器件就好

3.为什么需要三种library ——需要在各种环境内正常工作

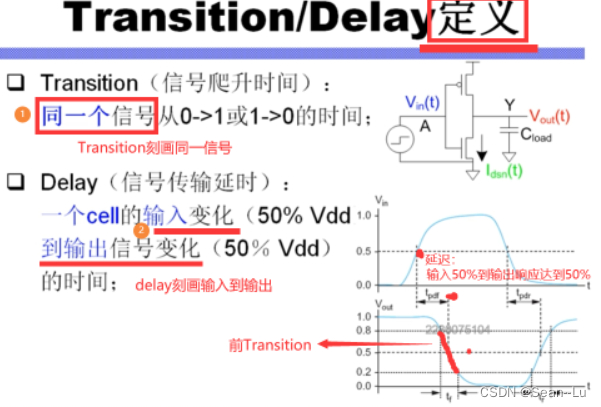

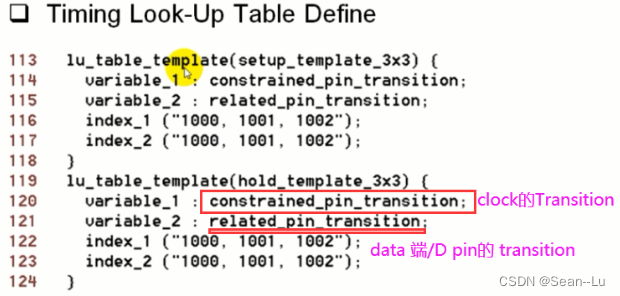

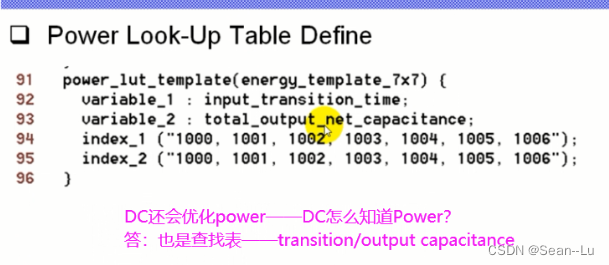

2.3延时用 Transiton传输 + capacity电容?——定义的组合查表获得

2.5时延的Look up table 定义/Power LUT 定义

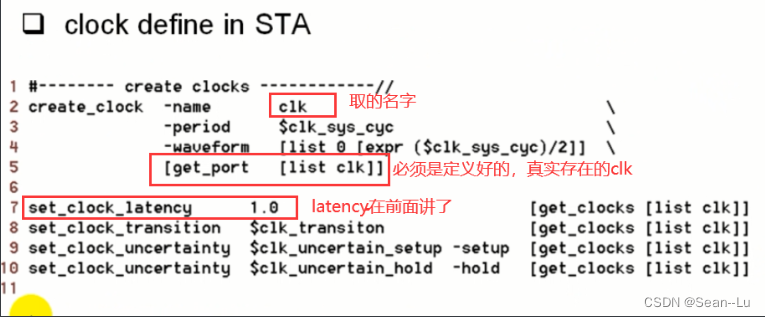

3.2 SDC中如何定义clock——整个是tcl tickle的写法

1.静态时序分析原理——STA目的是为DC服务

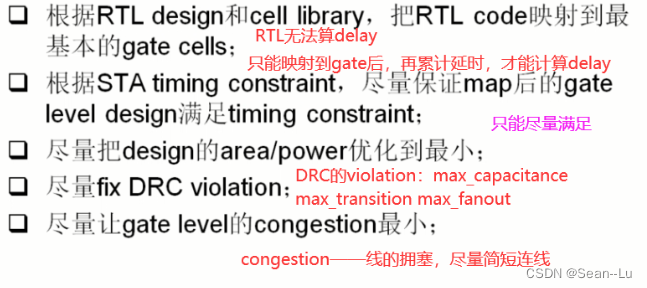

DRC和root DRC检查有差别,root的会检查金属线的宽度等,我们这里是DC综合的DRC,其余DRC是place布局布线工具中需要满足的。

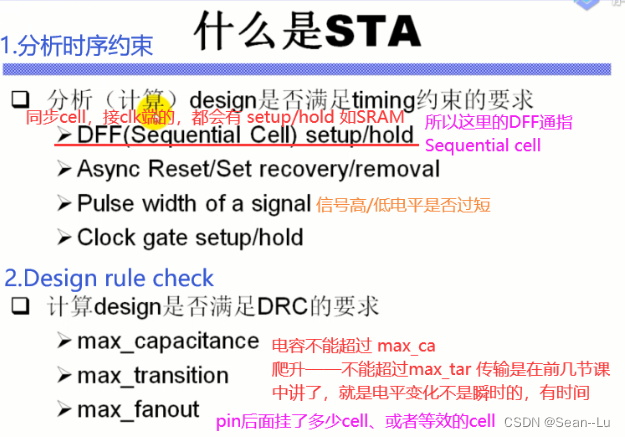

分析是为了保证某种功能的正确性——因而定义了各种check——Timing check 时序分析——静态时序分析

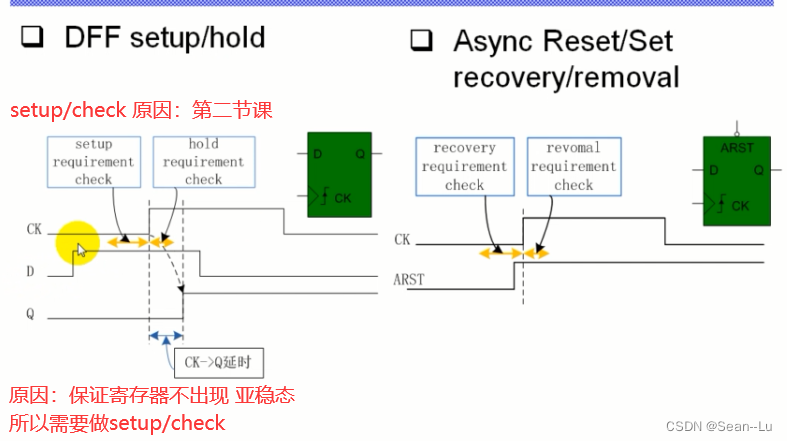

1.1 DFF setup/hold check

寄存器——原因:保证寄存器不出现 亚稳态。所以需要做setup/check

1.2 Async Reset/Set recovery/removal requirement 的 check

1.为什么在异步复位/置位端会有 recovery/removal的需求?

假设没有 reset/removal 形成的时间窗口,那么如图中在CK的上升沿,ARST同时生效,此时寄存器是复位?还是将D端的数据寄存到Q?——存在歧义! 假设design中有100个寄存器——那么可能出现,其中40个复位了,而其他60个开始进行计算了,出现了不同步的现象!——此时RTL仿真和行为出现了差异。

为什么不定义AReset 1 到 0 的窗口?——因为复位端有效,就算抓到了信号,最后也会被reset,所以最终整个效果是——100个寄存器都被复位了!(顶多出现了一些毛刺)

1.3 signal pulse width requirement 的check

①通常用在 clock 检测上——时钟宽度不能太短——否则寄存器等不会工作

②同时也会放在Async Reset端去看——reset信号的宽度不能太短——否则寄存器等不会复位

1.4 clock gate setup/hold 的check——时钟脉冲门的setup/hold check——时钟脉冲门理解为一个元器件就好

如果clk gate发生violation,比如clk_en在clk的下降沿才拉高,这样组合逻辑或门的输出clk_gate就会先低后高,产生一个非常短的毛刺,这就不行了,所以这里就要求clk_en在上升沿后面一点点,在下降沿前面一点点,这样就不会clk gate violation。

这里是clock gate时钟门的一种做法——因为在这里gate掉,所以clk_gate输出看不到这里的上升沿。 为什么会有clock gate的setup/hold check?——保证clk_gate输出不会有毛刺 此图的hold还有点violation。

1.5DRC(Design Rule Check)的要求

还包括计算design是否满足DRC(Design Rule Check)的要求:电路的最大电容不能超过设置的最大电容(capacitance)、电路的翻转时间(transition)不能超过设置的最大值,电路的扇出(fanout)不能超过最大值。

1.6 什么是综合?

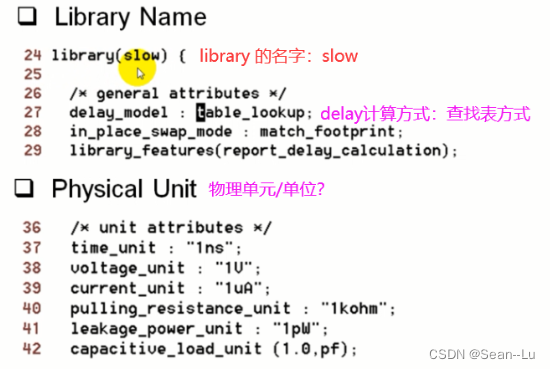

2.Stander Cell Library认识元件库

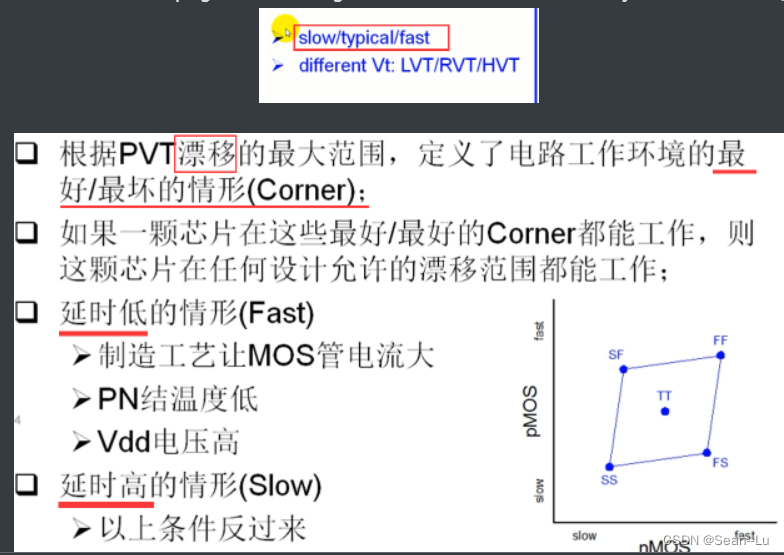

2.1 标准元件库的制程——三种Corner

1.任何一个制程至少提供有三种 cornor

SS:n/p都慢的Corner,TT:均为标准水平,FF:n/p都快的Corner

2.为什么有这些Corner ?

**在slow Corner的时候——关注setup分析check——因为cell比较慢(因为p/N管子工作在slow状态下,此时整个Cmos管子在建立传输的时间肯定是长的),所以setup是很容易violation的

在fast Corner的时候——关注hold的check——fast时,cell元件的delay很小,因此hold很容易出错。

3.为什么需要三种library ——需要在各种环境内正常工作

同一个芯片在各个环境下都要能工作,此时他的setup/hold在各个场景下都得满足

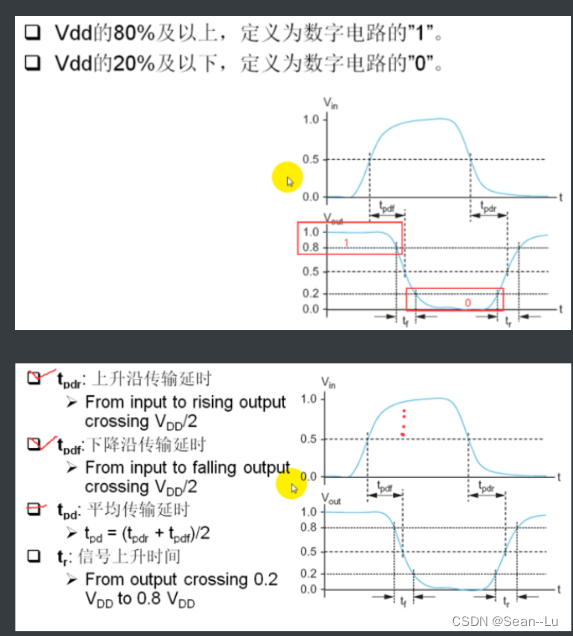

4.threshold voltage 门限电压

LVT——也有各种operation Corner。LVT——delay小,因为小电压就导通了——但 leakage 漏电级电流增大?——功耗增加?。 HVT——delay就大点。

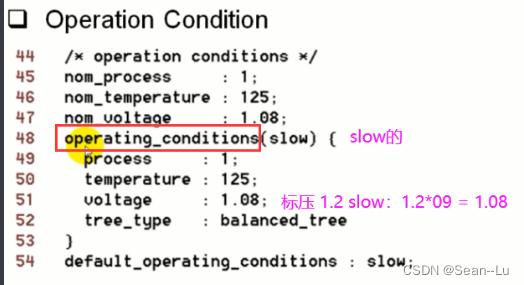

2.2运行条件

slow是延时高的情形

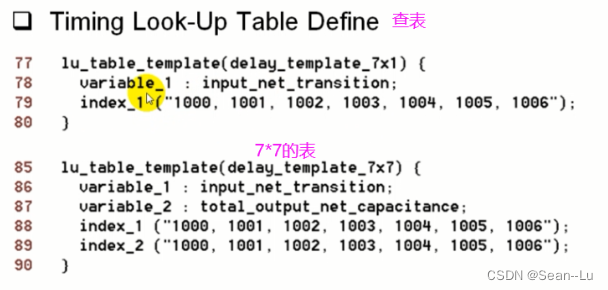

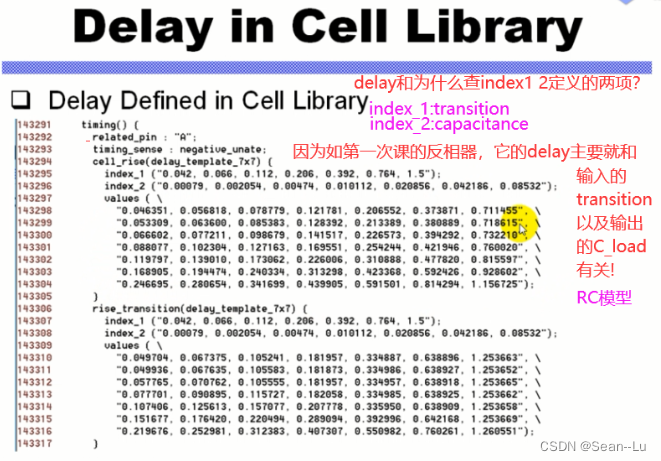

2.3延时用 Transiton传输 + capacity电容?——定义的组合查表获得

2.4cell 的delay计算——CMOS——RC模型

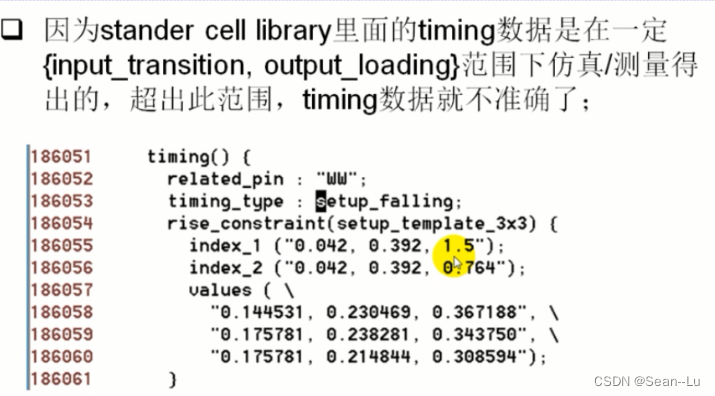

2.5时延的Look up table 定义/Power LUT 定义

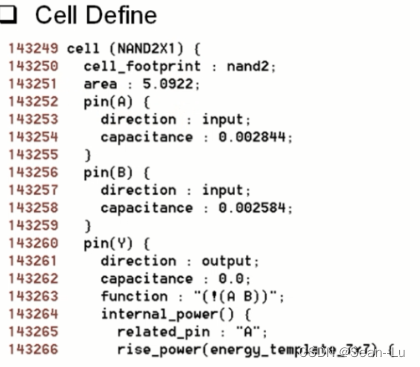

2.6 Cell元件的定义/元件延时定义

cell rise delay:输入A端变化,输出从0-1的变化的delay。 cell fall delay:

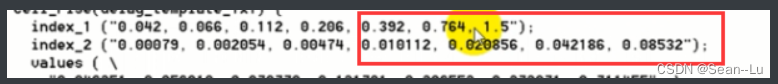

后面0.39 到 0.76 到1.5,跃变是很大的,越到后面越不准确,因此工厂也会要求尽量往下压一下,这样设计更加准确。

问fab代工厂,问提供cell library的人——maximum_trainsition maximum_capacitance 在点13的工艺上,究竟是多少合适?

2.7 总结:为什么需要DRC check

1.前提条件:前提条件——提取的参数不能大于最大的 Maximun_transition 等

2.建议:询问代工厂等,建议的工作区间

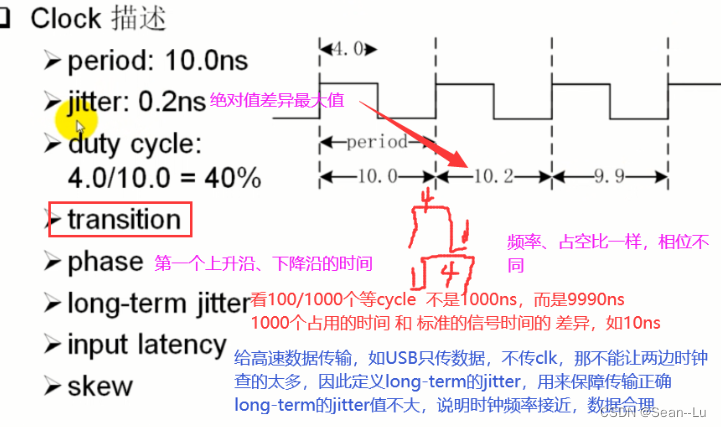

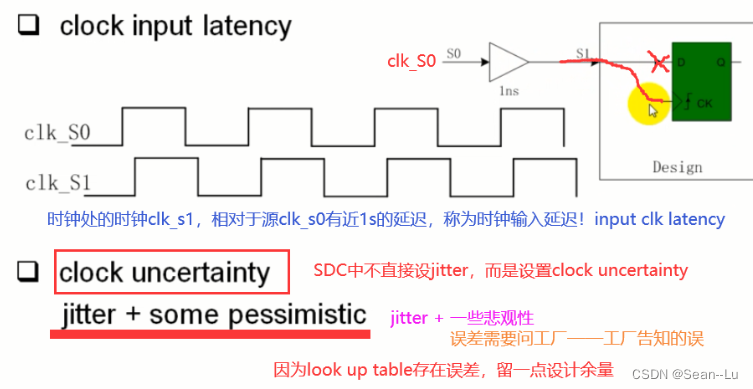

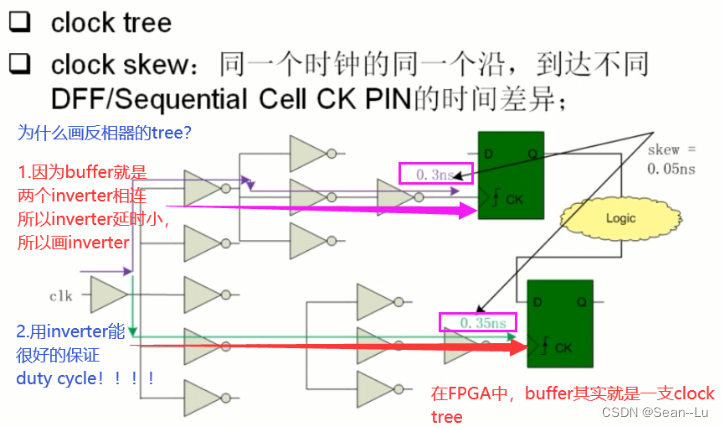

3.Clock相关概念

3.1相关概念

为什么画inverter Tree而不是buffer Tree?

1..因为buffer就是两个inverter相连所以inverter延时小,所以画inverter

2.用inverter能很好的保证duty cycle!!!!

3.2 SDC中如何定义clock——整个是tcl tickle的写法

SDC——使用tickle的脚本写的

所有的参数定义——都是根据实际情况设置的

文章详细介绍了静态时序分析(STA)的目的,包括DFF的setup/hold检查,异步复位/置位的recovery/removal需求,信号脉宽要求,时钟门的setup/hold检查,以及DRC的要求。此外,还探讨了标准元件库的不同制程Corner,时延计算和DRC检查的重要性。文章进一步阐述了时钟相关概念,如在SDC中定义clock的方法。

文章详细介绍了静态时序分析(STA)的目的,包括DFF的setup/hold检查,异步复位/置位的recovery/removal需求,信号脉宽要求,时钟门的setup/hold检查,以及DRC的要求。此外,还探讨了标准元件库的不同制程Corner,时延计算和DRC检查的重要性。文章进一步阐述了时钟相关概念,如在SDC中定义clock的方法。

8799

8799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?