工欲善其事必先利其器,高速电路的仿真离不开的就是Model Integrity仿真工具,而Model Integrity仿真用到的模型就是IBIS模型文件。使用Model Integrity不仅可以用来浏览模型,还可检查IBIS模型或DML模型(Cadence的模型格式)的语法。

在IBIS模型出现之前,人们用晶体管级的SPICE模型进行仿真,而这种仿真通常面临以下几个问题:

(1)结构化的SPICE模型只适用于元器件和网络较少的小规模系统仿真,借助这种方法设定系统的设计准则或对一条实际的网络进行最坏情况分析;

(2)得到元器件结构化的SPICE模型较困难,元器件生产厂不愿意提供包含其电路设计、制造工艺等信息的SPICE模型;

(3)各个商业版的SPICE软件彼此不兼容,一个供应商提供的SPICE模型可能在其他的SPICE仿真器上不能运行。

因此人们需要一种可被普遍接受、不涉及元器件设计制造技术、

并能准确描述元器件特性的“黑盒”式模型,IBIS因此应运而生。

IBIS模型及SPICE模型区别:

SPICE模型:

(1)电压/电流/电容等节点关系从元器件图形、材料特性得来,建立在低级数据的基础上;

(2)每个BUFFER中的元器件分别被描述/仿真;

(3)仿真速度太慢,适用于电路级的设计者;

(4)包含了详细的芯片内部设计信息。

IBIS模式:

(1)电压/电流/时间等BUFFER的节点关系建立在U-I或U-t数据曲线上;

(2)其中没有包括电路细节;

(3)仿真速度快(是SPICE仿真的25倍),适用于系统设计;

(4)不包括芯片内部的设计信息。

IBIS模型是以I/O缓冲器结构为基础的,I/O缓冲器行为模块包括封装所带来的RLC寄生参数,硅片本身的寄生电容参数,电源或地的电平钳位保护电路、缓冲器特征(门槛电压、上升沿、下降沿、高电平、低电平状态)。

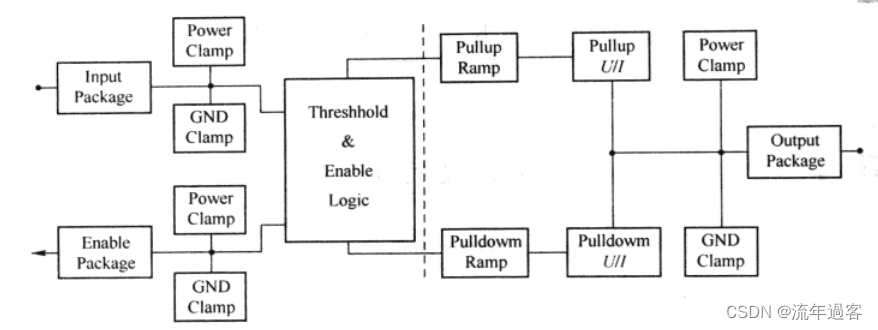

以下为IBIS模型结构图:

备注:图中虚线左边为输入模型结构,右边为输出模型结构!

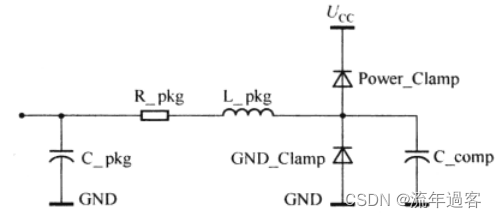

(1)输入模型结构可细化为如下图所示:

C_pkg, R_pkg, L_pkg为封装参数;

C_comp为硅片上引脚的压焊盘电容;

Power_Clamp为低端ESD结构的U-I曲线;

GND_Clamp为低端ESD结构的U-I曲线。

(注意:对输入结构模型而言,没有上下拉结构的电路)

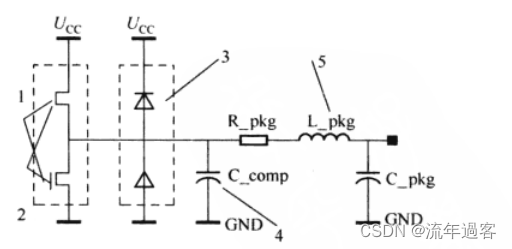

(2)输出模型结构同样可以细化为下图所示:

A、元素1为Pullup,Pulldown,包含了高电平和低电平状态的上拉、下拉U-I曲线;模拟缓冲单元被驱向低电平或高电平的U-I特性;

B、元素2为Ramp,包含了上升沿和下降沿的摆率(dU/dt),指的是输出电压从20-80%的电压输出幅度所用的时间。为了更加准确的描述上升沿和下降沿的过程,有上升沿和下降沿的U-t曲线;

C、元素3为Power/GND Clamp,包含了电源和地的钳位保护电路的U-I特性;

D、元素4为C_comp,包含了硅片本身固有的寄生电容;

E、元素5为RLC,代表封装的寄生参数特性,对元器件的所有引脚进行一个粗略的描述,可以进行进一步详细描述。

(注意:元器件中只有C_comp的描述而没有R_comp的描述,是因为硅片本身的寄生电阻影响已经包含在上下拉电路和钳位保护电路的U-I特性中了)

IBIS模型的进一步详细介绍,后续会单独出一篇,这里只做简述,下面一起来学习一下Model Integrity仿真工具。

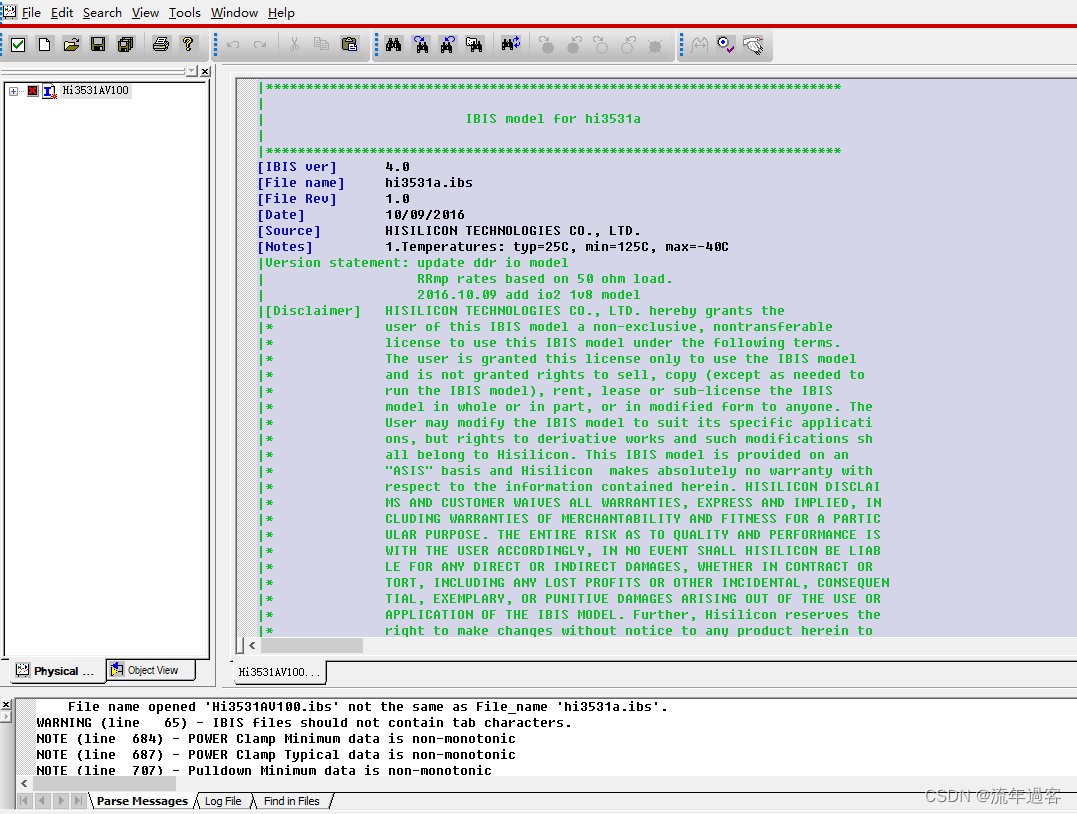

一、如下所示即为Model Integrity工具的界面:

界面介绍:

(1)左侧工作区域主要用于显示所打开的模型文件名,模型名前一般都有一些图形符号(如上图所示的红叉):

红X:表示调入的模型有语法错误;

黄√:表示调入的模型有语法警告;

绿√:表示调入的模型完全正确。

图形化的“I”表示此模型是IBIS格式,图形化的“D”表示是DML格式。

下面的“Physical”和“Object View”是用于切换模型名的显示模式。

(2)右侧一栏主要是显示模型文件的实际内容,其中:

蓝色字体是关键字;

绿色字体是注释;

黑色字体是普通文本;

红色是错误标志;

黄色为警告标志。

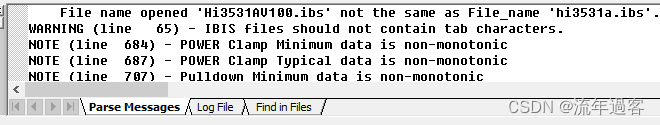

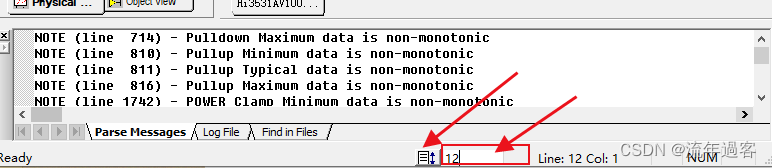

(3)下面一栏是输出窗口,显示Model Integrity各种功能、命令的结果。输出窗口有三种显示模式:

Parse Messages模式:

显示模型文件的语法分析确认过程中的错误和警告信息;

Log File模式:显示模型日志文件;

Find in Files模式:

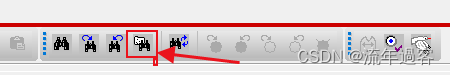

可通过搜索功能,在当前所有文件中查找某一字符串,搜索快捷键如下图:

(4)最下方的状态栏中,主要的一个功能就是快速跳转到某一行语句,例如在这里输入12,点击一下旁边的按键,即可跳转到模型语句中的第12行:

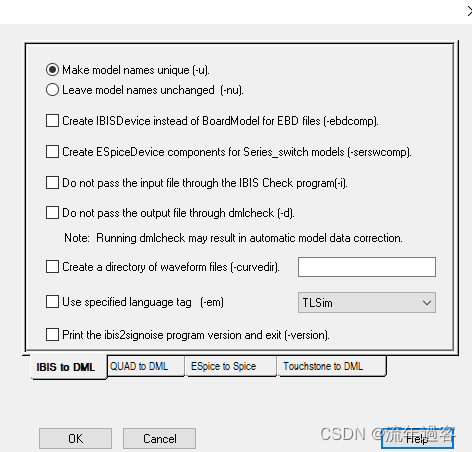

二、Model Integrity还可进行模型格式转换,支持的转换格式如下:

从IBIS格式转换到DML格式;

从Quad格式转换到DML格式;

从Espice格式转换到Spice格式。

操作如下:Tools–Translation Options,即可打开格式转换界面:

三、Model Integrity还提供了图形化接口,可以通过调入SigWave查看模型中任意IOcell的所有U-I、U-t曲线,这些波形曲线包括Pullup、Pulldown、GND_clamp、POWER_clamp、Raising Curve、Failing Curve的Type、Min、Max三种数据类型。

例如:选中任一IOcell模型,单击鼠标右键,选择“View Curve”,即可选择想要查看的曲线,SigWave窗口就弹出来了。

使用Model Integrity集成的Signoise接口即可对IOcell模型做仿真验证,用鼠标右键单击任一IOcell模型,选择“Simulate”即可对其进行仿真验证。

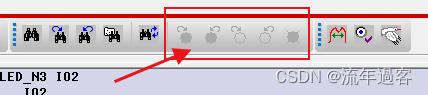

四、Model Integrity还会在调入IBIS模型时自动做语法检查,并在出错或者警告的行前打上相关标志,通过以下快捷键即可快速找到这些问题点:

这里的5个快捷键的功能依次是:

下一错误、上一错误、下一警告、上一警告、清除所有标志。

492

492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?