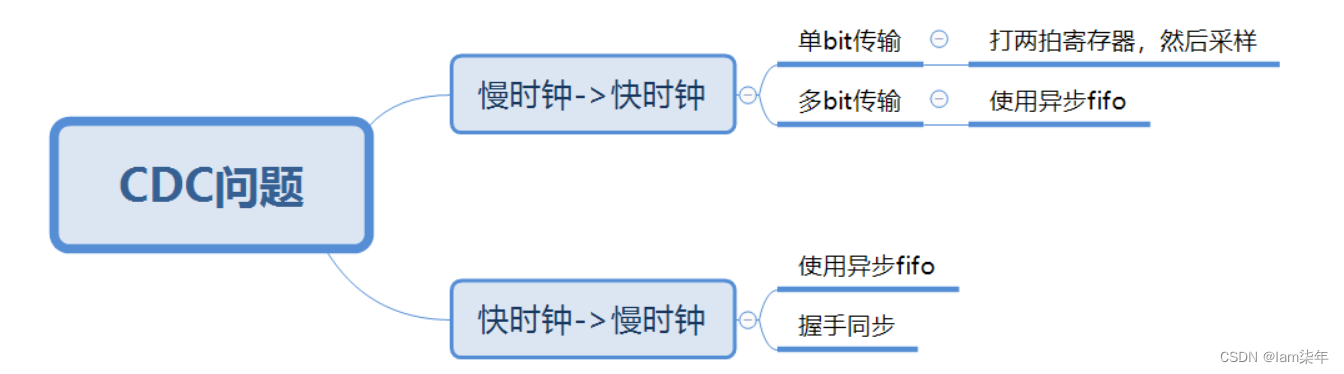

关于CDC问题小结

慢时钟到快时钟

单bit脉冲信号传递,在快时钟域打两拍后采样即可。

注意:打两拍适用于采样寄存器信号,如果是组合逻辑信号,得先在其所在的时钟域先寄存一拍,再做同步。这是因为组合逻辑信号会有毛刺,在快时钟域下采样极有肯能被采到。

module pulse_sync(src_clk, src_rst_n, src_pulse, dst_clk, dst_rst_n, dst_pulse);

input src_clk; //source clock

input src_rst_n; //source reset

input src_pulse; //source pulse in

input dst_clk; //destination clock

input dst_rst_n; //destination reset

output dst_pulse; //destination pulse out

//Internal singles

reg state_delay1;

reg state_delay2;

reg state_delay2;

wire dst_puase;

wire dst_puase_1;

wire dst_puase_2;

always@(posedge dst_clk or negedge dst_rst_n)begin

if(!dst_rst_n)begin

state_delay1 <=

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1193

1193

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?