详细说明见UG480文档第63页。

DRP全称Dynamic Reconfiguration Port,也就是动态重配置端口。

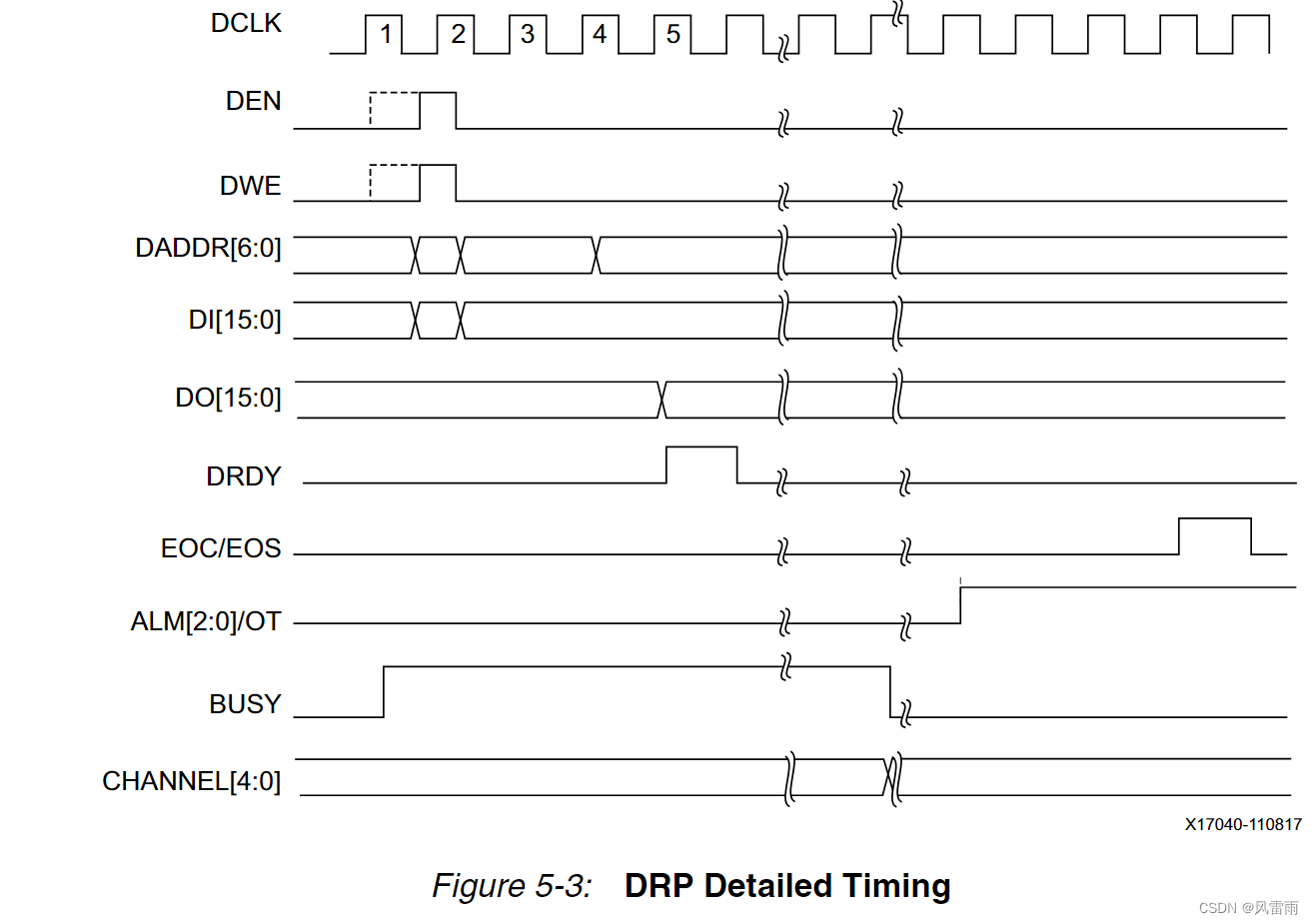

下图所示为DRP的读写时序:

DRP支持读写操作,在DEN为高电平(应该只保持一个DCLK时钟周期)的时候,在DCLK的上升沿锁存DWE(写使能)、DADDR(DRP地址)信息。

DRDY为低电平的时候才能读写DRP端口。

写操作:DEN、DWE信号为高电平(7系列要求只保持一个时钟周期的高电平)、DI、DADDR在DCL看上升沿被采集,DRDY拉高后标识数据被成功写入DRP寄存器。

读操作:DWE为低电平,读数据在DRDY为高的时候,在DO上有效输出。DRDY应该被用来抓取DO信号。

应用中要配置GTH、GTX接口的时候,就需要用到该时序,其相应的寄存器列表则在UG476的“DRP Address Map of the GTX/GTH Transceiver”部分。

XILINX DRP接口时序

于 2023-08-19 10:28:39 首次发布

本文详细解释了DRP(DynamicReconfigurationPort)的工作原理,包括DEN和DWE信号的使用、读写操作时序以及在配置GTX/GTH接口中的应用,引用了UG480和UG476文档的部分内容。

本文详细解释了DRP(DynamicReconfigurationPort)的工作原理,包括DEN和DWE信号的使用、读写操作时序以及在配置GTX/GTH接口中的应用,引用了UG480和UG476文档的部分内容。

6089

6089

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?