本文主要参考 DC WorkShop Lab2_w1152715961的博客-CSDN博客

一直以来,我都是把代码直接扔到vivado里面,从来没有考虑过它的实际综合的过程是怎么实现,这周有时间来研究一下design compiler工具的使用。

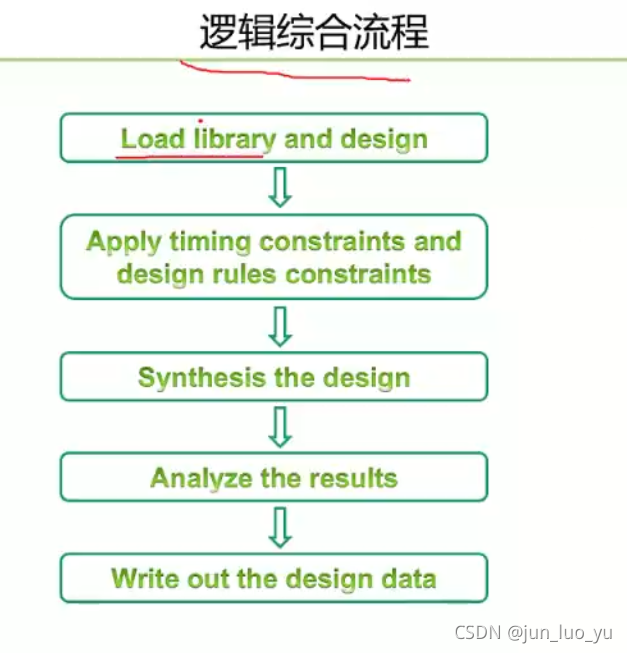

(一)原理

逻辑综合工具实际上就是将RTL代码映射到具体的工艺库上(一般由制造厂家提供),再通过添加约束信息(时序约束,线载模型,面积,功耗等,主要以tcl语言形式),对RTL代码进行逻辑综合,形成门级网表(netlists)。

一般先将VHDL/Verilog/Systemverilog转化为GTECH网表(中间网表),再映射到不同的工艺库上,生成TSMC网表。

Synthesis = Translation + Gate Mapping + Loigic Optimization

(二)一些路径的设置

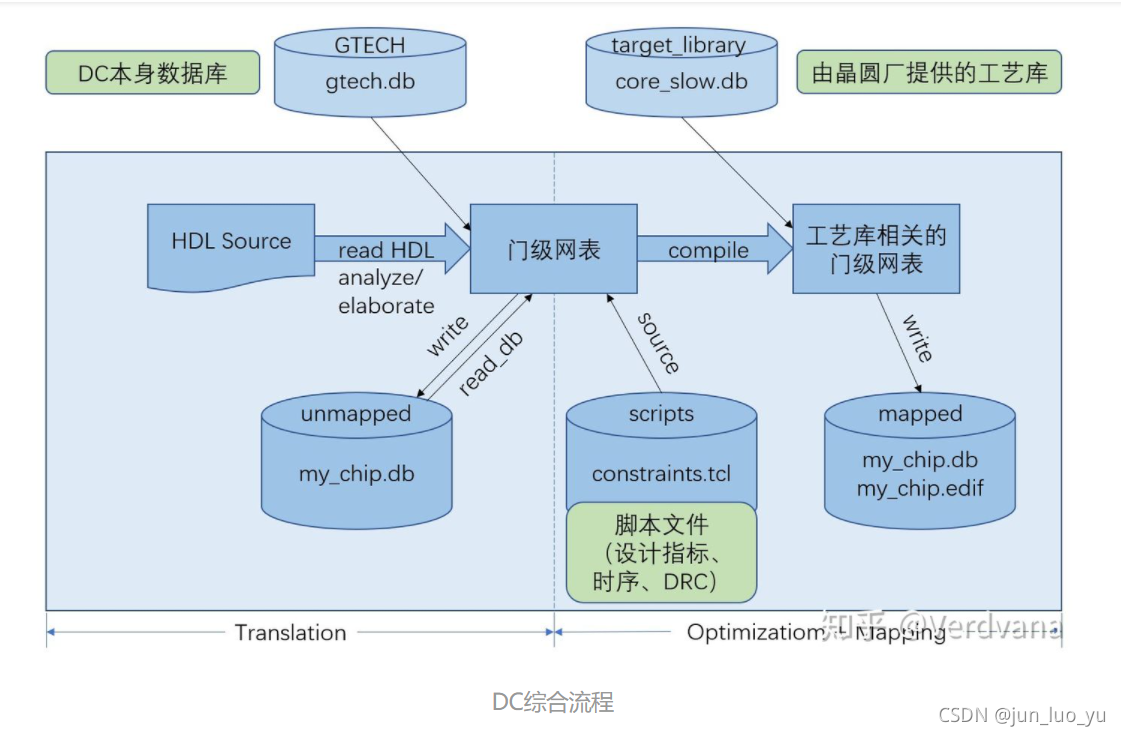

下面这张图片引用来自知乎

Target_library: 由半导体厂商提供,包含工艺技术参数和单元的功能,DC使用库里的单元构成电路。工艺库一般是.dbDE 的格式,这种格式是DC认识的一种内部文件格式;

Link_library: 设置模块或者单元电路的引用,对于所有DC可能用到的库,都需要在Link_library中进行指定,包括要使用到的IP文件。此处还要将search_path添加进来,这样才能找到.db文件;

Symbol_library: 包含工艺库中的单元图形表示的库名称;

Search_Path: 包括所有必需文件的指定路径都需要在此进行声明。

其中lib文件可以打开,工程师可以看懂。

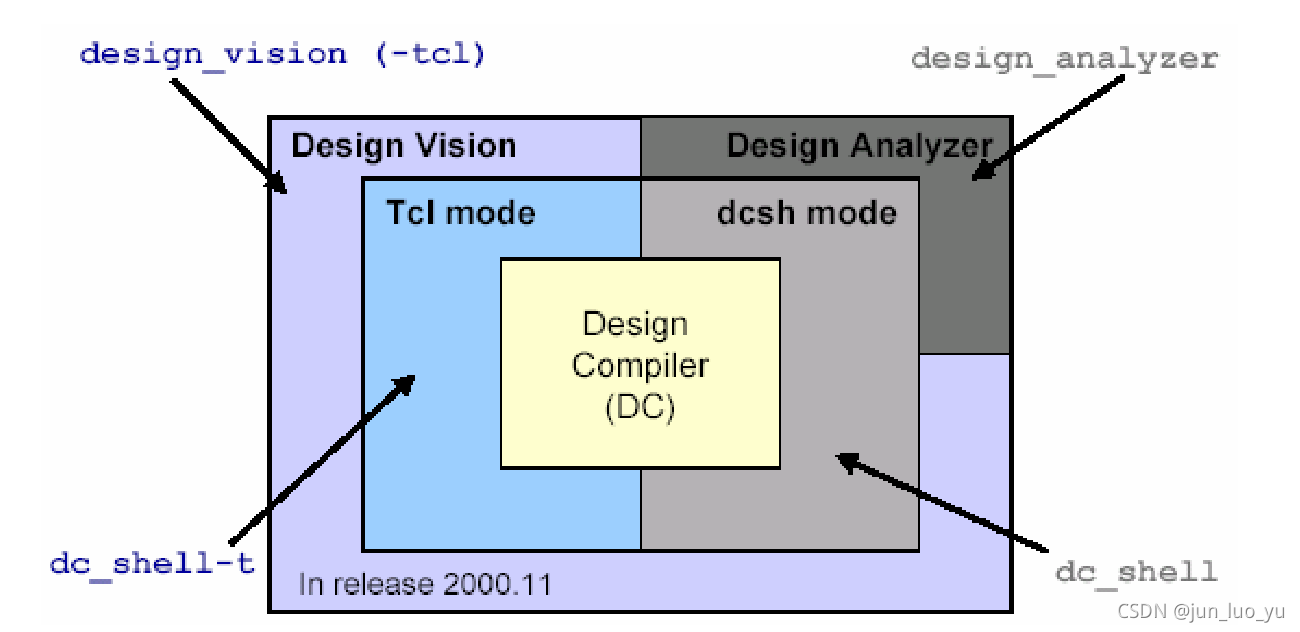

(三)DC工具的四种打开方式

| dcsh mode | dc_shell | 支持调用dcsh脚本,不支持tcl,仅支持文本界面,没有图形界面 | 可以通过dc_shell -f script方式来调用脚本 |

| design_analyzer | 对应的dc_shell格式的图形化界面,故不能调用tcl脚本 | 会产生command.log以及view_command.log来记录执行命令以及参数,会在运行中产生临时的filenames.log用于记录访问的目录,退出会自动删除。 | |

| tcl mode | dc_shell -t | dc_shell的扩展,支持tcl脚本 | 可以通过dc_shell-t -f script方式来调用脚本 |

| design_vision | 对应的dc_shell-t格式的图形化界面,故能调用tcl脚本 | 只会产生command.log的日志文件 |

其中dcsh不能调用tcl,tcl也不能调用dcsh。

//执行tcl脚本

source my.tcl

//dc执行tcl

dc_shell-t -f my.tcl

//dc执行tcl,并将输出定向到对应的log文件中

dc_shell-t -f my.tcl > my.log

//dc执行tcl,并将输出定向到对应的log文件中,并且在linux屏幕中输出

dc_shell-t -f my.tcl | tee my.log

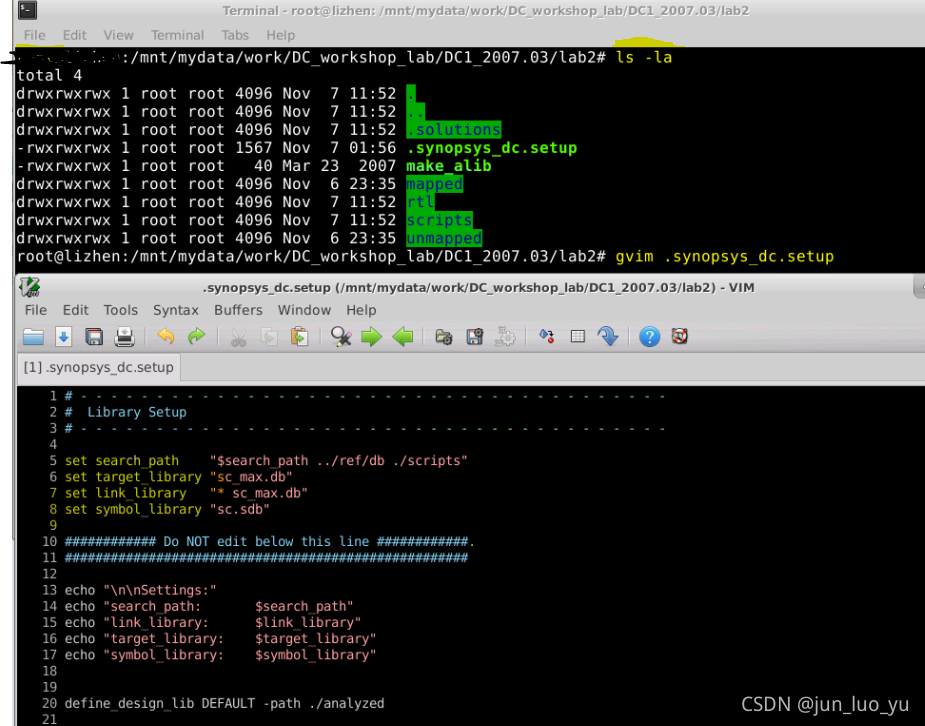

(四)lab2 2007.03

本来想跑通一个2012.06的lab1,但是因为找到的文件缺失一些东西,最后还是决定使用2007.3的lab来跑一遍试试看。这个lab的文件可以在EETOP上面找到,包括了实验文件以及对应的手册,还是写的非常详细的。

准备工作:安装DC2016版本的虚拟机,lab2的文件,DC1_200703_LG_02_setup.doc对应的手册。

Task1

flow的第一个工作是将不完整的.synopsys_dc.setup文件补齐。.synopsys_dc.setup它本身是一个隐藏文件,需要用ls -la来查看,之后去修改它对应的路径设置,包括search_path、target_library、link_library、symbol_library。我们先不关心这个.synopsys_dc.setup自己去写应该怎么写。

在link_library的设置中必须包含’*’, 表示DC在引用实例化模块或者单元电路时首先搜索已经调进DC memory的模块和单元电路,如果在link library中不包含’*’,DC就不会使用DC memory中已有的模块,因此,会出现无法匹配的模块或单元电路的警告信息(unresolved design reference)。

Task2

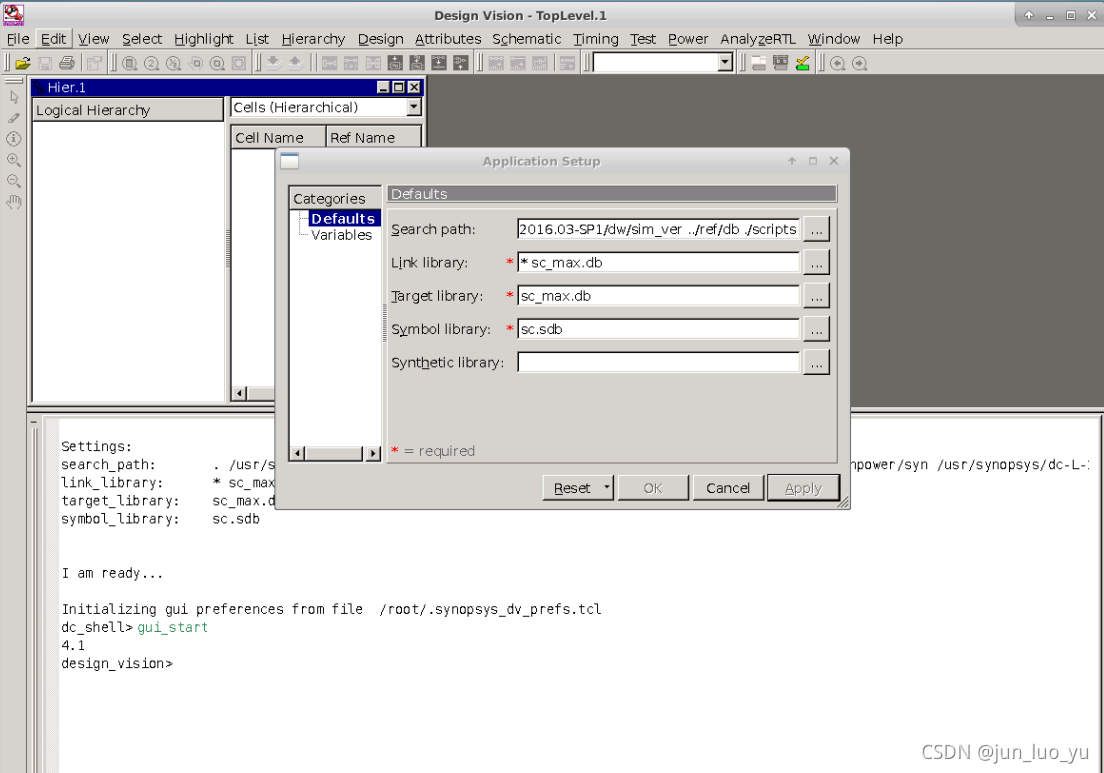

输入design_vision打开DC界面,并查看File->setup,观察路径是否正确。

//tcl查看对应的路径

printvar target_library

printvar link_library

printvar symbol_library

printvar search_path

Task3

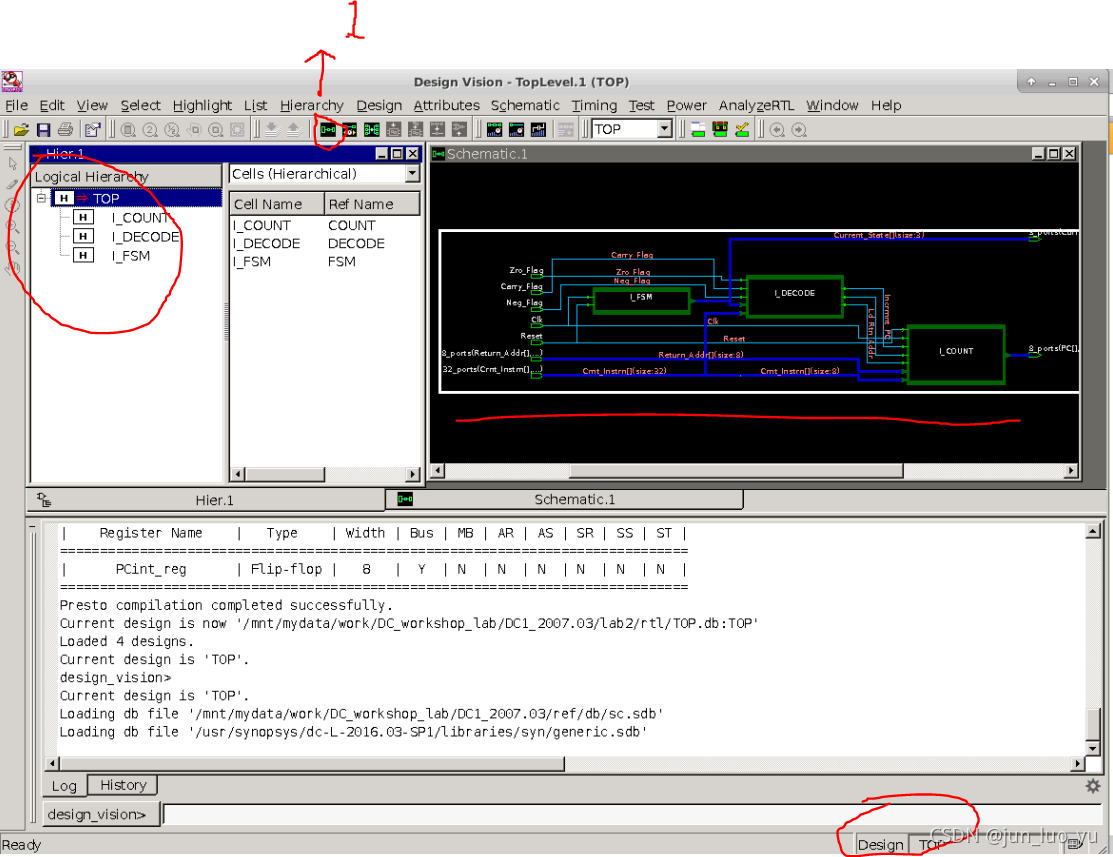

在File->read中选择TOP.vhd,选中top右下角会出现top字样。点击红色的1可以查看对应的schematic。

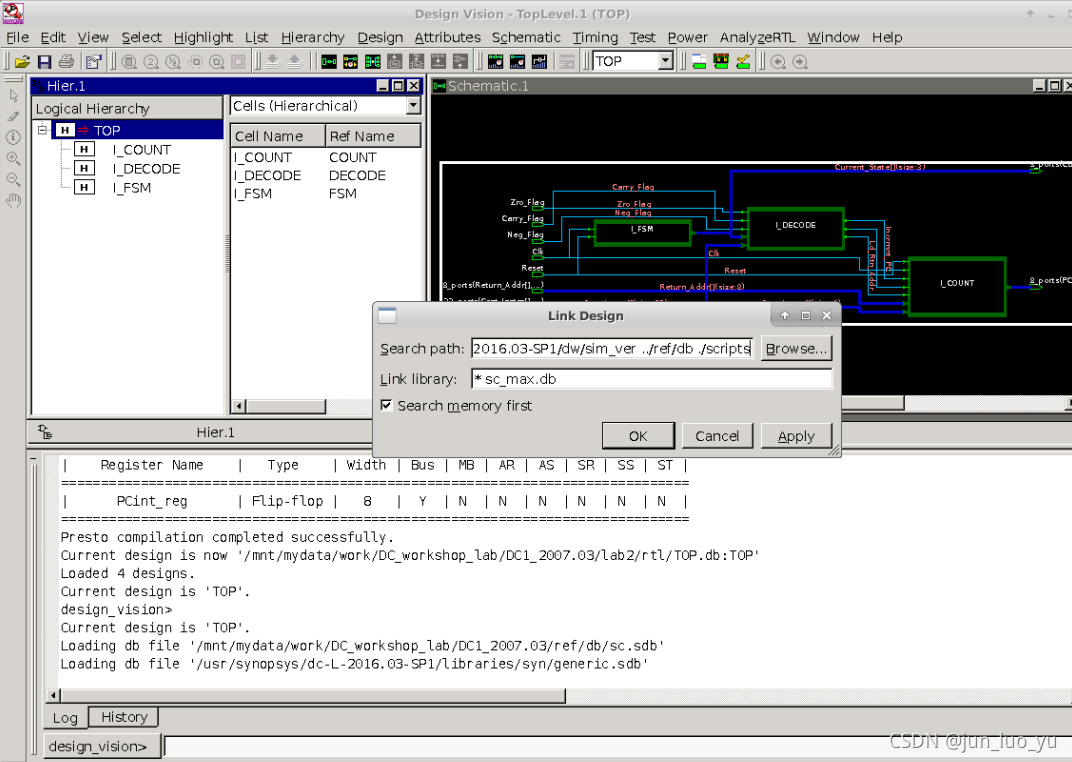

在 File->Link Design 中点击ok

//Save the unmapped design in ddc fromat,将没有映射的网表文件以ddc格式保存起来

write –hier –f ddc –out unmapped/TOP.ddc

//see a list of designs and libraries in memory,可以看到对应的design和lib清单

list_designs

list_libs

Task4

source TOP.con,这实际上就是一个约束文件。下面是TOP.con文件内容,包括了时钟约束以及线载模型的约束过程。

set lib_name cb13fs120_tsmc_max

current_design TOP

# Reset all constraints

reset_design

# Create clock object and set uncertainty

create_clock -period 2 [get_ports Clk]

set_clock_uncertainty 0.2 [get_clocks Clk]

# Set constraints on input ports

suppress_message UID-401

set_driving_cell -library $lib_name -lib_cell sdcfq1 [remove_from_collection [all_inputs] [get_ports Clk]]

set_input_delay 0.1 -max -clock Clk [remove_from_collection [all_inputs] [get_ports Clk]]

set_input_delay 1.2 -max -clock Clk [get_ports Neg_Flag]

# Set constraints on output ports

set_output_delay 1 -max -clock Clk [all_outputs]

set_load [expr [load_of $lib_name/an02d0/A1] * 15] [all_outputs]

# Set the wire load model

set_wire_load_mode top

set_wire_load_model -name 16000Task5

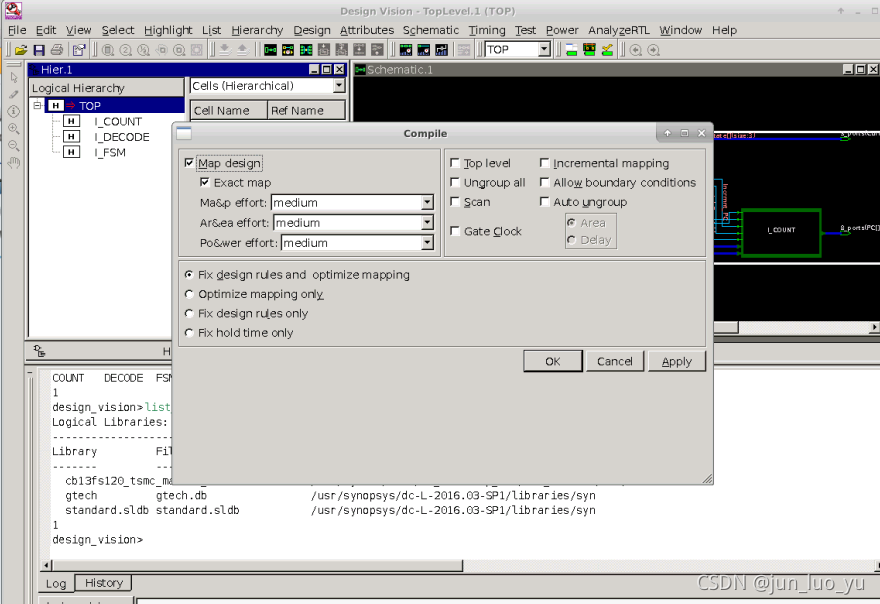

compile 编译

ultra 超级编译

执行编译的过程中有三个层次的优化过程:

(1)架构的优化(插入bufio)

(2)逻辑的优化/GTECH网表的优化(卡诺图的优化)

(3)门级优化

在满足时序约束的条件下,保证面积的最小。

gate clock 可以用来控制功耗

incremental mappping 增量映射,原理图之间可以进行跳转的过程。

auto ungroup 把模块打散掉

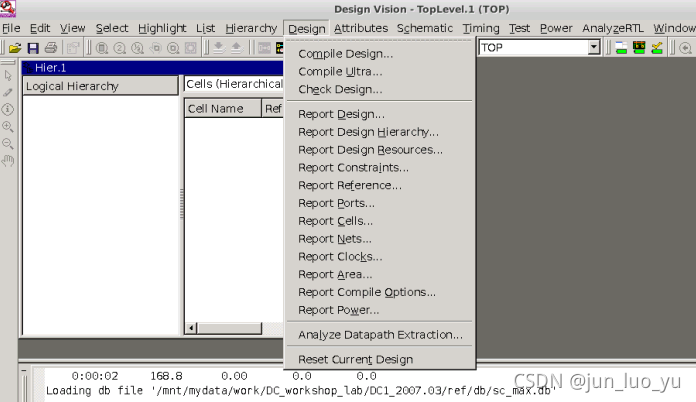

Task6

查看所有违例 report_constraint -all_violators

查看各种报告

Task7

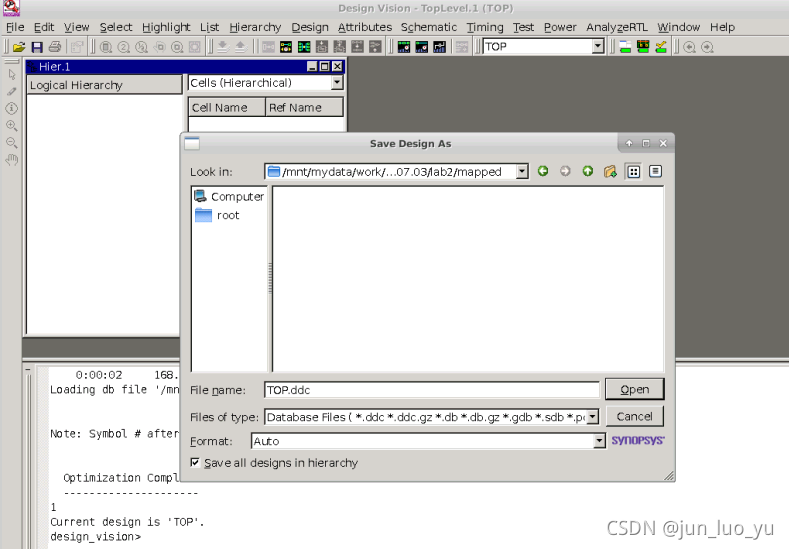

保存文件到 mapped中,仍然以ddc的格式来进行保存文件。

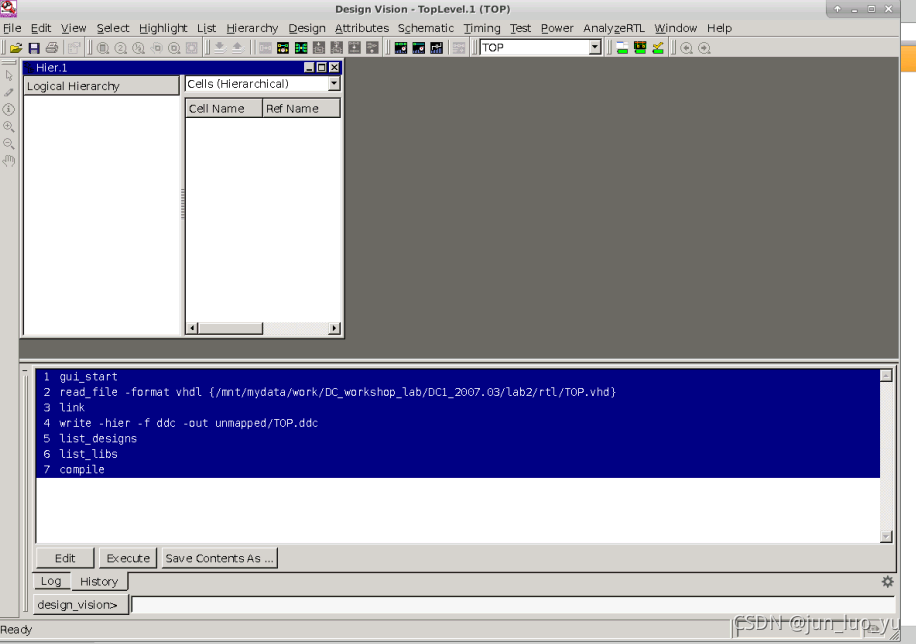

保存tcl脚本,先点击history,再鼠标全部选中,然后点击save contents as,将tcl脚本保存下来。之后可以通过 design_vision –f scripts/run_history.tcl 直接一键执行全部dc过程。

Task8

remove_design -designs 退出所有设计,然后exit退出。

本文详细介绍了逻辑综合工具DesignCompiler的工作原理、配置路径、操作方式及使用流程,包括设置库路径、使用不同模式打开工具、读取和链接设计、约束设置、编译优化以及违例检查等关键步骤,旨在帮助读者掌握如何使用DesignCompiler进行RTL到门级网表的转换和优化。

本文详细介绍了逻辑综合工具DesignCompiler的工作原理、配置路径、操作方式及使用流程,包括设置库路径、使用不同模式打开工具、读取和链接设计、约束设置、编译优化以及违例检查等关键步骤,旨在帮助读者掌握如何使用DesignCompiler进行RTL到门级网表的转换和优化。

5398

5398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?