FPGA的spi flash配置-配置模式理解

起因

现在在做的FPGA工程是基于以前的工程,其中flash配置啊什么的都没有进行过修改,之前是采用的spi x1的模式,现在新的数字版改为了spi x4的模式,所以我就认为需要修改xdc约束文件。但是在xdc文件中搜索相关引脚,发现并没有对其做任何约束和定义,所以考虑应该是FPGA固有的一些配置引脚,不需要单独定义和约束。

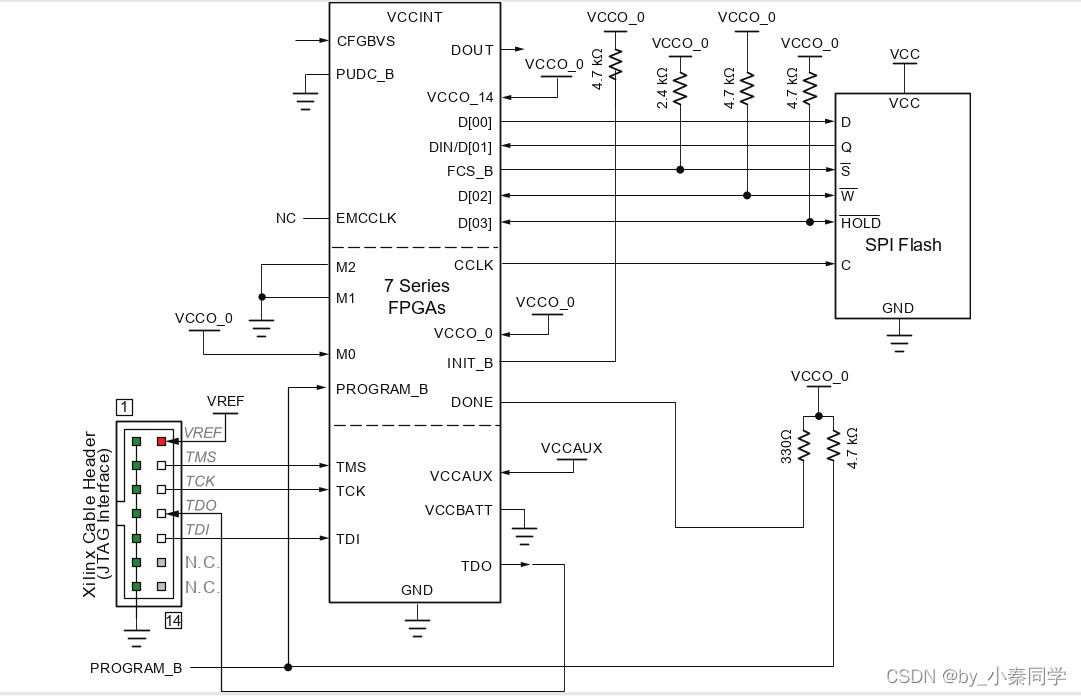

下图是vivado中官方提供的spi x4的配置电路

逻辑代码配置模式

观察图1,经过查阅官方文档,在该电路中,M0、M1、M2这3个引脚是逻辑代码配置模式选择管脚。在该模式中,M2,M1,M0为001,对应的模式为master SPI。

M[2:0]对应的配置模式表格如下表1所示

| configuration mode | M[2:0] | bus width | CCLK direction |

|---|---|---|---|

| Master Serial 主串模式 | 000 | x1 | output |

| Master SPI 主SPI | 001 | x1,x2,x4 | output |

| Master BPI 主BPI | 010 | x8,x16 | output |

| Master SelectMAP 主并模式 | 100 | x8,x16 | output |

| JTAG JTAG模式 | 101 | x1 | NOT Applicable |

| Slave SelectMAP 从并模式 | 110 | x8,x16,x32 | input |

| Slave Serial 从串模式 | 111 | x1 | inpput |

其中主从模式对应CCLK的流向。

这些配置模式对应的电路在vivado中都可以找到:tool->Edit Device Properties->configuration modes。

operties->configuration modes。

598

598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?