Timing Designer的使用学习

1 新建一个工程

在安装好Timing Designer之后(我这里使用的是Timing Designer9.103),可以找到他的应用图标,如图1.1。

图1.1

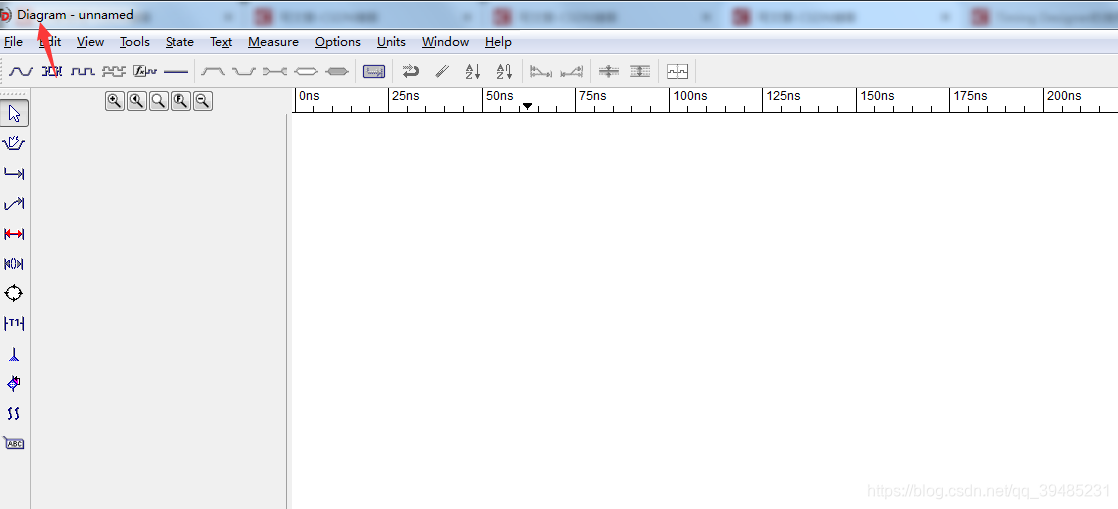

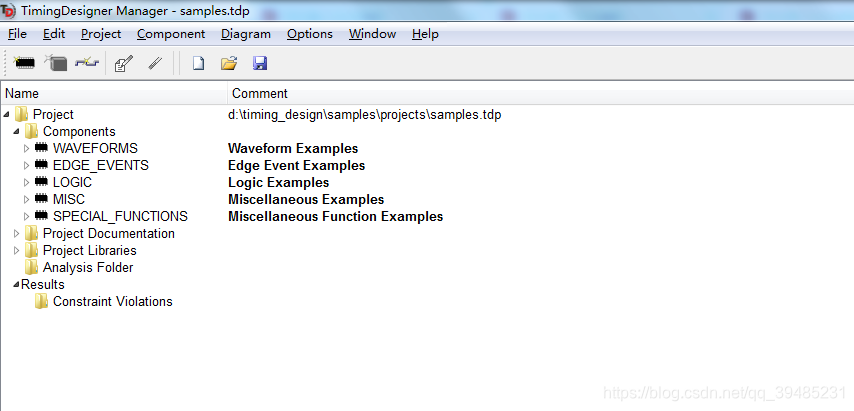

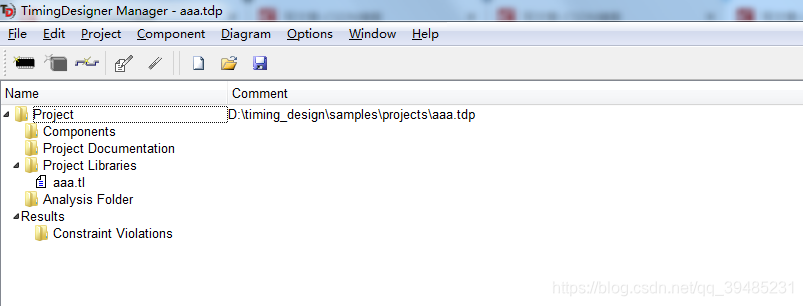

但打开软件之后出来的界面是这样,如图1.2,默认是一个Diagram的文件,并且找不到新建工程的地方。这个时候可以到软件的安装目录D:\timing_design\samples\projects,找到一个samples.tdp文件,打开他之后,出来的界面如图1.3。选择File→New,在弹窗中选择文件类型为tdp,修改文件名和保存路径,然后就能新建一个工程了,新建工程结果如图1.4。

图1.2

图1.3

图1.4

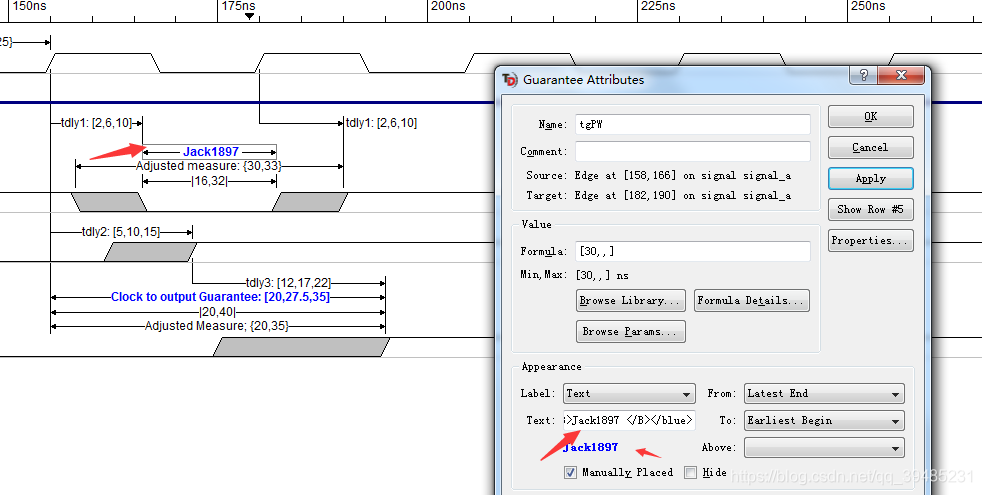

2 新建component

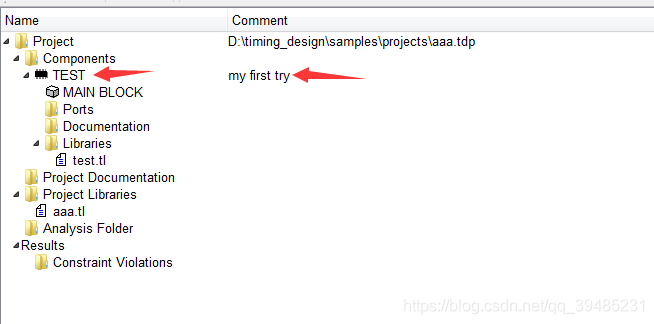

点击上图的这个新建一个component,选择create component from scratch→functional model,填写component的名字和描述,点击finish。然后就出现了如图2.1。

图2.1

鼠标放在图2.2的这个位置点击右键,选择new diagram 。

图2.2

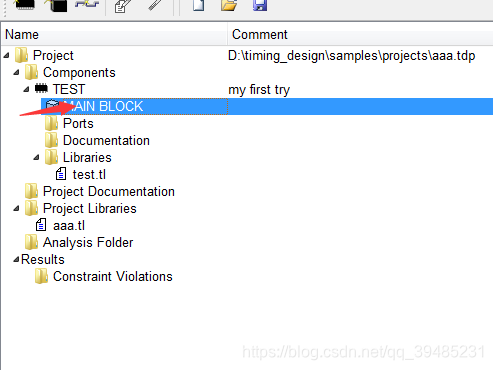

图2.3在①号标那里是选择新建的diagram放到哪个component中。假如一个工程,有多个component,每次新建diagram,都要确认对不对。

图2.3

3 画Diagram时常用功能

这部分可以参考 Timingdesigner timing designer 入门 基础 教程.

4 字体的设置

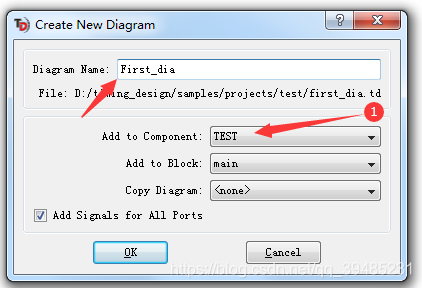

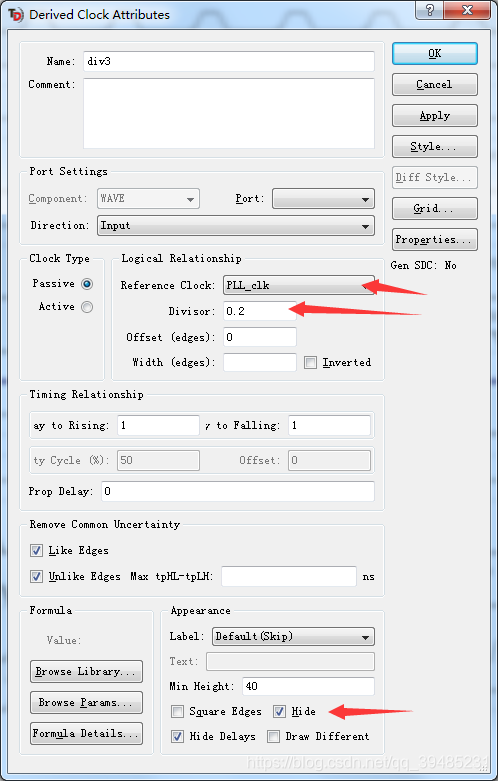

diagram中字体默认都是黑色且不加粗,假如要改变颜色输入:< blue > Jack1897 < /blue >,然后Jack1897就会变成蓝色,假如想要其他的颜色就把blue改成red或者其他的颜色。效果图如图4.1,

图4.1

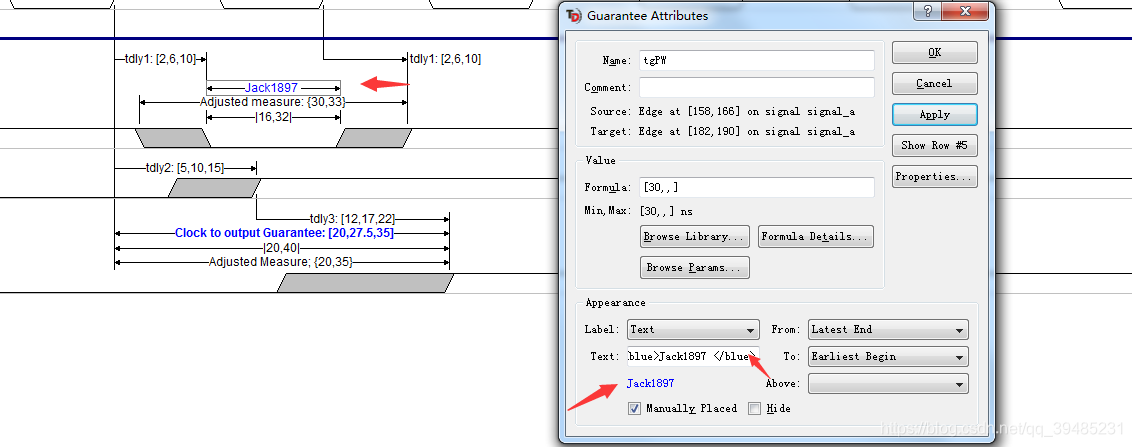

字体加粗也会经常用到,我在上一步的基础上继续操作,加粗的话< blue > < B > Jack1897 < /B > < /blue >,效果如图4.2。

图4.2

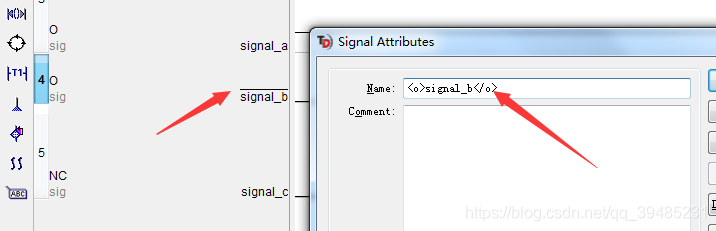

在信号中,我们还会遇到一些低电平有效的信号,这些信号为了一目了然都会在信号名上面加一个横杠,加横杠的话输入:< o > Jack1897 < /o >,效果如图4.3

图4.3

5 时钟信号的添加

通过上面那篇参考文章中添加时钟信号的方法,大家添加的时钟边沿不是垂直的,假如想要它垂直可以把图5.1的那个勾选上。

图5.1

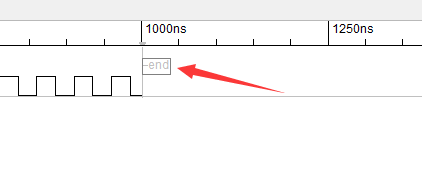

大家添加时钟之后会发现,默认的时钟结束时刻比较短,假如需要增加时间可以双击图5.2这个end,在time那一栏修改时间。

图5.2

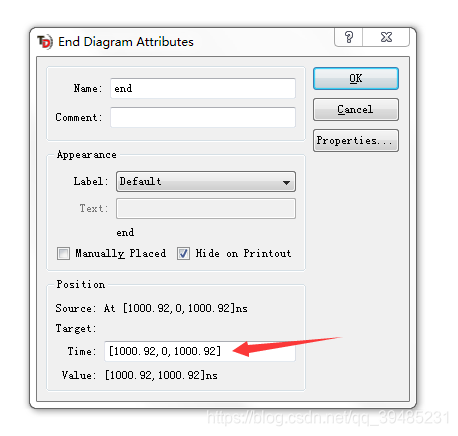

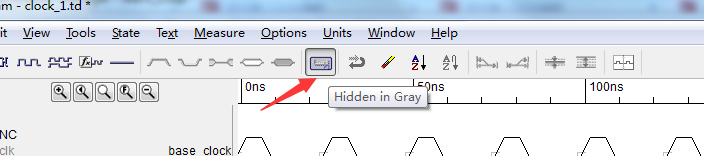

在时钟分频时,有时候分频系数是一个分数,不能用一个有限位数的数来表示,比如5/3。这个时候我们可以先设置一个5倍频信号作为中间信号,然后再对这个信号3分频。具体操作如下:我们单击add derived clock,选择我们的基准时钟PLL_clk,divisor:0.2表示的是5倍频,因为是中间信号,可以把下面的Hide 勾选上,其他的参数根据需要进行设置。在勾选上Hide后,图中会看不到这个信号,假如需要看到他,单击工具栏的Hidden in gray。

下一步再新建一个add derived clock,不过要把参考时钟改为上一步新建的那个5倍频信号,divisor填入3,其他地方根据需要进行设置。这个时候就获得了一个精确分频的5/3的时钟了。

6 可展开的总线信号

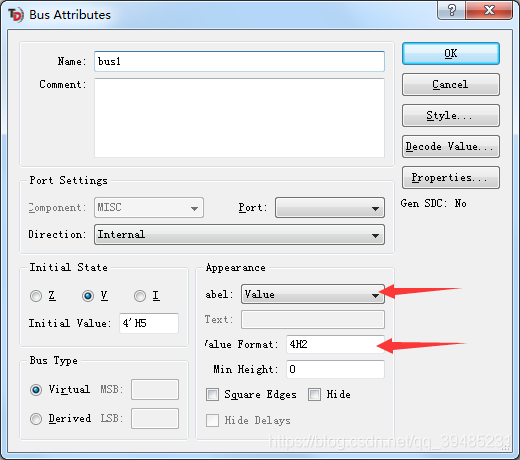

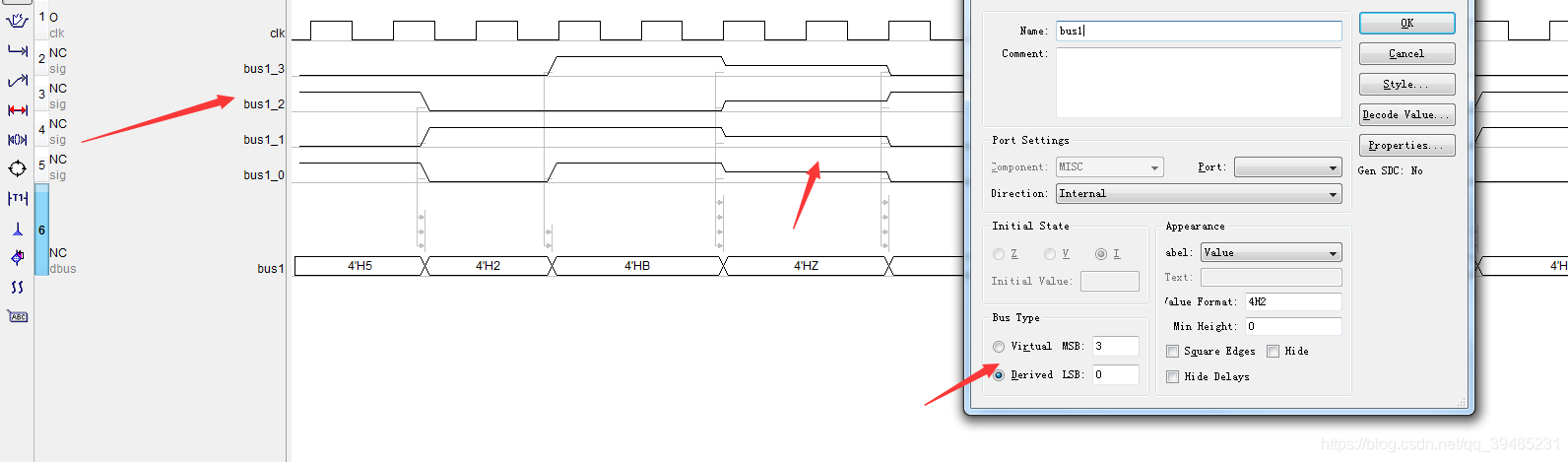

首先新建一个图6.1这样设置的总线信号,大家的4H2那个默认是不能修改的,一定要把上面的改为value。虽然默认写的是default(value),但我们还是要手动选择value。

图6.1

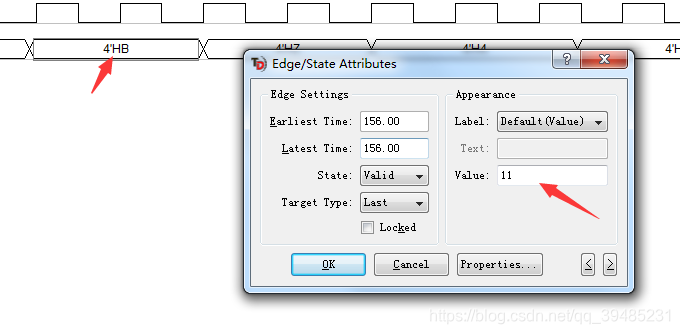

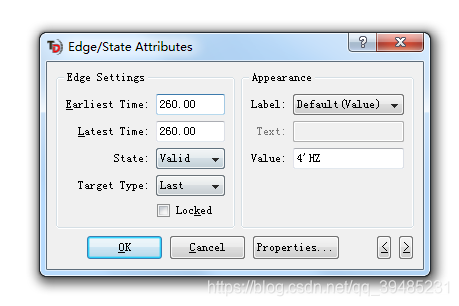

我们在为总线信号赋值时,假如想要4’HB,我们在value那里输入11,而不能输入B。假如要赋值高阻态,那么输入4’HZ。如图6.2所示

图6.2

下一步修改刚才新建的总线信号的属性,将刚才的virtual改为derived,然后LSB输入0,MSB输入3,这两个值根据我们数据的位宽来设置。然后可以看到图中自己多出了4个信号,正好是总线信号的各个位展开,刚才赋值的高阻态也能正常展开。假如我们一开始就选择derived,也是可以生成4路展开信号,但是发现无法给总线信号赋值,所以我们先在virtual下给总线赋初值,再用derived展开

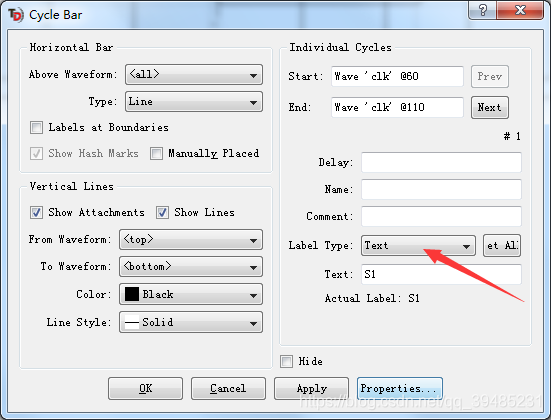

7 Cycle Bar信号的使用

在tool中找到cycle boundary,这个就是cycle bar。然后单击需要添加cycle bar的信号或者时钟边沿,添加完之后,双击添加好的cycle bar修改他的属性。这里主要讲一下他的Label type的修改,一般是设置为text,在下面的框中输入命名,之后所有的cycle bar都会自动改名,每次自加1,对于其他想要改名的地方可以同样用这个方法。cycle bar其他的属性可以根据需要修改。

因为同类的cycle bar自动同步属性,所以每次通过tool→cycle boundary添加的cycle bar都会按照同样的属性来同步。假如需要添加不同类的cycle bar可以通过tool→add cycle bar来完成。

先写到这里,有空再继续写

4171

4171

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?