一、毛刺产生的原因

信号在 IC/FPGA 器件中通过逻辑单元连线时,是存在延时的。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作环境等有关。因此,信号在器件中传输的时候,所需要的时间是不能精确估计的,当多路信号同时发生跳变的瞬间,就产生了“竞争冒险”。

信号由于经由不同路径传输达到某一汇合点的时间有先有后的现象,就称之为竞争,英文名Race;由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险,英文名Hazard或者Risk。有竞争不一定有冒险,但出现了冒险就一定存在竞争。发生冒险时往往会出现一些不正确的尖峰信号,这些尖峰信号就是“毛刺”。

毛刺是数字电路设计中的棘手问题,如果毛刺刚好被采样到,那么电路的逻辑就有可能出现错误。它会影响电路工作的稳定性、可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

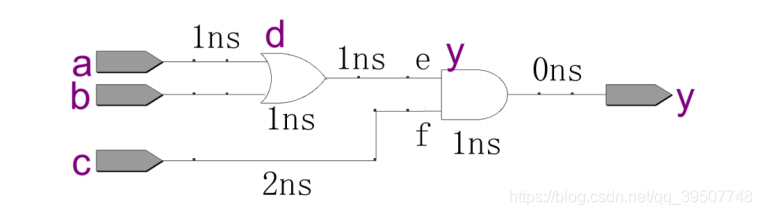

首先我们先来看下毛刺是如何产生的。下图是一个简单的组合逻辑电路,由一个或门和一个与门构成,输入信号是 a、b 和 c,输出信号是 y。

从图中,我们可以假设或门电路的延迟是 1ns,路径延迟也有时间,c 到 y 门电路的延迟是 2ns, a 到 d 门电路的延迟是 1ns,那么我们可以画出一个时序图如下:

本文详细探讨了数字电路中毛刺产生的原因,解释了竞争冒险的概念,并提供了多种消除毛刺的方法,包括同步电路设计、信号延时、状态机控制、组合逻辑输出加寄存器以及格雷码计数器的应用。通过实例分析,阐述了如何通过加寄存器有效去除组合逻辑中的毛刺问题。

本文详细探讨了数字电路中毛刺产生的原因,解释了竞争冒险的概念,并提供了多种消除毛刺的方法,包括同步电路设计、信号延时、状态机控制、组合逻辑输出加寄存器以及格雷码计数器的应用。通过实例分析,阐述了如何通过加寄存器有效去除组合逻辑中的毛刺问题。

订阅专栏 解锁全文

订阅专栏 解锁全文

1699

1699

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?