文章目录

概要

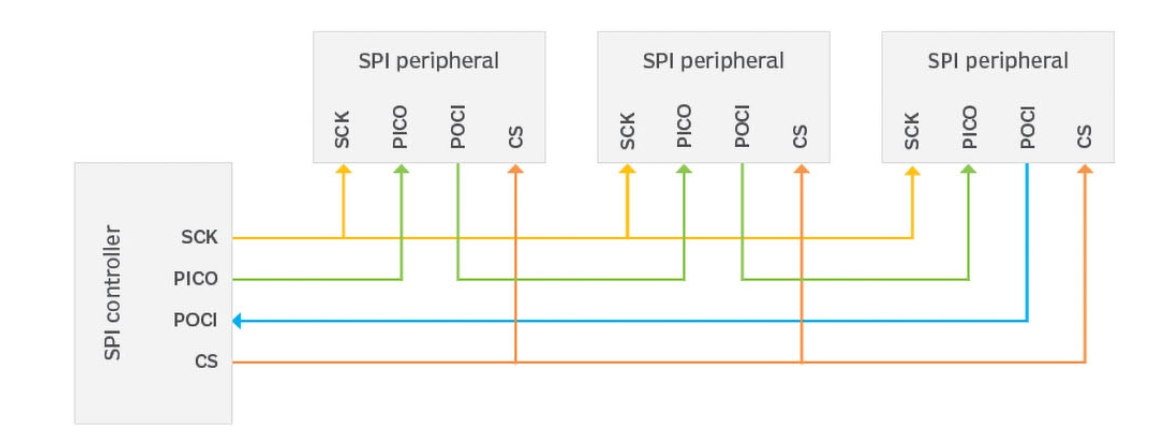

在 SPI(Serial Peripheral Interface,串行外设接口)通信中,菊花链模式(Daisy-Chain Mode) 是一种通过 “级联串联” 多个从设备(如 ADC、传感器、移位寄存器等)来共享同一组 SPI 总线引脚的拓扑结构。其核心优势是大幅减少主设备(如 MCU、FPGA)的引脚占用—— 无论级联多少个从设备,主设备仅需使用 SCLK(串行时钟)、MOSI(主发从收)、MISO(主收从发)3 根核心信号线(部分场景可省略 MOSI 或 MISO),仅需额外增加少量片选信号(甚至无需增加),特别适合多通道数据采集(如多通道 ADC)、多传感器监测等需大量外设扩展的场景。

一、菊花链模式的核心原理

SPI 菊花链的本质是利用 “移位寄存器级联” 实现数据的 “串行传递”:

每个从设备内部集成一个移位寄存器(通常与数据输入 / 输出端口绑定),主设备发送的串行数据(通过 MOSI)首先进入第一个从设备的移位寄存器,在 SCLK 时钟的驱动下,数据会逐位 “传递” 到下一个从设备的移位寄存器,直至所有从设备的移位寄存器都被数据填充;而从设备的反馈数据(如 ADC 的采样值)则通过 MISO 线反向串联,从最后一个从设备开始,逐位传递回主设备。

整个过程类似 “流水线”,所有从设备共享同一组 SCLK 和数据总线,无需为每个从设备单独分配片选(CS)信号(或仅需 1 个全局 CS),从而实现 “少引脚控制多设备”。

二、关键硬件连接与信号定义

以 “1 个主设备(如 MCU)+ 3 个 ADC 从设备(如 AD7689,12 位 ADC)” 的多通道数据采集系统为例,硬件连接如下表所示:

三、数据传输流程(以多通道 ADC 采样为例)

假设每个 ADC 的采样数据为 12 位,主设备需一次性读取 3 个 ADC 的采样值(共 36 位数据),流程分为 “指令发送” 和 “数据回读” 两个阶段,均由 SCLK 同步驱动:

1. 阶段 1:主设备发送控制指令(MOSI 方向)

主设备拉低全局 CS(使能所有 ADC),并生成 SCLK 时钟;

主设备通过 MOSI 向第一个 ADC(ADC1) 发送控制指令(如 “启动采样 + 读取数据” 指令,假设指令长度为 8 位);

在 SCLK 的每一个时钟沿,ADC1 的移位寄存器将输入的指令逐位 “推” 到其 DOUT 端,传递给 ADC2 的 DIN 端;

同理,ADC2 的移位寄存器再将指令逐位传递给 ADC3 的 DIN 端;

当指令发送完成(8 个 SCLK 周期后),所有 ADC 均通过级联链路接收到相同的控制指令,同步启动采样(或进入数据准备状态)。

2. 阶段 2:主设备回读多通道数据(MISO 方向)

指令发送完成后,ADC1、ADC2、ADC3 分别将各自的 12 位采样值存入内部移位寄存器;

主设备继续生成 SCLK 时钟(共需 36 个时钟周期,对应 3 个 ADC×12 位数据);

最后一个 ADC(ADC3) 首先将其 12 位采样值通过 DOUT 端逐位输出到主设备的 MISO;

当 ADC3 的数据传递完成(12 个 SCLK 周期),ADC2 的 12 位数据开始通过 ADC3 的移位寄存器(已空)传递到 MISO;

最后,ADC1 的 12 位数据通过 ADC2、ADC3 的移位寄存器传递到 MISO;

主设备在 MISO 端逐位接收 36 位数据,并按 “ADC3→ADC2→ADC1” 的顺序解析出每个 ADC 的采样值;

数据回读完成后,主设备拉高 CS,结束本次通信。

关键特点:数据回读的顺序与设备级联顺序相反(最后一个设备的数据先回传),RTL 或驱动设计中需注意数据位的顺序对齐。

四、菊花链模式的优势与局限性

1. 核心优势(为何适合多通道数据采集)

极致节省引脚:主设备仅需 3-4 根线(SCLK、MOSI、MISO、CS)即可控制 N 个从设备,相比 “每个从设备单独分配 CS” 的并行模式(需 3+N 根线),引脚占用呈指数级减少,尤其适合 FPGA/MCU 等引脚资源紧张的场景。

同步性好:所有从设备共享同一 SCLK 和 CS,可实现严格的同步操作(如多通道 ADC 同时采样),避免因多 CS 信号延迟导致的采样时差,适合对同步性要求高的系统(如工业检测、电力采样)。

布线简单:仅需串联从设备的 DIN/DOUT,无需为每个设备单独拉通到主设备,简化 PCB 布线(尤其多设备时)。

2. 局限性(设计需注意的问题)

数据传输延迟增加:数据需逐位通过所有从设备,总延迟 = 单个设备延迟 × 设备数量 + 传输线延迟,不适合超高速(如吉比特级)通信场景。

容错性差:若某一个从设备故障(如 DIN/DOUT 短路),会导致整个菊花链链路中断,所有后续设备无法通信,需在设计中增加故障检测机制(如超时重传、数据校验)。

数据位宽受限:总传输数据量 = 单个设备数据位宽 × 设备数量,需主设备的移位寄存器或接收缓冲区支持足够的位宽(如 3 个 16 位 ADC 需主设备支持 48 位接收),或分批次传输。

五、典型应用场景

菊花链模式因 “少引脚、高同步” 的特点,广泛应用于需多通道并行采集或控制的场景:

多通道 ADC 数据采集:如工业自动化中的温度 / 压力采集(需 8-16 路 ADC)、电力系统的多相电流 / 电压采样;

多传感器串联:如 SPI 接口的加速度计、陀螺仪组成的惯性测量单元(IMU),或多个光学传感器的图像数据拼接;

移位寄存器扩展:如 74HC595(SPI 移位寄存器)级联控制多组 LED 灯、继电器,实现 “少引脚控制多外设”。

六、RTL 设计关键注意事项(以 FPGA 为例)

若在 FPGA 中实现 SPI 菊花链的主设备控制,需重点关注以下几点:

时钟同步:SCLK 的频率需匹配所有从设备的最高支持频率(取所有设备的最小值),避免因时钟过快导致数据采样错误;

数据位序对齐:明确从设备的 “高位先传(MSB First)” 或 “低位先传(LSB First)” 配置,确保主设备发送 / 接收的位序与从设备一致;

延迟补偿:若从设备间的传输线较长(如超过 10cm),需考虑信号延迟,可在 SCLK 边缘增加采样延迟(如使用触发器打拍),避免亚稳态;

数据校验:为提升可靠性,可在每个从设备的数据包后增加 CRC 校验位或奇偶校验位,主设备接收后校验数据正确性,错误时触发重传。

总结

SPI 菊花链模式是 “以时间换空间” 的典型设计 —— 通过增加数据传输的串行延迟,换取主设备引脚资源的极大节省,尤其适合多通道数据采集等对引脚限制严格、同步性要求高的场景。在实际设计中,需平衡 “传输速度” 与 “引脚成本”,并通过同步控制、数据校验等手段规避链路延迟和容错性问题,确保系统稳定运行。

3800

3800

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?