1. AXI总线特征

axi总线可以连接CPU的cache和其他外设,比如内存等。内存是从属设备,它接受信号,并驱动ready信号;主从设备都会驱动data信号,总线仲裁器只看request和grant信号,而忽略所有的其他信号。

详情参考:AXI学习笔记-11.AXI总线结构2.AXI接口时序3.数据结构4.传输特性 - 云+社区 - 腾讯云

1.1 数据传输特征

(1) AXI总线有5个通道,分别为写请求、写数据、写响应、读请求、读响应,通道之间存在依赖关系

(2) 单通道内的事务存在顺序关系,详细参见2.4节

1.2 写事务和读事务的过程

对于总线上的设备来说,一个写过程为:master发出写请求,则slave接收写请求并发出写响应,master接收写响应,然后发出写数据,接着slave接收写数据;

一个读过程为:master发出读请求,则slave接收读请求并发出读响应,然后master接收读响应

2. 协议内容

2.1 五种通道

2.2 valid和ready的握手机制

无论是写事务还是读事务,通信的双方都可分为发送方和接收方(与master和slave概念区分,二者都可以是发送方和接收方),而其中承担握手机制的主要是valid和ready信号(二者均是高电平有效)。

发送方置高valid时:表示发送方已经将地址,数据,控制信息准备就绪,并保持在总线上。

接收方置高ready时:表示接收方已经做好接收地址,数据和控制信息的准备。

当双方的valid和ready信号同时为高时,在时钟的上升沿完成一次数据传输。所有数据传输完毕后,双方同时置低自己的信号。

注意:

- ready信号只由接收方自身决定,当然编程时可综合考虑发送方的valid信号。

具体时序图可见:AXI总线协议时序_yundanfengqing_nuc的专栏-CSDN博客_axi时序

2.3 突发传输机制

参考链接1:ARM系列 -- AXI(三)

在xxburst=INCR模式下,每次传输的数据是 <ax_len>+1 个 <size>大小的数据传输,其中有效字节为<strb>索引号的部分。

2.4 事务序

AXI支持事务的乱序和顺序处理,可以将并行操作事务,从而提升系统性能。

2.4.1 顺序

不同ID的多个请求事务,返回事务可以乱序完成

2.4.2 乱序

同一ID的多个请求事务,返回事务必须按顺序完成

2.4.3 outstanding

AXI的outstanding指同时在总线上处理的最大事务量,要求master和slave都支持。

3. AXI总线主要信号定义

重要信号定义

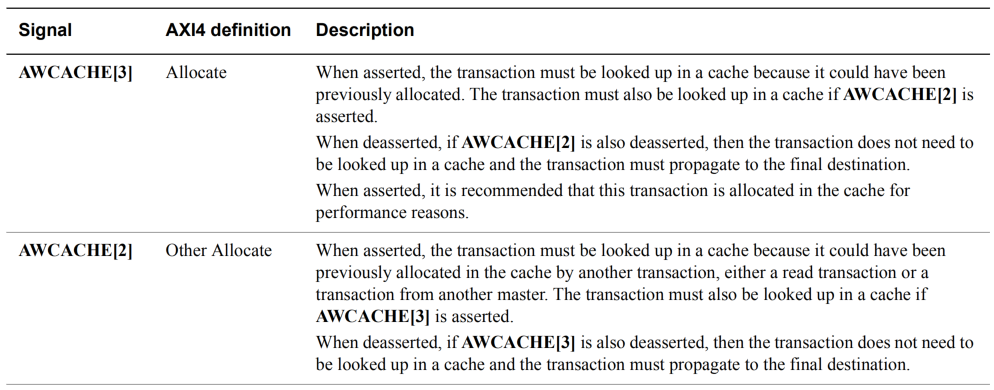

axcache的字段定义和使用

参考链接:深入 AXI4 总线(四)传输事务属性(draft) - 知乎

AWCACHE[3] 信号置高表示本主机先前的写事务可能已经将该位置上的数据缓冲于CPU下的cache中,首先在 cache 中查找对应表项。当 AWCACHE[3] 信号置低,但 AWCACHE[2] 置高时,该位置上的数据可能因为其他主机的操作、或者本机的读事务缓存于 cache 中,同样需要首先查找 cache。

同样,ARCACHE[3]信号拉高表示该地址的数据可能被其他主机的操作、或者两外一个主设备的写事务缓存于cache中,首先要到cache中查找该地址的数据,如果ARCACHE[2]同样拉高,也必须查询cache,如果ARCACHE[2]拉低,则不需要到cache中查询

信号list

以master的信号为例,包括主动发出和被动接收的信号:

| aw_id[n: 0] | 输出 | 写请求标识号 |

| aw_addr[m: 0] | 输出 | 写请求地址 |

| aw_len[3: 0] | 输出 | 写请求数据长度 |

| aw_size[2: 0] | 输出 | 写请求数据宽度 |

| aw_burst[1: 0] | 输出 | 写请求类型 |

| aw_valid | 输出 | 写请求有效信号 |

| aw_ready | 输入 | 写请求接受准备好信号 |

| id[n: 0] | 输出 | 写数据标识号,与aw_id对应 |

| w_data[j: 0] | 输出 | 写数据 |

| w_strb[k: 0] | 输出 | 写数据屏蔽信号,1位对应8个数据位 |

| w_valid | 输出 | 写数据有效信号 |

| w_ready | 输入 | 写数据接受准备好信号 |

| 写回复:针对整个写数据的操作,而不是写某个数据的单独操作 | ||

| d[n: 0] | 输入 | 写响应标识号,与aw_id对应 |

| b_resp[1: 0] | 输入 | 写响应状态 |

| b_valid | 输入 | 写响应有效信号 |

| b_ready | 输出 | 写响应接受准备好信号 |

| _id[n: 0] | 输出 | 读请求标识号 |

| ar_addr[m: 0] | 输出 | 读请求地址 |

| ar_len[3: 0] | 输出 | 读请求数据长度 |

| ar_size[2: 0] | 输出 | 读请求数据宽度 |

| ar_burst[1: 0] | 输出 | 读请求类型 |

| ar_valid | 输出 | 读请求有效信号 |

| ar_ready | 输入 | 读请求接受准备好信号 |

| id[n: 0] | 输入 | 读响应标识号,与ar_id对应 |

| r_data[j: 0] | 输入 | 读的数据 |

| r_resp[1: 0] | 输入 | 读响应状态 |

| r_valid | 输入 | 读响应有效信号 |

| r_ready | 输出 | 读响应接受准备好信号 |

1189

1189

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?