1.1 ACE 简介

学习 ACE 协议之前首先要对 cache 有一个充分的了解,因此关于 cache 部分不做说明。

ACE(AXI Coherency Extensions) 作为 amba 总线中的一种,是一种用于高性能系统-on-Chip(SoC)的协议。可以提供缓存一致性、扩展性、低延迟和高带宽,以及与其他AXI协议兼容设备的互操作性。它为系统提供了一种灵活而强大的互联和数据交换方式。

1.2 协议概述

ACE 的常用版本有:ACE4、ACE5、ACE4-Lite、ACE5-Lite 等

ACE 协议是基于 AXI4 协议,增加了 cache 的硬件一致性。

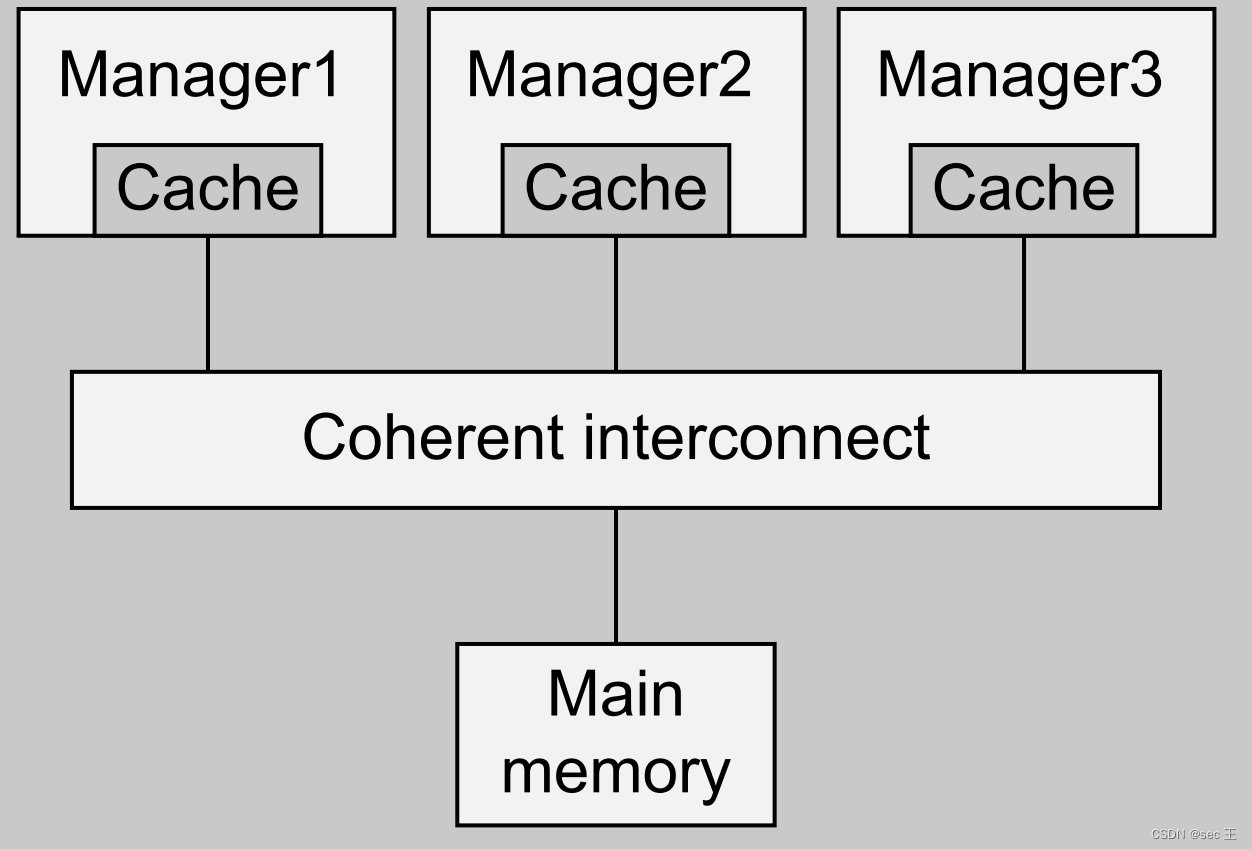

1.2.1 一致性模型

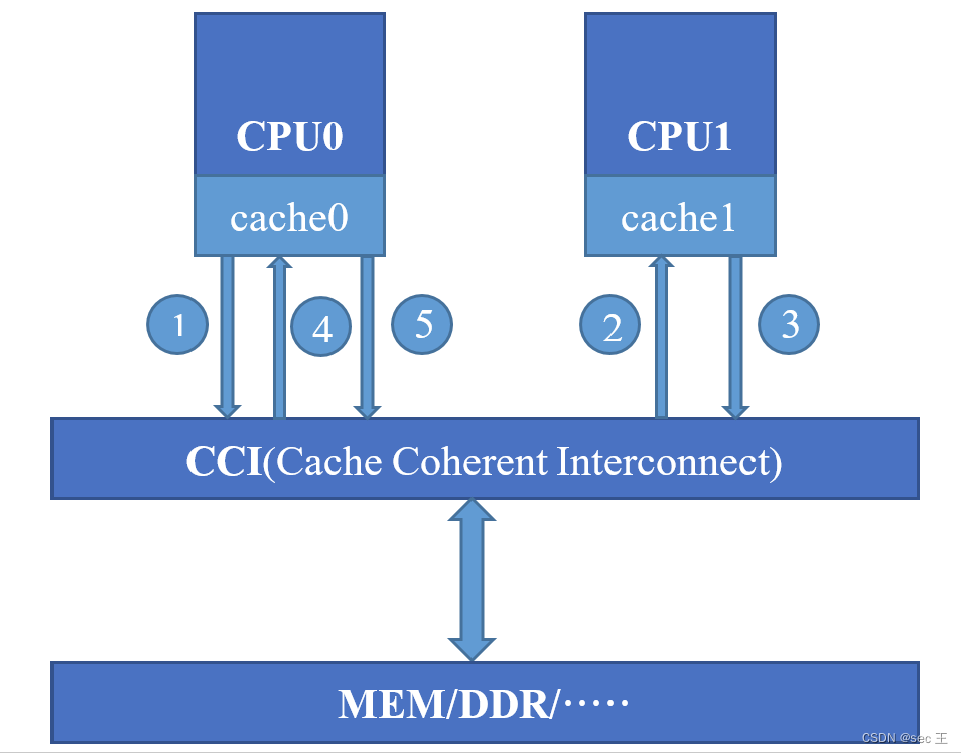

上图显示了一个基于“三个拥有本地缓存(cache)的 master 组件”的一致性系统模型,ACE一致性协议通过 master 在写操作时,操作的 cache line 只存在于一个 master 的缓存中,以此来确保所有 master 在任何地址都能观察到正确的数据值。读操作时,所有 master 可以为自己的本地缓存获取数据的新副本,允许不同 master 存在地址相同的 cache line。

简单来说,对于main_memory 中的数据,所有的 mst 都可以其拿出来一部分放在自己的 cache 中,方便多次读取(如果其它 mst.cache 中有的话,先在其它 mst 的 cache 中读取),但是写入的话,在写入之前,清理掉其它 mst.cache 上对应的 cache line,再写数据到自己的 cache 中。这样这几个 mst 的读写就不会出现冲突了,保证数据的准确、一致性。

Coherent interconnnect(cci) 是 ACE 协议一致性的管理器,通过接收 ace 的传输,根据当前各个 mst 中 cache 的状态、tr 的内容等来判断:是否要向其它被监控的 mst 上发出 snoop_tr、是否向 slave 发出 axi 信号等。

cache line 被定义为若干按顺序字节寻址的本地内存的缓存副本,第一个地址与 cache line 的总大小对齐。

Main Memory(主存) 不需要一直保持是最新的,当 cache line 的副本不再保存在任何缓存之前更新主存即可。虽然不是必需的,但在缓存副本仍然存在的情况下更新主存也是可以的。

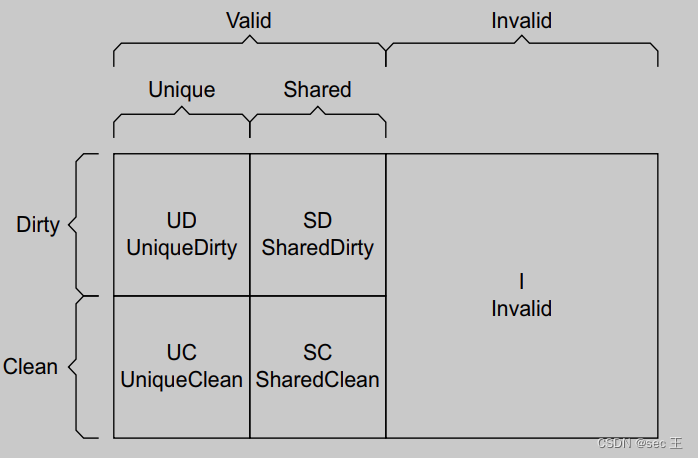

1.2.2 cache line 的状态模型

1.3 端口概述

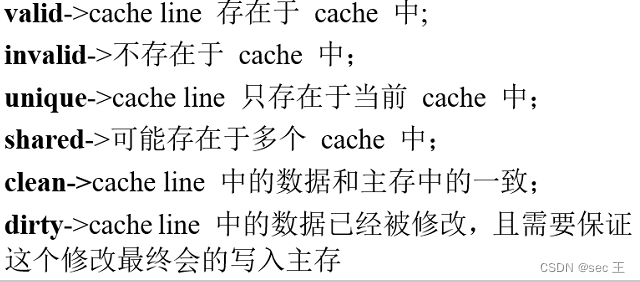

相比于 AXI4,ACE4 在其基础上增加了一些端口。

1.3.1 基于 axi4 各个通道上增加的端口

写数据通道和写相应通道没有增加端口,a*domain 涉及域的概念,a*snoop 表示是“一致性类型”,a*bar 表示 barrier 访问的标志,这些后边会后详细说明。

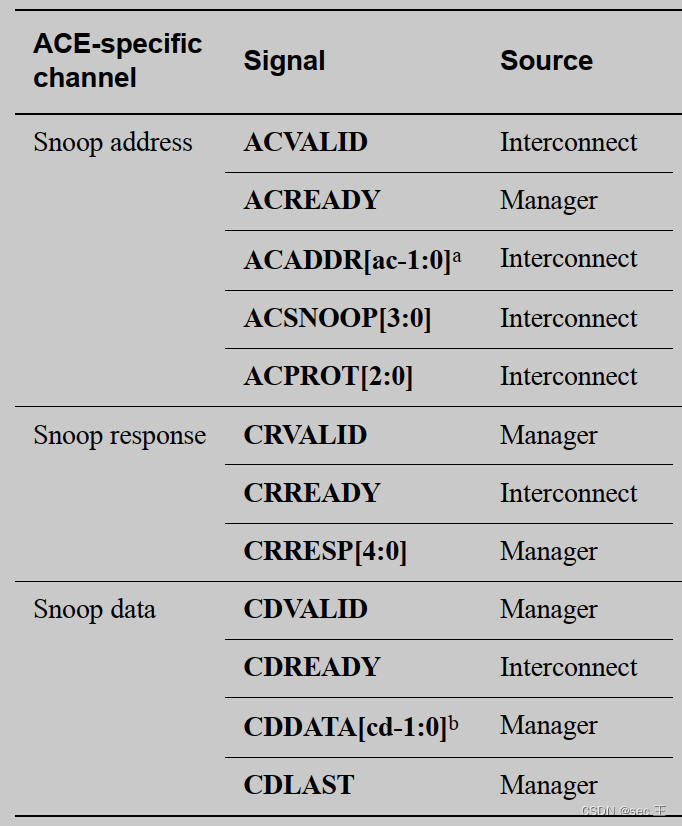

1.3.2 相较 AXI4 增加的通道

ACE 相较于 AXI4,增加了 3 条 snoop_tr 的 channel(通道):

· Snoop address channel(AC)

· Snoop data channel(CD)

· Snoop response channel(CR)

AC channel 由 cci 发出,包含了 snoop_tr 的地址和相关控制信息。

CD channel 由被监控的 mst 发出,snoop_tr 中是否包含此 channel,由 snoop_tr 的类型、mst 中 cache line 的状态决定。

CR channel 由被监控的 mst 发出,是 mst 对 snoop_tr 相应,crresp 反应了是否有数据返回、是否 error、访问的 cache line 是否是 unique 的、是否保留 cache line、是否将 dirty 属性传递给初始 mst。

具体增加的端口如下图:

1.3.3 响应信号

ACE 协议增加了两个响应信号 RACK、WACK,由初始 mst 发出,用于向 cci 表示一个 ACE 的 tranction 完成。

1.3.4 ACE 读操作的一般流程

读取数据的一般方法:

1. 发起端 mst 通过 RA(Read_Addr) 通道发出读 tr 到 cci ;

2. cci 将读命令发送给其他 mst.cache,通过其他 mst 返回的 resp 信号,判断在其他 mst.cache 中是否存在相同地址的 cache line;

3. 如果 resp 表示存在对应的 cache line,对应的 mst会通过 CD channel传递出 data;

4.1 如果有 mst.cache 传出了 data,CCI 会将 data 通过 RD 通道传递给发起端的 cache;

4.2 如果其他 mst.cache 中没有对应的 cache line,那么:

a. CCI 会将发起端发出的读 tr 发送到主存;

b. 读数据会像标准 tr 一样,返回到发起端的 cache;

5. 发起端 cpu 收到读数据完成后,会向 CCI 返回一个 RACK 信号。

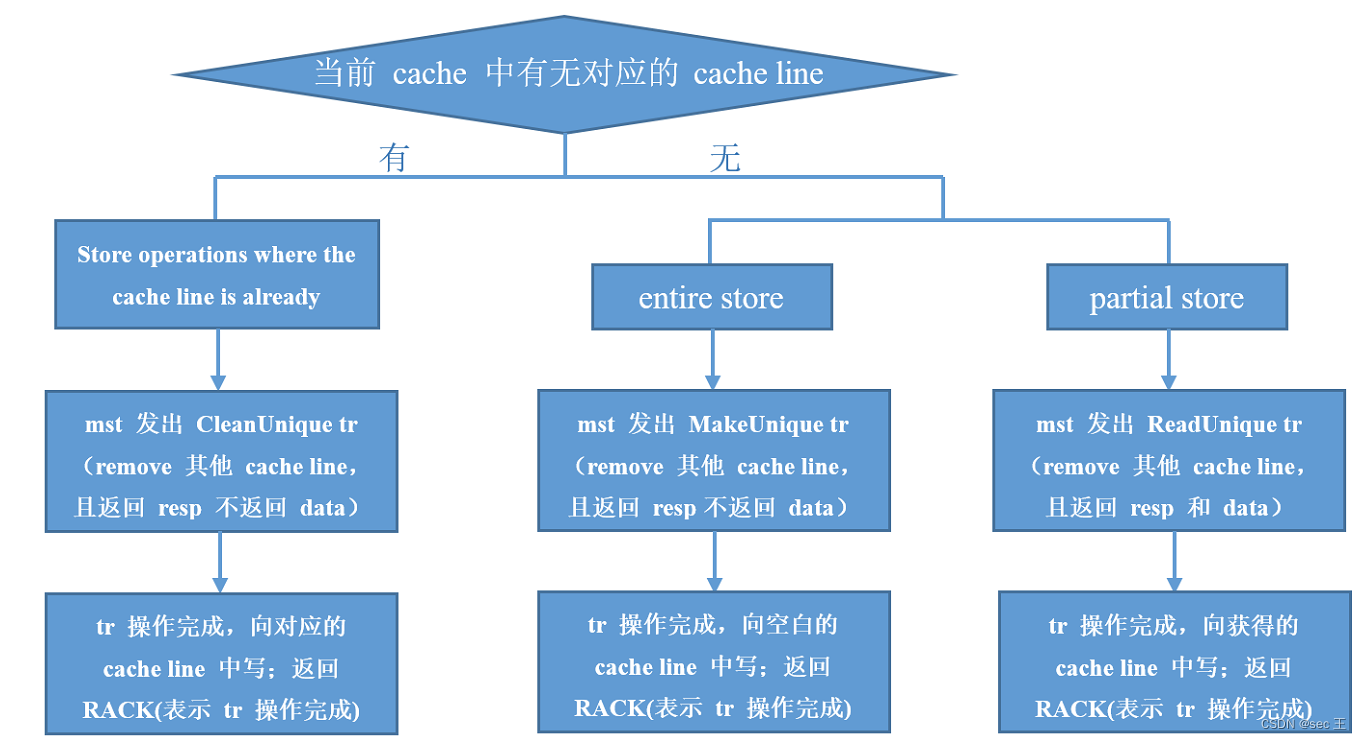

1.3.5 ACE 写操作的一般流程

在进行写操作之前,如果发起端 mst 有对应的 cache line 副本:

1. 发起端 master 通过 RA(Read_Addr) 通道发出 CleanUnique tr 来请求作为唯一副本; (这个 tr 不会返回 cache line 的数据,只会返回一个 resp,用于清理其它 mst.cache 中对应的 cache line)

2. CCI 通过 AC(Snoop_Addr) 通道向其他 cache 发出 snoop_tr。被监控的 mst 会在 CR(Snoop_Resp) 通道返回 resp 来表示:

① 对应的 cache line 已经被移除了;

② 是否有 dirty 状态的 cache line 需要被写入主内存;

3. 如果有 2.②的情况,dirty 属性的 cache line 会通过 CD(Snoop_Data) 通道发送到 CCI 中,然后 CCI 会将这个 dirty 属性的 cache line写入主存,并且这个 cache line 会被清理;

4. CCI 将 resp 信号返回到发起端的 cache,(只返回的 resp,不返回 data)

5. 发起端 mst 完成对 cache 的写操作;并发出 RACK ,用来表示 CleanUnique tr 的操作完成。

在进行写操作之前,如果发起端 mst 没有对应的 cache line 副本,写部分 cache line :

1. 发起端 mst 要先获取对应的 cache line,然后通过 RA channel 向其他 CCI 发送 ReadUnique tr,用来删除其他 cache 中对应地址的 cache line;

2. CCI 将地址通过的 AC channel 传递给其他 cache;

3. 如果其他 mst 有对应地址的 cache line,那么它会向 CCI 返回以下数据:

① 通过 CR 通道返回一个响应信号,表示存在对应的 cache line,并且已经删除;

② 通过 CD 通道返回对应的 data;

4. CCI 会通过 RD 通道向发起端的 mst 返回 resp 和 data 信号;(如果没有其他 cache 响应,就向主存获取 cache line 参数)

5. 发起端的 mst 写完对应 cache line 之后,会发出 RACK 信号到 CCI,表示已经获取 cache line 完成。

在进行写操作之前,如果发起端 mst 没有对应的 cache line 副本,写完整 cache line(burst 的总 size 大小等于一个 cache line 的大小):

1. 发起端的 cache 通过向 CCI 发送 MakeUnique tr,使其他 mst 中对应地址的 cache line 无效;

2. CCI 通过 AC 通道传递 MakeUnique tr 对应的 snoop_tr;

3. 如果其他 mst 中有对应的 cache line,那么它会通过 CR 通道向 CCI 返回 resp,表示对应的 cache line 已经被删除;

4. CCI 通过 RD 通道将步骤3 的 resp 发送给发起端 mst。(这里只传递了 resp,没有 data)

5. 发起端 mst 进行写操作,并发出一个 RACK 信号,表示之前的 MakeUnique tr 步骤完成。(这里的写,是直接在空的,或者 invalid cache line 中,写入对应的数据,写之前不需要获取 cache line)

覆盖写操作: 如果两个 mst 试图同时对同一个 cache line 写操作,CCI 将确定事务发生的顺序。此处使用约定: ·M1 是 CCI 选择的先执行的组件; ·M2 是 CCI 选择的后执行的组件;

1. M1 执行正常的写操作(如上)

2. M2 通过它的 snoop_tr 获取 M1的写操作,然后根据覆盖写操作时自身缓存中有无对应 cache line和发出的写操作类型进行以下操作之一来完成任务:

2.1 如果 M2 发出的是写部分 cache line,且 cache 中没有对应地址的 cache line,它会在自己的(CleanUnique)事务完成时接收 cache line 数据,然后正常地进行自己的写操作。

2.2 如果 M2 发出的是写完整 cache line,M1 在写的过程中,会将 M2 中的对应地址的 cache line 进行 invalid。M2可以在自己的(MakeUnique)事务完成时继续处理自己的完整 cache line 写。

2.3 如果 M2 发出的是写部分 cache line,且 cache 中有对应地址的 cache line,因此正常情况下不用(向主存或者其他 cache)请求 cache line 的副本。但是要注意 M1 在写的过程中,会将 M2 中的对应地址的 cache line 进行 invalid,因此 M2 的 CleanUnique tr 操作完成后,需要使用以下两种方法之一:(因为是 CPU1 和 CPU2 同时发出 tr, 然后才是 CCI 判断 M1 先进行写操作,因此在当前 M2 是 partial store 的情况下,M2 已经发出了 CleanUnique tr,表示不要获取新的 cache line)所以需要进行下边二选一的额外步骤: )

2.3.1 为了让 M2 中有最新的 cache line,M2 需要重新进行发出 ReadUnique tr 的操作。

2.3.2 M2 直接 partial store 到主存,此时M2 还是没有对应的 cache line,为了之后的时间可能还会用到这部分内存,M2 还得再次获取这个 cache line。

1.4 transaction 类型概述

1.4.1 Non-snooping transaction

non-snooping 事务用于访问不在其他 mst 缓存中的内存位置(no-shareable 域内存),这些事务不会执行 snoop 事务,用于以下类型的内存:

- Non-shareable

- Device

两种 non-snooping 事务的类型分别为:ReadNoSnoop 和WriteNoSnoop

1.4.2 coherence transaction

通常,一致性事务用于访问 Shareable 地址内存,他们可以被保存到多个 mst 的缓存中。

从可共享位置执行读操作的事务

当 mst 需要的对 Shareable 属性的内存空间执行读命令时,允许其他 mst 的 cache line 副本仍然保留。对应的 snoop 事务如下:

ReadClean:表示 mst 组件只能接受 Clean 状态的 cache line,通常由无法接受 dirty 或者具有 Write-Through 缓存的 mst 使用。不能承担将 dirty 状态的 cache line 写入主存的责任。

ReadNotSharedDirty: 表示mst 可以接收除了 SharedDirty(SD) 之外的任何状态的 cache line,这意味着 cache line 可以是 UC、UD、SC。

ReadShared:都支持。

对于上述三种事务,有以下三条补充:

备注1:对于上面所述的每一种 snoop tr 来说,被 snoop 的 mst 的 cache line 是 dirty 的状态都是可以接受的,即使发起端的 mst 不支持,CCI 会负责将 dirty 的 cache line写入到主存。 例如:mst1 使用 RC_tr 去其他被 snoop 的mst 去读取数据,mst2 中有对应的 cache line,但是状态是 Dirty,CCI 对负责将 Dirty 的 cache line 写入到主存,然后mst2 上的这个 cache line 就会变成 Clean,然后返回 resp 和 data 信息到 CCI。

备注2:如果被 snoop 的mst 中有对应的 cache line,那么一定会通过 RD 通道返回 cache line 的数据。

备注3:如果被 snoop 的mst 中有对应的 cache line,需要在读取之后将它的 Unique 属性转换为 Shared 属性。

从可共享位置执行写操作的事务

在进行写操作之前,需要本地对应 cache line 是 Unique属性的,不然会出现一致性错误。因此可以使用以下事务:

ReadUnque:

使用场景:mst在部分 cahce line 存储时使用,且在 mst 没有对应 cache line的情况下。

功能:清除其他 mst 中的对应 cache line,并获取数据的一个 cache line(部分字节)。

CleanUnique:

使用场景:用于mst在部分 cache line 存储时使用,且在 mst 有对应 cache line的情况下。

功能:清除其他 mst 中的对应 cache line,不返回数据。如果被清除的是 dirty 状态的,CU 事务负责将它写入主存。

MakeUnique:

使用场景:用于mst在全部 cache line 存储时使用

功能:清除其他 mst 中的对应 cache line,不返回数据。

不需要缓存 cache line 副本,使用的事务

当 mst 想要访问一个 shareable 属性的内存,且不会在本地 cache 中保留 cache line 副本,或者这个 mst 没有缓存组件,使用以下事务:

ReadOnce:

使用场景:不保留本地 cache line 的读操作。

功能:读取到其他 mst 的缓存后,被读取的 cache line 如果是 Unique 状态,不会转变成 Share 状态。

WriteUnique:

使用场景:用于完整 cache line 存储或者部分 cache line 存储使用。

功能:发出写事务之前删除 cache line 的所有其他副本,并确保执行写事务之前将所有 dirty 状态的 cache line 写入主存。

WriteLineUnique:

使用场景:只能用于完整 cache line 存储。

功能:发出写事务之前删除 cache line 的所有其他副本。

备注:与Shareable内存的其他事务不同,ReadOnce和WriteUnique事务不需要是完整的 cache line 大小。然而,WriteLineUnique事务需要是一个完整的 cache line 大小。

1.4.3 内存更新事务

WriteBack:用于将 dirty 状态的 cache line 写入到主存中,且不保留 cache line 的副本。

WriteClean:用于将 dirty 状态的 cache line 写入到主存中,且保留 cache line 的副本。

WriteEvict:用于将 cache line 写入到下一级的缓存中,不需要更新主存。

Evict:mst 使用 Evict 事务来指示在不需要主存更新时,从驱逐对应的本地 cache line。事务允许跟踪特定组件中的 cache line,并可用于构建窥探过滤器等应用程序。数据传输与驱逐事务不相关。

备注:WriteBack、WriteClean、WriteEvict 和 Evict 事务不会导致对其他缓存的窥探事务。其他缓存不需要知道 cache line 是否已写入主存。WriteBack、WriteClean、WriteEvict和Evict事务不像其他窥探事务那样序列化。

1.4.4 缓存维护事务

Mst 使用缓存维护事务来访问和维护系统中其他 mst的缓存。特别是,缓存维护事务使 mst 能够查看读、写操作对无法通过其他方式访问的系统缓存的影响。这个过程通常称为软件缓存维护。广播缓存维护操作也可以传播到下游缓存,允许维护系统中的所有缓存。

发起维护事务的 Mst 还负责自己本地缓存上执行的适当操作。以下事务使用缓存维护:

CleanShared: 被监控的 mst 如果有对应地址的 dirty cache line,那么将它写进主存。并不清除这些 cache line。

CleanInvalid: 被监控的 mst 如果有对应地址的 dirty cache line,那么将它写进主存。并清除这些 cache line。

MakeInvalid: 直接清除 snooped 的 cache 中对应的 cache line,即使他们是 dirty 的,也不执行写入主存操作。

1.4.5 Snoop 事务

Snoop事务是使用Snoop地址、Snoop响应和Snoop数据通道的事务。Snoop事务是一致事务和缓存维护事务的子集。

1.4.6 barrier 事务

barrier 事务为系统中事务的顺序和观察提供了保证,ACE5和ACE-Lite不支持 barrier 功能。

ACE 支持以下类型的 barrier:

- Memory barrier

- Synchronization barrier

Mst 发出一个 Memory barrier 事务来保证:如果另一个 mst 在适当的域中可以在 barrier 之后观察到任何事务,那么他必须能有在屏障之前观察到每个事务。

Mst 发出 Synchronization barrier,以确定在 barrier 之前发出的说有实物何时被特定域中的每个 mst 观察到。一些 Synchronization barrier 还要求 barrier 事务发出前发出的所有事务必须到达目标从属组件。

1.4.6 分布式虚拟内存(DVM)事务

分布式虚拟内存(DVM)事务用于虚拟内存系统维护,通常在分布式虚拟内存系统内的组件之间传递消息。

1.5 事务处理过程

当 Mst 发出事务时,一致性信号表明事务指向一个由多个组件共享的内存位置,因此需要一致性支持,一般来说交易的处理方法如下:

- Mst 开始发出 tr

- 根据是否需要一致性需求,tr 需要:

- (不支持)根据使用的地址解码方案,传递给下层组件,

- (支持)通过 CCI 传递给一致性支持逻辑。

- 将一致性事务和来自其他 Mst 的后续事务进行对照,以确保正确的处理顺序;

- CCI 决定需要哪一种 Snoop 事务;

- 每个接收到 Snoop 事务的 mst 都必须提供一个 Snoop 的 resp,一些 mst 还可能会提供 data 数据用以完成 snoop 事务(例如 ReadShared tr);

- CCI 根据返回的 resp 决定是否需要访问主存;

- CCI 整理 snoop 到的 resp 和 data 信息;

- 发起端的 mst 完成事务。

1.6 ACE 中的一些概念

1.6.1 域

ACE 使用了“shareability domains(可共享域)”的概念,可共享域的内容就是 mst 组件,它使发起端 mst 在发出一致性或者 barrier 事务时,能够确定要包含那些其他的 mst 组件。

对于一致性事务,CCI 通过共享域来判断需要 snoop 的 mst 有哪些。

对于 barrier 事务,域可用于确定哪些mst 参与建立 barrier 的排序关系,barrier 的域可用于确定 barrier 事务可以传播多远,以及建立所需顺序所需的 barrier 属性。

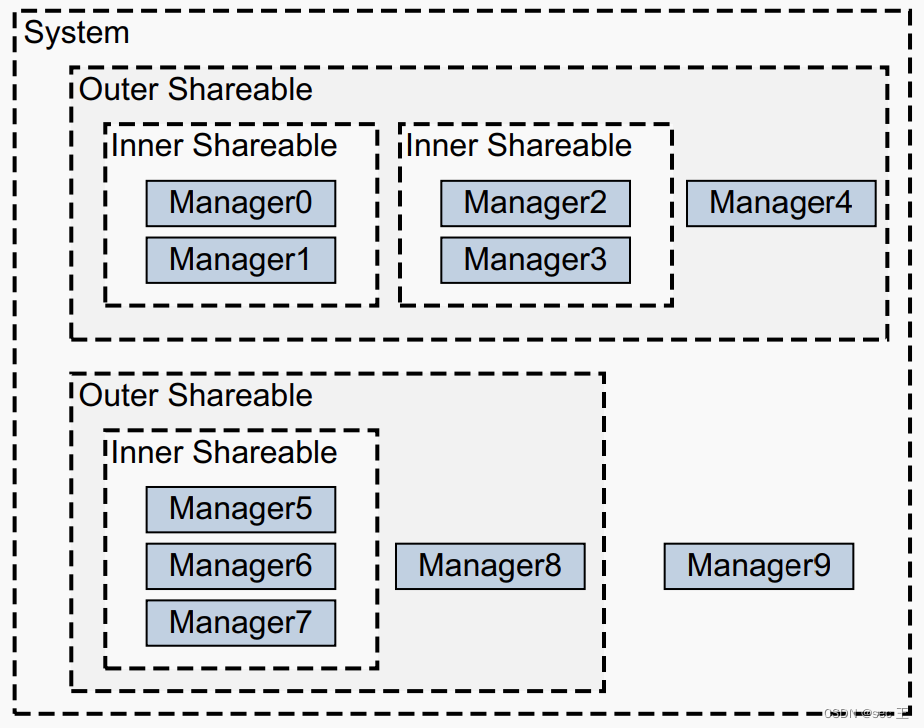

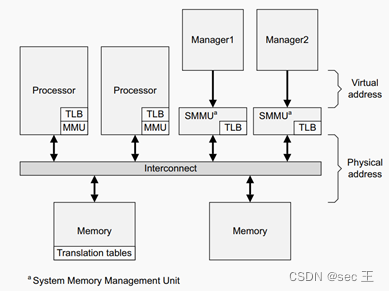

它用于多层次、多 mst 的复杂 SOC 结构如下图:

如图所述,ACE 协议定义了以下四种域:

Non-shareable: 只包含单个 mst

Inner shareable: 包含多个 mst

Outer shareable: 至少包含 inner shareable的 mst,也能包括其他 mst

system shareable: 改域包含 system 中的所有 mst

尽管一个系统中可以存在多个 Non-Shareable、Inner Shareable 和 Outer Shareable 的域,但是每个域中包含的 mst 必须有一个一致性的定义。比如 M0 的 inner Shareable 中有 M1,同样的 M1 的 inner Shareable 域也必须要有 M0。

同一类的域被定义为不可重叠的,且一个 mst 如果同时在一个 Inner 共享域和一个 Outer 共享域中,那么这个 Inner 共享域中所有的 mst 都必须包含在这个 Outer 共享域中。

system 共享域中也包含了 Non-shareable 的域。

1.6.2 Barriers

barrier 事务为系统中事务的顺序和观察提供了保证,它有两种类型( barrier 之后发出的 tr 一定是建立在 barrier 之前发出 tr 已经完成的基础上的):

Memory barriers:如果适当域中的另一个 mst 可以在 barrier 之后观察到任何事务,那么它必须能够在 barrier 之前观察到每个事务。

Synchronization barriers:Manager 组件发出同步屏障,以保证当 barrier 事务完成时,在屏障之前发出的所有事务都可以被适当域中的每个 mst 观察到。此外,还有一个额外的要求,在 barrier 事务之前发出的所有事务必须在屏障完成之前到达它们要到达的端点下级。

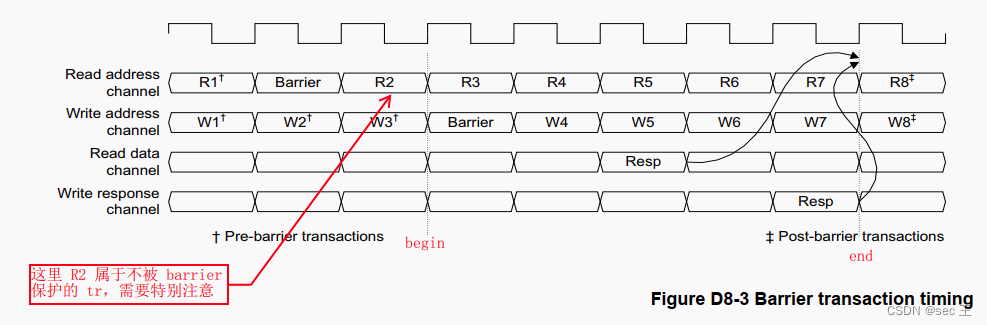

barrier 样例的时序进程如下图 :

barrier 事务有一个地址(开始)阶段和一个响应阶段,但不发生数据传输。Mst 组件必须在读地址通道和写地址通道上发出屏障事务。barrier可以强制排序,因为只有barrier 之前发出的事务全部完成之后,barrier 的读写事务才会有 resp 返回,因此可以保证:barrier 之后的事务一定是建立在 barrier 发出前的事务全部完成基础上的。

1.6.3 Distributed Virtual Memory

ACE 支持分布式虚拟内存(DVM),并包含允许虚拟内存系统管理的事务。虚拟内存系统的基本组成如图:

133

133

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?