一、要求

1、这是提供的数据选择器的代码,可以在工程中例化

module data_sel( input S0 , input S1 , input D0 , input D1 , input D2 , input D3 , output wire Y ); assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3); endmodule

2、函数模块的输入输出定义如下:

input A,B,C; output wire L;

二、分析

1、assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

这行代码是选择器的功能,控制端S1 决定了选择器是否工作,

当控制端S1为1时,只用看后半部分

~S1为0,0“与”任何数都为0,所以 ~S1 & (~S0&D0 | S0&D1) 这部分的值为0,即输出Y和D0D1S0无关;

S1为1,S1&(~S0&D2 | S0&D3),变成,(~S0&D2 | S0&D3)。S0为0时,Y是D2;S0为1时,Y是D3;

所以 S1S0 为 10 时 ,Y = D2 S1S0 为 11 时,Y = D3

当控制端S1为0时,只用看前半部分

S1为0,0“与”任何数都为0,所以 S1 & (~S0&D2 | S0&D3) 这部分的值为0,即输出Y和D2D3S0无关;

~S1为1,~S1&(~S0&D0 | S0&D1),变成,(~S0&D0 | S0&D1)。S0为0时,Y是D0;S0为1时,Y是D1;

所以 S1S0 为 00 时 ,Y = D0 S1S0 为 01 时,Y = D1

总结:控制端 S1S0 = 00 01 10 11 时,输出 Y 分别选择 D0 D1 D2 D3

三、写代码

1、怎么把选择器和表达式对应?

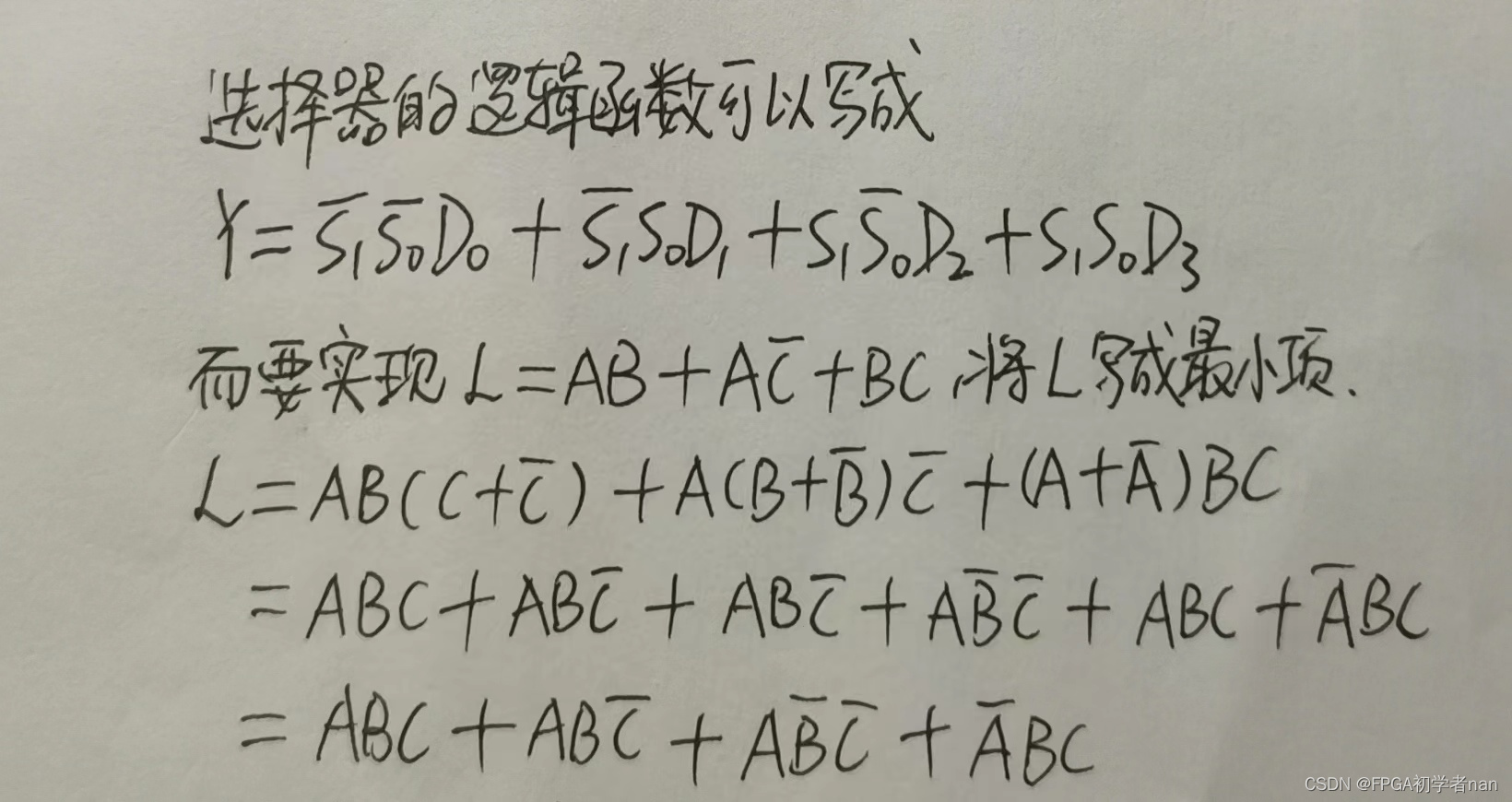

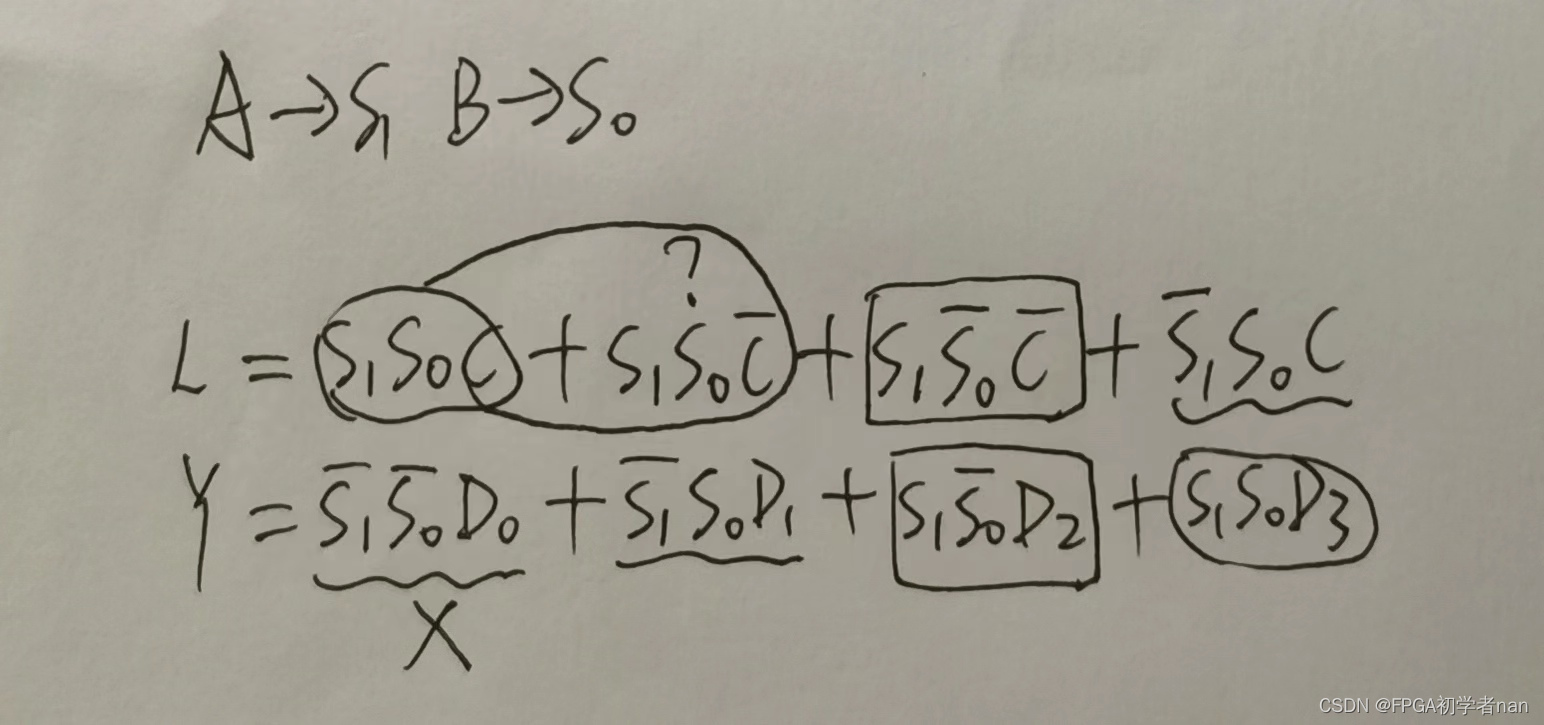

首先令 A = S1 B = S0 ,则可以把表达式 L写成这样。

注意,表达式 L 是要实现的功能,所以它的每一项都必须得到对应。而选择器是用来实现功能的,不必每个项都对应。

根据S1S0锁定,

L的第一项对应Y的第四项 L的第二项也可以对应Y的,把L的第一第二项合并,则可以对应Y的第四项。所以 D3 = 1 。

L的第三项对应Y的第三项。D2 = !C

L的第四项对应Y的第二项。D1 = C

L的四项全部对应完毕,但是Y只使用了三项功能,Y的第一项没有使用,使用让D0 = 0 ,既可以禁止Y 的第一项功能。

2、代码

`timescale 1ns/1ns

module data_sel(

input S0 ,

input S1 ,

input D0 ,

input D1 ,

input D2 ,

input D3 ,

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

module sel_exp(

input A ,

input B ,

input C ,

output wire L

);

data_sel data_sel_inst0(

.S0(B) ,

.S1(A) ,

.D0(0) ,

.D1(C) ,

.D2(!C) ,

.D3(1) ,

.Y(L)

);

endmodule

(只创建一个source文件,把上面的代码直接复制到vivado,也会生成这个电路图。但是为了养成好习惯,最后一个source文件只有一个module)

6199

6199

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?