作者: Saint

掘金:https://juejin.im/user/5aa1f89b6fb9a028bb18966a

微博:https://weibo.com/5458277467/profile?topnav=1&wvr=6&is_all=1

GitHub:github.com/saint-000

CSDN: https://me.csdn.net/qq_40531974

VHDL基础体会篇(三)

Part3

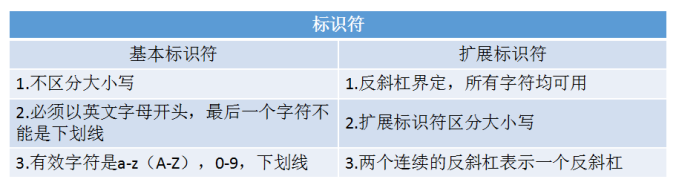

1.标识符

2.数据对象:

(1)信号(Signal)

(2)变量(Variable)

(3)常量(Constant)

3.数据类型:标准数据类型,用户自定义数据类型,用户自定义子类型。

标准数据类型:位BIT(逻辑0或1)

位矢量BIT_vector(一串逻辑0或1的数列)

整数Integer(32位整数)

布尔量Boolean(逻辑真或假)

字符Character(单引号)

字符串String(双引号)

用户自定义数据类型:(只列出枚举法)

用户自定义子类型:SUBTYPE 子类型名 is 原数据类型名[范围];

若之前已经定义了CNT为整数型,此时我们设计的只要从0-9循环计数,而我们用的Integer范围太大了,我们可以在原类型的基础上定义子类型:

SUBTYPE CNT is integer range 0 to 9;

4.数据类型转换

我们大部分需要留意的是BIT与std_logic之间的关系以及相应的数据间运算

Signal CNT:std_logic_vector(0 to 2);

.......

CNT<=CNT+1;(这里的加法需要用到IEEE中的std_logic_Unsigned.all)

5.操作符

899

899

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?