基础

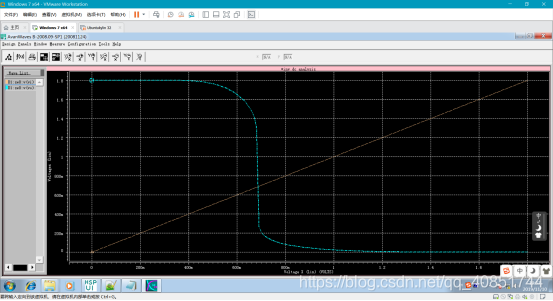

反相器直流特性:

SPICE网表:

*INV DC Analysis

.TEMP 25.0000

.option abstol=1e-6 reltol=1e-6 post ingold

.lib 'gd018.l' TT

* --- Voltage Sources ---

vdd VDD 0 dc=1.8

vin vi 0 dc=0.9

* --- Inverter Subcircuit ---

Mpmos vo vi VDD VDD PCH W=30U L=6U

Mnmos vo vi GND GND NCH W=30U L=6U

* --- Transient Analysis ---

.dc vin 0 1.8 0.01

.print dc v(vi) v(vo)

.end

没什么特别的,nmos和pmos串联,如有不理解可以看我之前的博客

同样可以做出如下的改进:

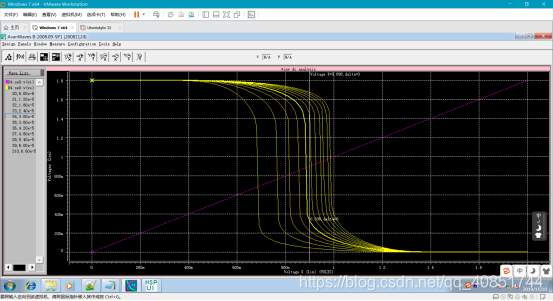

反相器直流特性-不同宽长比:

SPICE网表:

*INV DC Analysis

.TEMP 25.0000

.option abstol=1e-6 reltol=1e-6 post ingold

.lib 'gd018.l' TT

.para WA=30U

* --- Voltage Sources ---

vdd VDD 0 dc=1.8

vin vi 0 dc=0.9

* --- Inverter Subcircuit ---

Mpmos vo vi VDD VDD PCH W=WA L=6U

Mnmos vo vi GND GND NCH W=6U L=6U

* --- Transient Analysis ---

.dc vin 0 1.8 0.01 sweep WA 30U 36U 1U

.print dc v(vi) v(vo)

.end

这里通过定义了一个WA变量,我们可以通过sweep进行改变,看不同宽长比情况下的图像

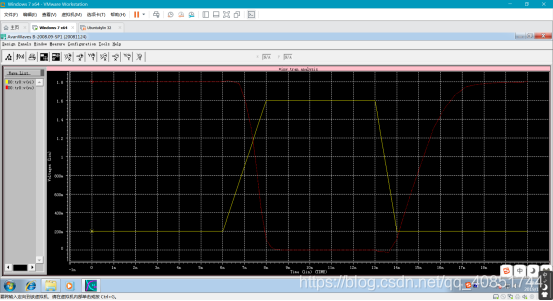

反相器瞬态特性-单周期

SPICE网表:

*AC Analysis for INV

.TEMP 25.0000

.PRINT TRAN V(IN) V(OUT)

*打印节点in,out电压瞬态分析值

.option abstol=1e-6 reltol=1e-6 post ingold

.lib 'gd018.l' TT

* --- Voltage Sources ---

vdd VDD 0 dc=1.8

vin vi 0 PULSE(0 1.8 0ns 0.5ns 0.5ns 5ns 10ns)

*在vi和0节点之间加一个脉冲源,低电平为0,高电平为108V,延时0ns,上升沿0.5ns,下降沿0.5ns脉冲宽度5ns,周期10ns

* --- Inverter Subcircuit ---

Mpmos vo vi VDD VDD PCH W=30U L=6U

Mnmos vo vi GND GND NCH W=30U L=6U

* --- Transient Analysis ---

.OPTIONS POST

.tran 0.001ns 10ns

*瞬态分析步长为0.001ns,时间为10ns

.end

我们要看输入输出电压

可以进行如下改进

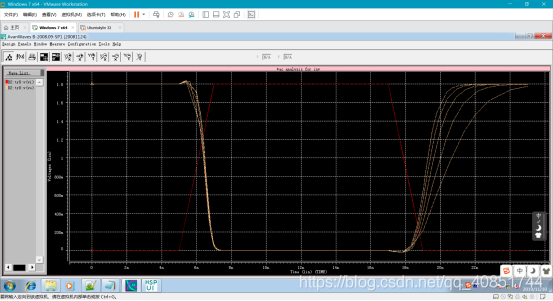

反相器瞬态特性-单周期-不同宽长比

SPICE网表:

*AC Analysis for INV

.TEMP 25.0000

*打印节点in,out电压瞬态分析值

.lib 'gd018.l' TT

.para WA=10U

* --- Voltage Sources ---

vdd VDD 0 dc=1.8

vin vi 0 PULSE(0 1.8 5ns 2ns 2ns 10ns 20ns)

*在vi和0节点之间加一个脉冲源,低电平为0,高电平为108V,延时2ns,上升沿0.5ns,下降沿0.5ns脉冲宽度5ns,周期10ns

C1 vo 0 0.75p

* --- Inverter Subcircuit ---

Mpmos vo vi VDD VDD PCH W=WA L=1U

Mnmos vo vi GND GND NCH W=20U L=1U

* --- Transient Analysis ---

.OPTIONS POST

.tran 0.01ns 25ns sweep WA 10U 40U 5U

*瞬态分析步长为0.01ns,时间为25ns

.print tran v(vi) v(vo)

.end

原理讲解——反相器:

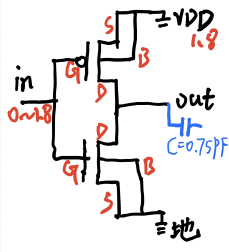

反相器是一个nmos与一个pmos相连,其中栅极相连,为输入端;漏极相连,为输出端。而pmos的源极和衬底接高电平,nmos的源极和衬底接低电平。

当输入为高电平的时候,对pmos而言,Vgs=0;对nmos而言,Vgs=VDD高电平,所以相当于pmos截止,nmos导通,相当于放电,对外显示低电平0;当输入为低电平的时候,对pmos而言,Vgs=-VDD高电平反向;对nmos而言,Vgs=0低电平,所以相当于nmos截止,pmos导通,相当于充电,对外显示高电平1。

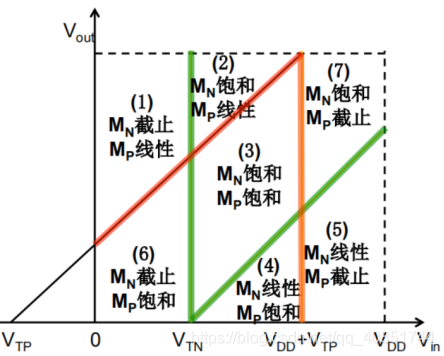

当改变输入电压的时候,根据不同的线性区和饱和区的电压,可以绘制出7个不同的区域,如下:

当 0≤Vin≤VTN,NMOS截止, PMOS线性,Vin在一定范围变化(0~VTN), Vout始终保持VDD。

当VTN<Vin<Vout+VTP,NMOS饱和,PMOS线性,Vout随Vin的增加而非线性地下降, Kr=KN/KP为比例因子

当 Vout+VTP≤Vin≤Vout+VTN,NMOS饱和, PMOS饱和,VTC垂直下降。

当Vout+VTN<Vin<VDD+VTP,NMOS线性,PMOS饱和,Vout随Vin的增加而非线性地下降

当VDD≥Vin≥VDD+VTP,NMOS线性, PMOS截止,Vin在一定范围变化(VDD+VTP ~ VDD), Vout始终保持0

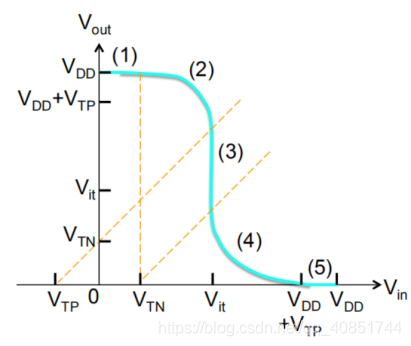

理想VTC曲线:

(1)为输出高电平区

(2)、(3)、(4)为转变区

(5)为输出低电平区

其中(3)表现为垂线段

66

66

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?