原文链接:https://blog.csdn.net/icxiaoge/article/details/80555683

1、 什么是FIFO?

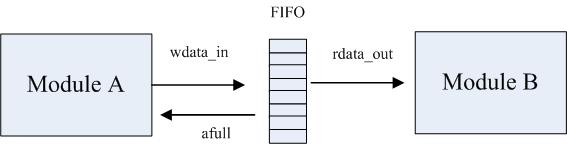

FIFO(first in firstout)是一种用寄存器reg或者RAM实现的存储结构,常用于存储数据通道中的数据流,采用先入先出的数据,当下游模块无法及时处理上流模块输出的数据时,此时需要用FIFO暂存数据,防止数据丢失。

2、 什么是FIFO阈值

FIFO阈值包含将满阈值afull_cnt和将空阈值aempty_cnt,当FIFO内包含的数据data_cnt大于等于afull_cnt时,将满信号有效(afull为1),afull传输给上游模块A,通知上游模块停止发送数据,防止FIFO发送溢出,NOTE:将满阈值afull_cnt的作用是防止FIFO发送溢出导致数据丢失。将空阈值的作用时防止FIFO空的,即FIFO中没有有效数据了还会产生读数据操作。

3、 FIFO将满阈值如何设置

请看下图,数据data和有效信号vld从模块A产生,经过N拍延时,输入到FIFO,FIFO产生将满信号afull,经过M拍延时反馈到模块A,假设模块A接收到afull=1时,立即停止发送数据。假设FIFO深度为depth_fifo,每拍为一个时钟周期。

1为了保证FIFO不发生溢出,请问将满阈值afull_cnt至少应该设置成多少?

2为了充分发挥FIFO的性能,FIFO深度depth应该为多少?

1343

1343

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?