1. 操作技巧

1.1. 配置.cdsinit文件

.cdsinit文件负责Cadence软件的初始化配置,包括加载快捷方式等。

将cdsinit文件从下面的cadence的安装目录复制到软件启动目录,并命名为“.cdsinit”。

cadence/IC617/tools/dfll/samples/local

命名为“.cdsinit”后打开,找到LOAD USER CUSTOMIZATION 之后的内容,按照文件的说明每一行前面加“;”注释掉这部分内容,或者直接删掉,不然启动不正常。

接下来就可以在.cdsinit中添加代码使cadence更通人性:

1️⃣直接打开open Library manager

ddsOpenLibManager()

2️⃣更改仿真波形背景颜色为白色,第一句不能用就换第二句。

envSetVal("viva.rectGraph" "background" 'string "white")

envSetVal("viva.graphFrame" "background" 'string "white")

3️⃣更改仿真线条粗细

envSetVal("viva.trace" "lineStyle" 'string "solid")

envSetVal("viva.trace" "lineThickness" 'string "medium")

envSetVal("asimenv.plotting" "useDisplayDrf" 'boolean nil )

.cdsinit和.cdsenv文件说明

Virtuoso中通过cdsini文件修改初始设置

1.2. Net Highlighting

2. 版图

2.1. 版图环境设置

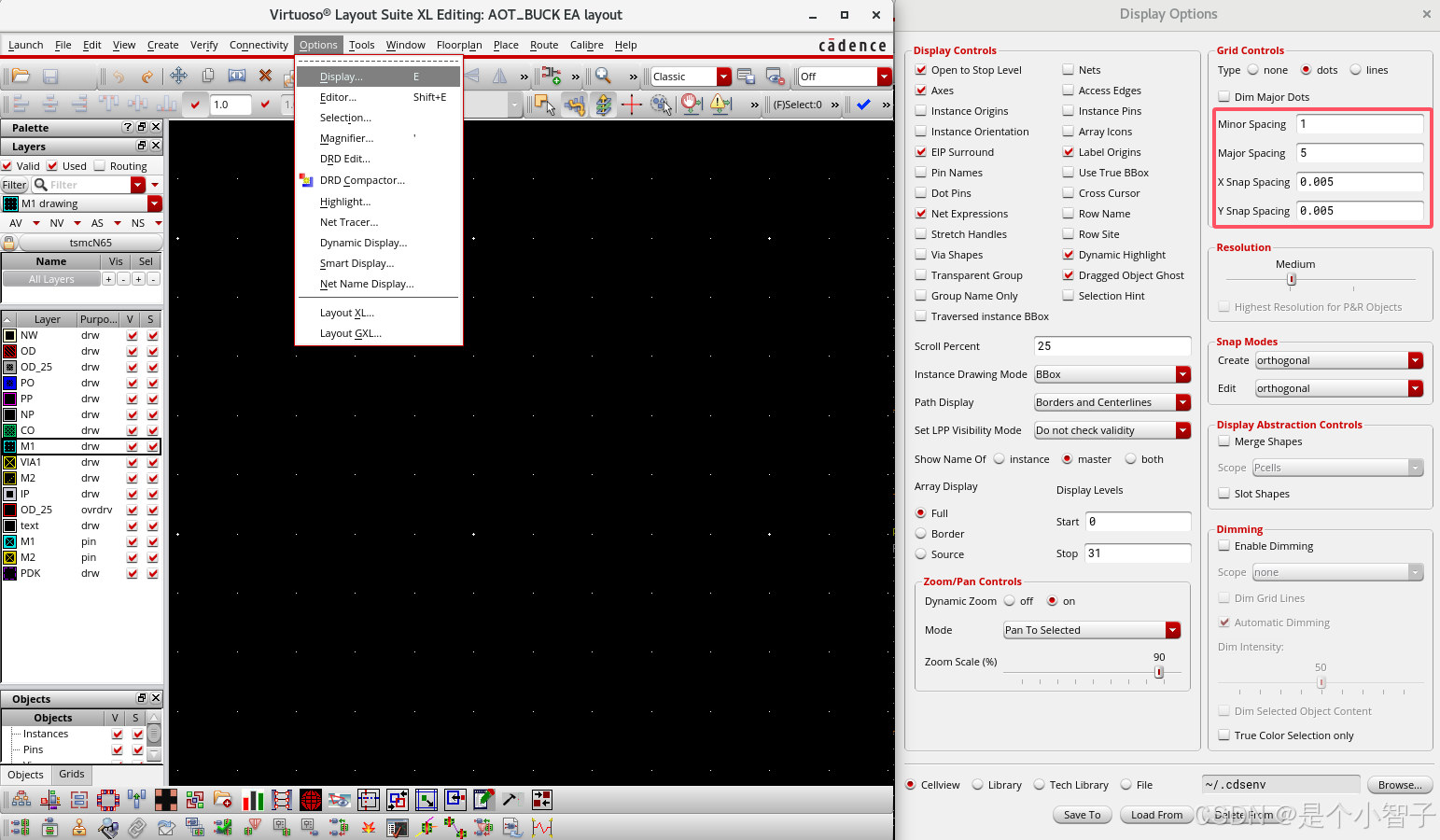

Snap Spacing是鼠标移动精度,翻阅Design Rules File,搜索“grid”,可看到工艺推荐的分辨率:

Snap Spacing是鼠标移动精度,翻阅Design Rules File,搜索“grid”,可看到工艺推荐的分辨率:

2.2. IC617中集成calibre

在本文1.1.中为了操作方便,将配置文件.cdsinit复制到了软件的启动目录。这导致打开layout界面时候,最上面选项栏没有calibre,这意味着无法使用calibre进行后续的DRC、LVS等操作。

最简单的解决办法就是将软件启动目录下的.cdsinit文件删掉。

第二种方法是在calibre安装目录下搜索“skillREADME”这个文件,如下图。

打开“skillREADME”这个文件,将一下部分复制到.cdsinit最后面。只要红框中的部分,因为说明部分未用注释符号,直接复制到.cdsinit会引起语法错误。

打开.cdsinit可以看到红色框住的是复制来的内容,红色框上面是本文1.1.节中添加的内容。

操作完成后启动软件,打开layout界面,可以看到calibre出现在工作栏。

2.3.DRC或者LVS中如何关掉FULL_CHIP校验

DRC校验一个电路版图的时候总是报许多跟chip相关的错误,如下图所示。而我只是想校验当前这个电路子模块。

解决方法:按照下图找到DRC Rules文件中FULL_CHIP这一行,并注释掉。进行chip校验时再将其打开。

3. 仿真

3.1.蒙特卡洛仿真(失配)

①先增加蒙卡工艺角(一般带有mc) 第一种方法:打开ADE XL→Setup→Model Library Setup

①先增加蒙卡工艺角(一般带有mc) 第一种方法:打开ADE XL→Setup→Model Library Setup

第二种方法:点击Corners Setup(温度计样子)

②运行蒙卡仿真 选择Monte Carto Sampling→Simulation Options→设置仿真点数,勾选Save Data to Allow Family Plots→Run

Save Data to Allow Family Plots选项可以将每一个点的仿真数据保存方便查看。

③仿真结果 Min、Max、Mean分别是200个仿真点中的最小、最大、平均值。Std Dev是标准差

标号1用来查看每个晶体管失配的占比,标号2可以查看所有点失配的统计图形。

4.calculator

4.1.deriv 求导

4.2.积分

定积分:integ

不定积分:iinteg

5562

5562

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?