1. 电路结构

1.1.cascode结构

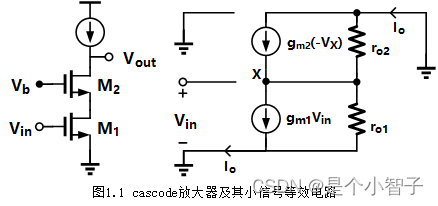

图1.1是一个以理想电流源作为负载的cascode放大器。画出其等效电路,可以列出下面方程组:

图1.1是一个以理想电流源作为负载的cascode放大器。画出其等效电路,可以列出下面方程组:

{ I o u t = g m 1 V i n + V X r o 1 I o u t = − g m 2 V X − V X r o 2 \left\{ \begin{aligned} I_{out}&=g_{m1}V_{in}+\frac{V_X}{r_{o1}} \\[2.5ex] I_{out}&=-g_{m2}V_X-\frac{V_X}{r_{o2}} \\[2.5ex] \end{aligned} \right. ⎩ ⎨ ⎧IoutIout=gm1Vin+ro1VX=−gm2VX−ro2VX

解方程组得到跨导Gm:

G

m

=

I

o

u

t

V

i

n

=

g

m

1

g

m

2

r

o

1

r

o

2

+

r

o

1

g

m

2

r

o

1

r

o

2

+

r

o

1

+

r

o

2

≈

g

m

1

\begin{aligned} G_m=\frac{I_{out}}{V_{in}}=g_{m1} \frac{g_{m2}r_{o1}r_{o2}+r_{o1}}{g_{m2}r_{o1}r_{o2}+r_{o1}+r_{o2}}≈g_{m1} \end{aligned}

Gm=VinIout=gm1gm2ro1ro2+ro1+ro2gm2ro1ro2+ro1≈gm1

将输入信号短路,输出端接电压源Vo,求出其输出电阻为:

R

o

u

t

=

V

o

I

o

=

g

m

2

r

o

2

r

o

1

+

r

o

1

+

r

o

2

≈

g

m

2

r

o

2

r

o

1

\begin{aligned} R_{out}=\frac{V_{o}}{I_{o}}=g_{m2}r_{o2}r_{o1}+r_{o1}+r_{o2} ≈g_{m2}r_{o2}r_{o1} \end{aligned}

Rout=IoVo=gm2ro2ro1+ro1+ro2≈gm2ro2ro1

最后可以得到cascode放大器的电压增益:

∣

A

v

∣

=

G

m

R

o

u

t

≈

g

m

1

g

m

2

r

o

2

r

o

1

\begin{aligned} |A_v|=G_mR_{out} ≈g_{m1}g_{m2}r_{o2}r_{o1} \end{aligned}

∣Av∣=GmRout≈gm1gm2ro2ro1

由此可见,cascode结构的电压增益能达到两级放大器的效果。cascode结构的输出电阻也有了很大的提升。根据cascode结构输出电阻大的特性,可以将其用作恒流源。将图1.1中的理想恒流源负载换成cascode恒流源如图1.3所示。于是就可以估算出图1.3 cascode结构电路的电压增益:

∣

A

v

∣

≈

g

m

1

[

(

g

m

2

r

o

2

r

o

1

)

∥

(

g

m

3

r

o

3

r

o

4

)

]

\begin{aligned} |A_v| ≈g_{m1}[(g_{m2}r_{o2}r_{o1})∥(g_{m3}r_{o3}r_{o4})] \end{aligned}

∣Av∣≈gm1[(gm2ro2ro1)∥(gm3ro3ro4)]

1.2.折叠cascode结构

在图1.3的结构中,输出端上下各叠了两个晶体管,为了使他们都工作在饱和区输出摆幅就受到了限制。如果使用折叠cascode结构,就可以解决输出摆幅受限的问题。

利用与前面相同的方法可以计算出图1.4中折叠放大器的输出电阻,两种结构的输出电阻相同:

R

o

u

t

=

g

m

2

r

o

2

r

o

1

+

r

o

1

+

r

o

2

≈

g

m

2

r

o

2

r

o

1

\begin{aligned} R_{out}=g_{m2}r_{o2}r_{o1}+r_{o1}+r_{o2} ≈g_{m2}r_{o2}r_{o1} \end{aligned}

Rout=gm2ro2ro1+ro1+ro2≈gm2ro2ro1

非折叠结构中晶体管M1和M2串联流过相同的电流;折叠结构中晶体管M1和M2获得相当的性能,就要满足I2=|ID1|+|ID2|。所以折叠结构的代价就是增加了功耗。

1.3.折叠cascode运放

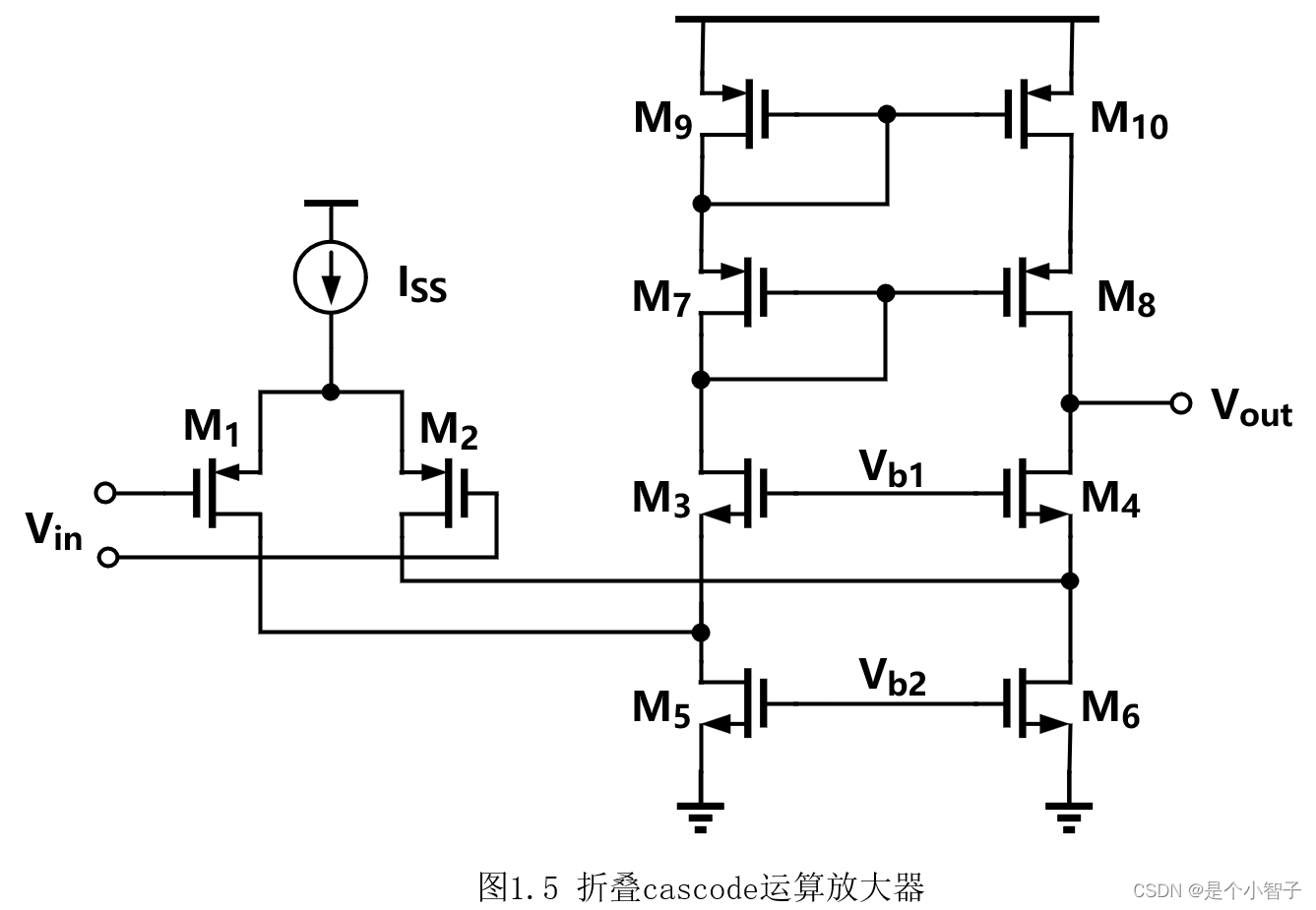

图1.5采用PMOS输入折叠cascode结构的运算放大器。

图1.5采用PMOS输入折叠cascode结构的运算放大器。

尾电流源Iss是流过晶体管M1、M2的电流之和。流过M5的电流是M1支路和M3支路电流之和,因此M5和M6上面会流过较大的电流。也就是说通过控制ISS来控制流过M1、M2的电流;M1、M2的电流确定后,晶体管M5可以控制流过M3的电流大小。

计算得到输出电阻:

R

o

u

t

≈

(

g

m

8

r

o

8

r

o

10

)

∥

[

g

m

4

r

o

4

(

r

o

2

∥

r

o

6

)

]

\begin{aligned} R_{out}≈(g_{m8}r_{o8}r_{o10})∥[g_{m4}r_{o4}(r_{o2}∥r_{o6})] \end{aligned}

Rout≈(gm8ro8ro10)∥[gm4ro4(ro2∥ro6)]

计算得到增益:

∣

A

v

∣

≈

g

m

1

(

g

m

8

r

o

8

r

o

10

)

∥

[

g

m

4

r

o

4

(

r

o

2

∥

r

o

6

)

]

\begin{aligned} |A_v| ≈g_{m1}(g_{m8}r_{o8}r_{o10})∥[g_{m4}r_{o4}(r_{o2}∥r_{o6})] \end{aligned}

∣Av∣≈gm1(gm8ro8ro10)∥[gm4ro4(ro2∥ro6)]

单位增益带宽GBW与负载电容有关:

G

B

W

=

g

m

1

C

g

d

4

+

C

g

d

8

+

C

L

\begin{aligned} GBW=\frac{g_{m1}}{C_{gd4}+C_{gd8}+C_L} \end{aligned}

GBW=Cgd4+Cgd8+CLgm1

M3和M4的栅源之间有较大的寄生电容,与次极点频率相关:

p

2

=

g

m

4

C

g

s

4

\begin{aligned} p_2=\frac{g_{m4}}{C_{gs4}} \end{aligned}

p2=Cgs4gm4

1.4.偏置电路

图1.6是对之前设计偏置电路的修改,启动电路结构不变,只需要把电流源换为cascode电流源即可。要注意NMOS晶体管M1、M2的宽长比,在这里K=4。另外两个NMOS管M3、M4的宽长比相同。

2. 整体电路图

电路整体由放大电路、偏置电路和启动电路构成,在图2.1中分别对应绿色、蓝色和红色矩形框。

3. 仿真分析

3.1.dc仿真

首先要调节cascode晶体管宽长和偏置电压,选择合适的工作状态。

如果图2.1cascode结构M6、M8两个NMOS(黄色圈内的晶体管)的偏置电压偏大一些,而流过的电流不变会使其Vds减小,由于沟道长度调制效应ro也会减小,最终使得运放增益减小。

如果电流是事先确定好的,图2.1放大器cascode结构中M7、M9(紫色圈内的晶体管)的宽长和偏置设定好后就难以调整了,因为一旦改变,cascode结构的电流就变了。

调整过后每个晶体管的dc工作状态如图3.1所示。

3.2.ac仿真

晶体管dc工作点调整好之后就可以得到图3.2的结果,直流增益为91dB,如果dc工作点没调好,输出电阻不够大,增益也就比较小。

博客主要介绍了电路结构,包括cascode结构、折叠cascode结构、折叠cascode运放和偏置电路,分析了其跨导、输出电阻、电压增益等参数。还给出整体电路图,由放大、偏置和启动电路构成。最后进行仿真分析,包括dc仿真和ac仿真,探讨了工作状态对增益的影响。

博客主要介绍了电路结构,包括cascode结构、折叠cascode结构、折叠cascode运放和偏置电路,分析了其跨导、输出电阻、电压增益等参数。还给出整体电路图,由放大、偏置和启动电路构成。最后进行仿真分析,包括dc仿真和ac仿真,探讨了工作状态对增益的影响。

2459

2459

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?