折叠式共源共栅

Cascode结构的设计思路是:将输入电压转化为电流,然后将它作为共栅级的输入。

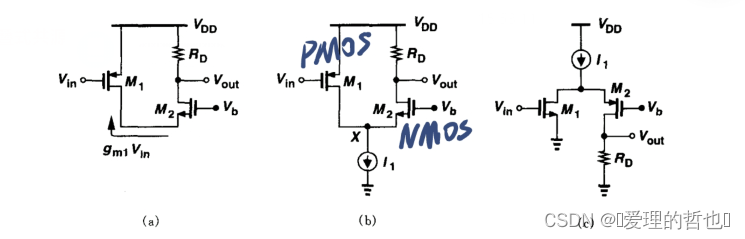

然而,输入器件和共源共栅器件不一定是同一种类型。例如下图(a)中,PMOS和NMOS组合也可以完成相同的功能。

为了对M1和M2进行偏置,需要像(b)那样增加一个电流源。

(b)和(c)都是“折叠式共源共栅”级,这是因为小信号电流分别向上折叠{如(b)}或者向下折叠{如(c)}

(1)小信号工作原理

(b)中,如果变大,

减小,使得

增加,所以

下降。

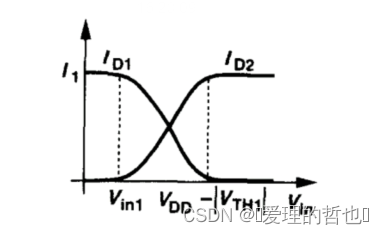

(2)大信号特性{假设从

减小到0}

①如果,此时M1截止。电流

全部流过M2,可得

;

②如果,M1开启并且处于饱和状态,可得:

随着下降,

进一步减小,当

时,

最终变为0。这时:

因此:

如果,下降到

以下,

趋向于大于

,因此M1进入线性区以使

。变化过程见下图:

(3)计算输出阻抗

利用公式,可以容易得出:

可以看出电路表现出的输出阻抗比非折叠的共源共栅的要小。

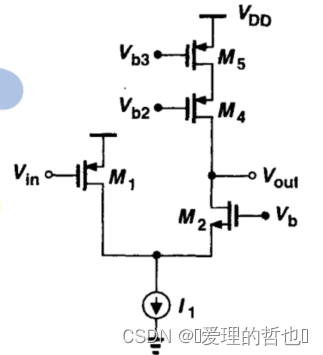

为了实现高电压增益,折叠式共源共栅的负载可以用共源共栅本身来实现,如下图:

回顾:

我们设法增大了电压放大器的输出电阻来得到高增益。或许看起来会使电路的速度容易受负载电容的影响,但如果放大器工作在一个适当的反馈环路里,高输出阻抗本身并不会造成严重的问题。

2840

2840

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?