EDA实验课课程笔记(五)——NC-verilog的介绍与使用(一)

简介:简单介绍NC及其精要的总结,防止以后忘记、本文主要是简单的背景及图像化界面的使用

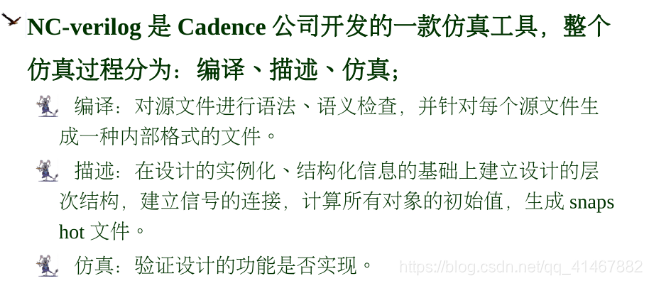

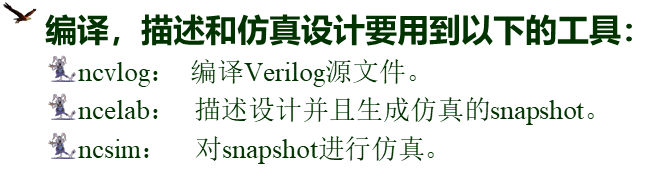

NC简介

类比于modelsim的使用,modelsim简单来说需要三部,首先compile,然后start simulation,之后run就可以看到波形了。NC中分为单步实现及多步实现。单步的三个步骤类比于modelsim的仿真进行学习。

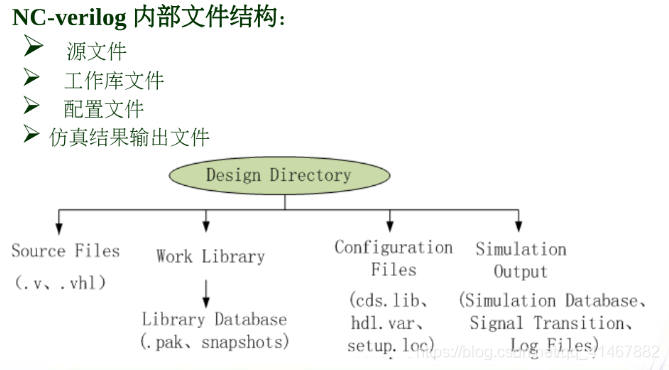

NC内部文件结构

- 源文件

- 工作库文件

- 配置文件:

- 仿真结果输出文件

NC-verilog的两种启动方式

分为图形界面方式,批处理方式。

笔者个人理解,图形化是为了帮助使用者进行理解NC的使用,主要的使用还是使用批处理方式。这里简单介绍下图像化仿真的具体流程。

使用时候的两个问题

1,未使用探针即可观察到波形

2,使用时位设置时间精度

图形界面方式演示视频

NC-verilog

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?