本文参考Verification with VCS Workshop的讲义,简单对理解的进行总结

1,VCS is?

什么是VCS (Verilog Compiled simulator)就是Verilog的编译仿真器,使用类似于我们常用的modelsim。其兼容 IEEE-1364,支持多种抽象级别的仿真。

简单的验证流程如下图所示

- Compiler 生成优化后的仿真可执行文件

- Simulator 执行用户的测试文件,报告仿真结果

- Debugger 提供基于文本的命令行接口Command Line Interface 以及GUI界面的VirSim

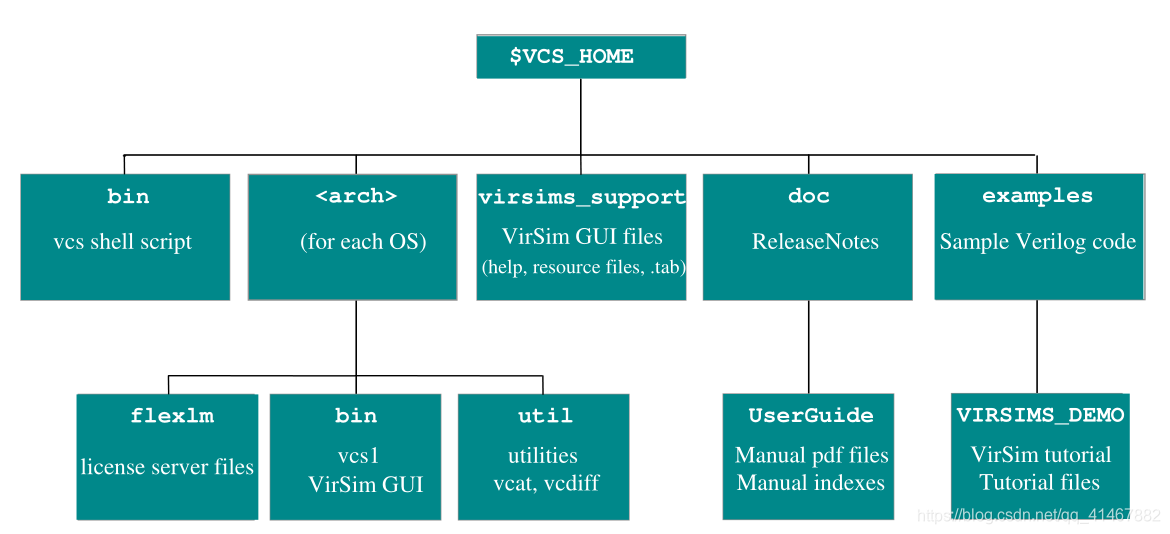

下图是VCS的安装目录

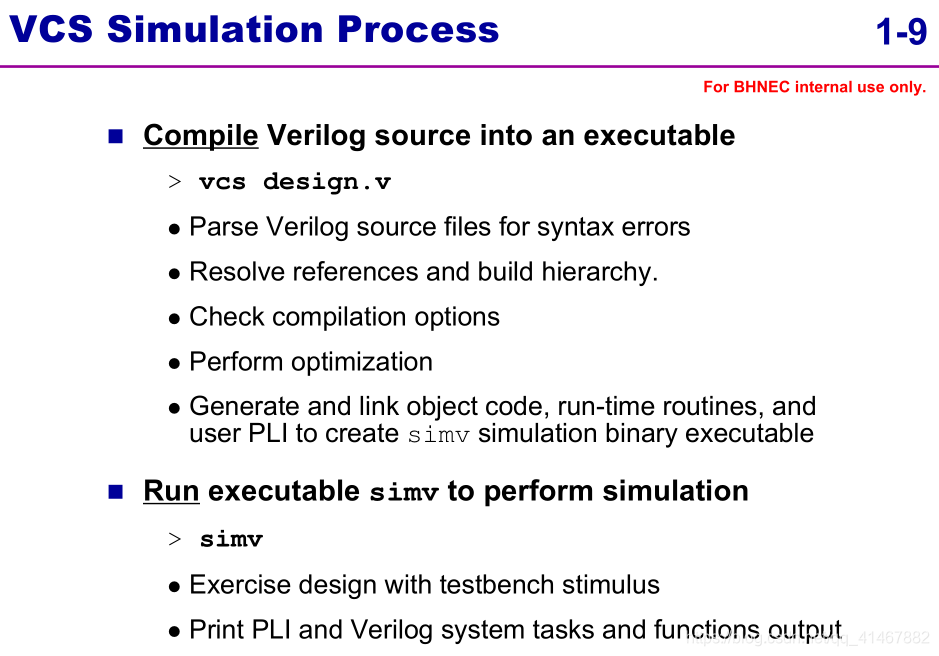

2,VCS的仿真流程

VCS的仿真分为两步

第一步是将Verilog源文件编译成可执行文件

> VCS design.v

解析Verilog源文件以查找语法错误,解析引用并构建层次结构,检查编译选项,生成并链接目标代码、运行时例程和用户PLI,以创建SIMV模拟二进制可执行文件

第二步是运行simv来进行仿真

> simv(官方给出的)

> ./simv(自己使用的)

使用测试台刺激的运动设计

打印PLI和Verilog系统任务和函数输出

3,VCS编译仿真的流程

这里的命令使用会在lab的学习中使用

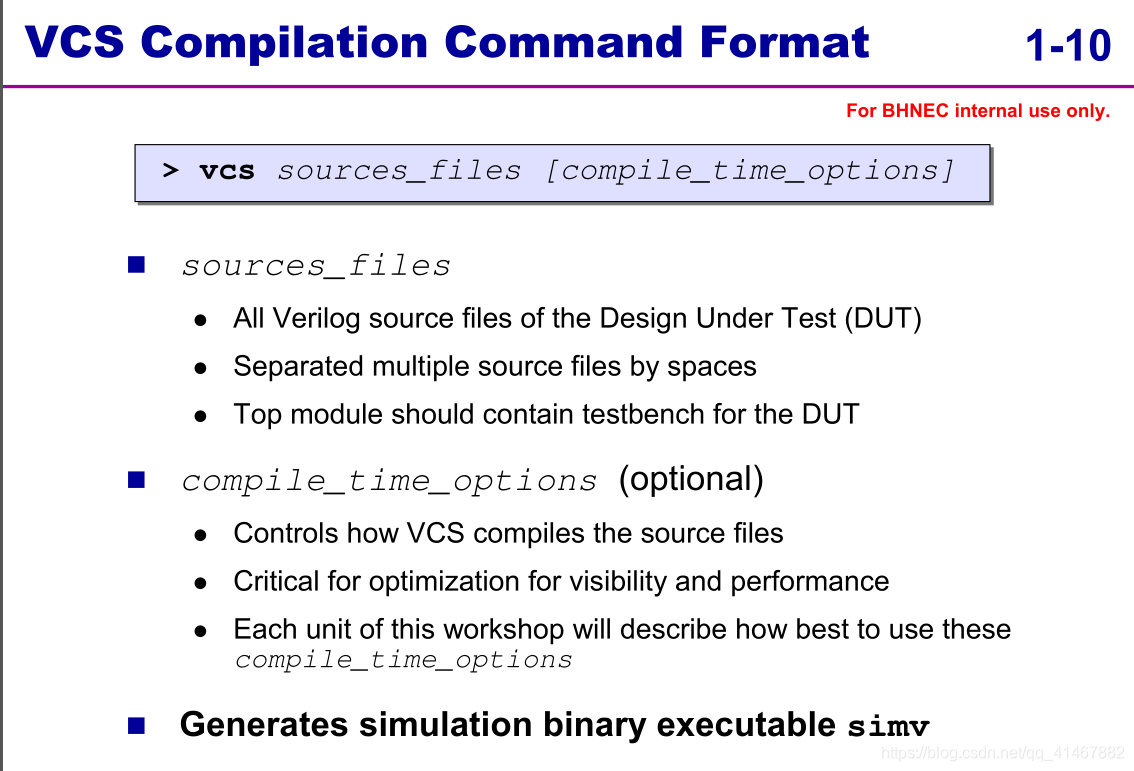

4,VCS编译命令格式

187

187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?