常见的方法:

对于降低功耗的方法:

属于系统级的是:硬软件划分功耗管理;

属于体系结构级的是:电压/频率调整、多电压供电、电源门控、多阈值优化、FFT域、异步设计;

属于寄存器传输级+逻辑/门级的是:独热编码、行波计数器、总线反转、避免组合环路、减少字长、二进制表示法、去掉逻辑云、其他RTL技术;

属于晶体管级的是:衬底偏置、版图优化、技术工艺优化、减少氧化厚度、多氧化器件,电容最小化。

一、为什么需要低功耗设计?低功耗设计的目的?

1.便携性设备等需求——提高电子产品的寿命

电子产品在我们生活中扮演了极其重要的作用,便携性的电子设备便是其中一种。便携性设备需要电池供电、需要消耗电池的能量。在同等电能提供下,低功耗设计的产品就能够工作更长的时间。时间的就是生命,因此低功耗设计是很重要的。便携性的设备需要低功耗设备,比如说手机,如果充电两小时,通话5分钟,这谁还买你的手机...

2.可靠性与性能的影响

设备消耗电能,会产生热量;消耗的能量越多,产生的热量越多。发热越严重,热噪声越大,就会影响器件的正常工作,导致电路不能正常工作。发热量的增加,可能会使工作在1G下的电路,只能工作在500M,这就影响了速度,这最常见的就是手机的发热了,手机发热之后,便感觉卡卡的。

3.成本的影响

如果不注意进行低功耗设计,那就可能导致后期的成本增加,从而导致整个系统的成本增加。例如,不进行低功耗设计,发热量就可能增加,在封装的时候,就需要考虑怎么给你这个芯片进行散热,从而增加了封装的散热成本。再比如,在进行系统组装的时候,如果那你的芯片功耗过大,就需要考虑在系统外给你进行散热,比如说添加一个风扇,发热很严重的甚至可以给你进行液体降温。这样子就在系统组装上面增加了组装成本。因此在设计初始进行低功耗设计是很重要的。

二、系统级低功耗设计:

- 软硬件划分

- 低功耗软件

- 合适的处理器

三、体系结构级低功耗设计:

1、多阈值电压设计Multi-Vt Design(静态低功耗技术)

低阈值的标准逻辑单元:速度快、漏电流大;

高阈值的标准逻辑单元:速度慢、漏电流小。

总结:在设计中可以在关键路径上使用低阈值的标准逻辑单元来优化时序,在非关键路径上使用高阈值的标准逻辑单元来优化漏电流。

优点:①可以大大减少系统的静态功耗;

②没有任何面积开销,工艺库设计是将两种阈值库中的相应单元的面积设计成一样,这样可以方便替换。

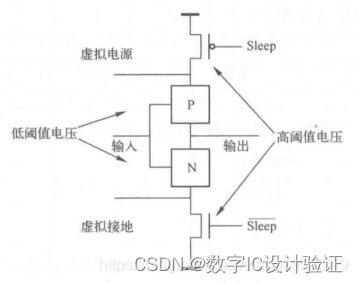

2、电源门控(Power Gating)(静态低功耗技术)

如上图所示,电源开关单元(Power Switch Cell)中的高阈值MOS管作为电源闸门,用来将低阈值电源和地隔离开。

在正常工作状态,Sleep信号为低电平,高阈值MOS管处于导通状态;当处于睡眠状态时,Sleep信号为高电平,切断电源,并且由于采用了高阈值MOS管作为开关,可以有效地减少漏电流。

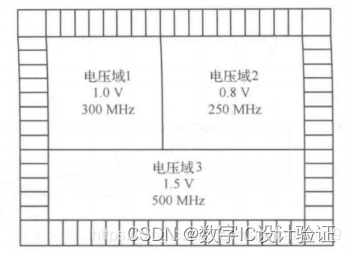

3、多电压域(Multi-Voltage Domain)(动态低功耗技术)

对于多电压域设计,要在不同的电压域之间使用一些电平转换单元(Level Shifter),将输入电压范围转换成输出需要的不同电压范围。

如果不同电压与之间的驱动信号与接受信号之间的距离很长,需要插入特殊的驱动单元(Repenter)来增强信号的驱动能力;如果不同的电压域可以单独断电(MV with Power Gating),还要考虑添加保持寄存器(Retention Register)和电压隔离单元(Isolation Cell)。

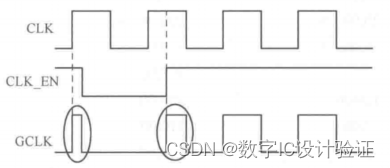

4、门控时钟(Clock Gating)

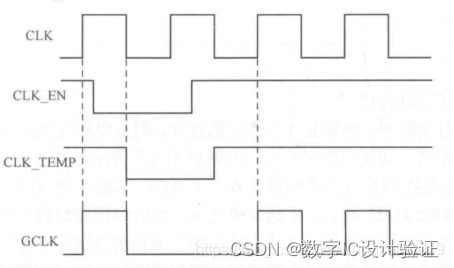

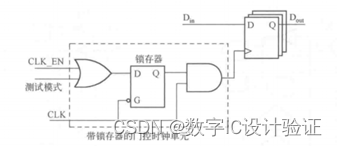

上图所示的门控时钟可能会产生毛刺。

使用锁存器的门控时钟可以避免毛刺。

5、DVFS技术

DVFS(Dynamic Voltage and Frequency Scaling)动态电压频率调节本质上是一种低功耗技术,目的是根据的芯片当时的实际功耗需要设定工作电压和时钟频率,这样可以保证提供的功率既满足要求又不会过剩,从而可以降低功耗。比如数字芯片中,CPU模块(比如8核cpu),在需要跑分的时候,将给cpu供电的电压通过软件调节到更高的电压(overdrive),获得一个更高的频率。在实际某个应用场景下,可能cpu只需要一个较低的频率时,可以将电压调节成一个较低的电压(underdrive)来实现

一味的降频降压当然是不能降低功耗的,因为低频下运行可能使系统处理任务的时长增加,从而整体上可能反而增加了功耗。所以DVFS的核心是动态调整的策略,其目的是根据当时的系统负载实时调整,从而提供满足当时性能要求的最低功率,也就达到了最低功耗。制定调整策略前,先找出系统中的耗电大户即CPU GPU这些模块。需要统计出这些模块的负载情况,基本的策略当然是工作负载增加则升频升压,工作负载降低则降频降压

-

寄存器传输级低功耗设计:

1、资源共享

其实就是复用。如果有同一个逻辑运算在多处使用时,就直接复用就行了,不要每一处都重新计算一次。

2、状态编码

多bit信号频繁变化时,使用一般的二进制计数法可能会产生很多翻转功耗,可以在状态机、高速变换的数据使用其他编码方式。

Grey码:

格雷码相邻之间只有1bit变化,相比二进制计数器翻转率得到了有效降低,状态机尽量还是用格雷码。

除此之外,格雷码还消除了二进制计数的毛刺问题,并且是多bit信号跨时钟域的最优解决方案。

独热码:

onehot码,指只有一位是1、其余位全是0的编码方式,常用于多路选择器MUX,同时在机器学习的数据特征处理中得到应用。

独热码的优势在于省去了译码电路,下面的例子就很能说明问题

-

晶体管级低功耗设计:

晶体管级的低功耗设计包括动态功耗设计和静态功耗设计。

动态功耗设计主要降低由晶体管的开关过程引起的功耗。静态功耗设计则主要关注降低晶体管的泄露电流。

本文探讨了电子产品低功耗设计的重要性,涉及系统级的软硬件划分、体系结构级的电压/频率调整和电源门控、寄存器传输级的资源共享和状态编码,以及晶体管级的动态与静态功耗控制方法。

本文探讨了电子产品低功耗设计的重要性,涉及系统级的软硬件划分、体系结构级的电压/频率调整和电源门控、寄存器传输级的资源共享和状态编码,以及晶体管级的动态与静态功耗控制方法。

4677

4677

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?