电子产品的续航能力越来越重要,而PCB布局设计直接影响功耗表现。四层板在复杂度和成本上平衡得较好,但要实现低功耗,必须从电源分配、信号完整性、热管理等多个维度优化。

1.叠层优化

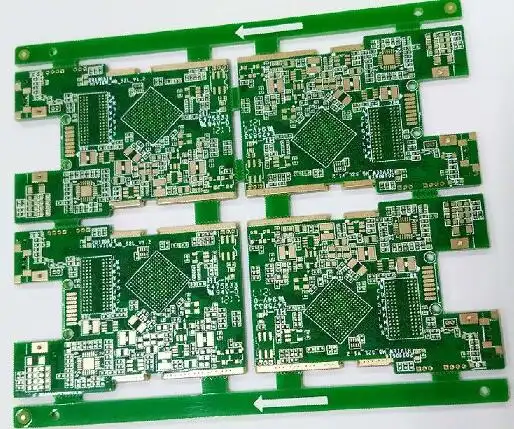

推荐叠层结构(Signal - GND - Power - Signal)

层序作用低功耗优化点L1(顶层)信号层(低速/控制线)减少高速信号,降低串扰功耗L2(地层)完整地平面提供低阻抗回流路径,减少地弹噪声L3(电源层)分割电源平面优化电源分配,降低IR DropL4(底层)信号层(关键高速信号)优先布放低摆幅信号(如LVDS、I2C)

关键点:

✅ 地平面必须完整(避免分割),否则回流路径变长,增加功耗。

✅ 电源平面合理分割,不同电压域之间留足够间距(≥20mil)。

2. 电源设计

(1)电源树优化

大电流路径优先:MCU、射频模块等耗电大户直接连电源入口。

小电流分支后置:传感器、LED等低功耗器件放末端。

(2)去耦电容布局

电容类型摆放位置作用大容量(10μF+)电源入口稳定DC电压中容量(1μF)每个IC的VCC引脚附近抑制中频噪声小容量(0.1μF)紧贴高速器件电源脚滤除高频瞬态电流

3. 信号完整性:减少不必要的"能量浪费"

(1)低速化设计

非关键信号降低速率(如GPIO从50MHz降至10MHz)。

使用上升沿缓和的驱动芯片(减少高频谐波损耗)。

(2)阻抗匹配

高速信号(USB/DDR)严格控阻抗(±10%)。

长走线端接匹配电阻(消除反射导致的重复充放电)。

实测数据:

阻抗失配的信号线,功耗可能增加15-25%!

4. 热管理

(1)高热器件布局

分散放置大功耗芯片(避免局部热点)。

敏感器件(如晶振)远离热源。

(2)散热通道设计

电源层大面积铺铜(兼作散热片)。

关键IC下方放置导热过孔阵列(直径0.3mm,间距1mm)。

行业经验:

温度从25℃升至85℃,MOSFET导通电阻增加40%,效率暴跌!

5. 低功耗器件选型技巧

器件类型选型要点省电效果MCU选择带动态调频功能(如STM32U5)休眠模式μA级LDO选低静态电流型号(如TPS7A02)待机功耗降低90%MOSFET低Rds(on)器件(如IPD90N04S4)减少导通损耗

总结:低功耗四层板设计口诀

🔋 叠层要对称,电源地完整

🔋 电容像保镖,贴身护芯片

🔋 信号低速化,阻抗严管控

🔋 发热均匀散,选型看静态

374

374

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?