目录

3.1.1.8PCIE参考时钟

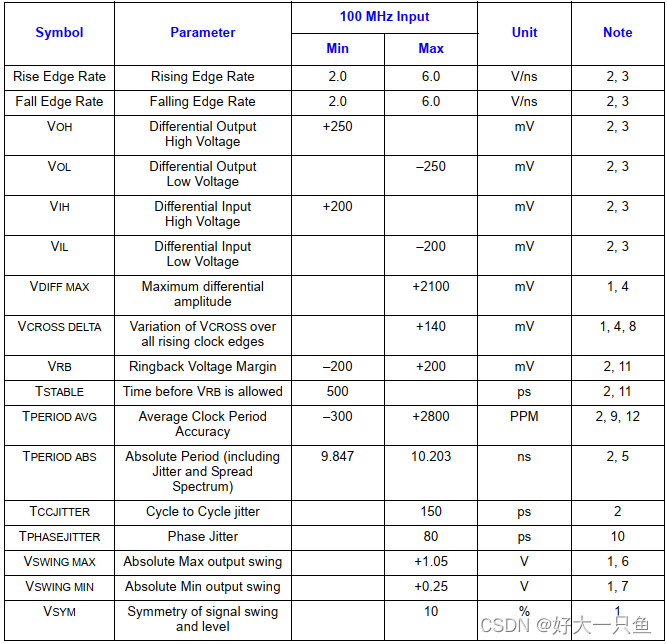

为了减少抖动、控制辐射和串扰,并考虑到未来硅制造工艺的变化,本规范使用低压摆幅差分时钟,如3.1.1.8.6节所示。

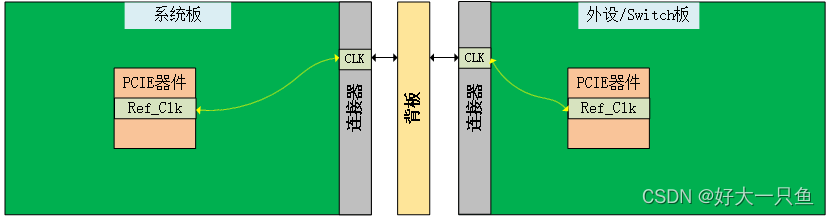

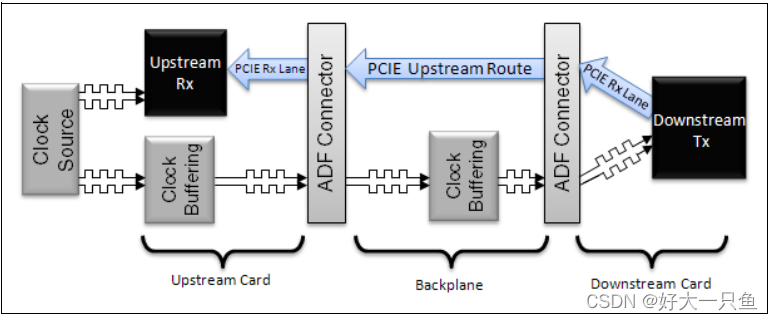

①参考时钟来自系统板,由外设板和/或Switch板的Upstream端口接收。

②参考时钟也可以来自Switch板,并由外设板和/或连接到其Downstream端口的Switch板接收。

系统板和Switch板提供的链路应有专用于该链路的100MHz参考时钟,以允许与下游外围槽位、Switch和Switch板进行点对点连接。系统板和Switch板可能被设计成链路与正确的100MHz参考时钟配对是很重要的。因此,背板应该这样布线:使连接器引脚中列出的编号Link分配布线到插槽或设备,布线到它的编号相同的100 MHz参考时钟,即时钟编号和Link编号应一一对应。

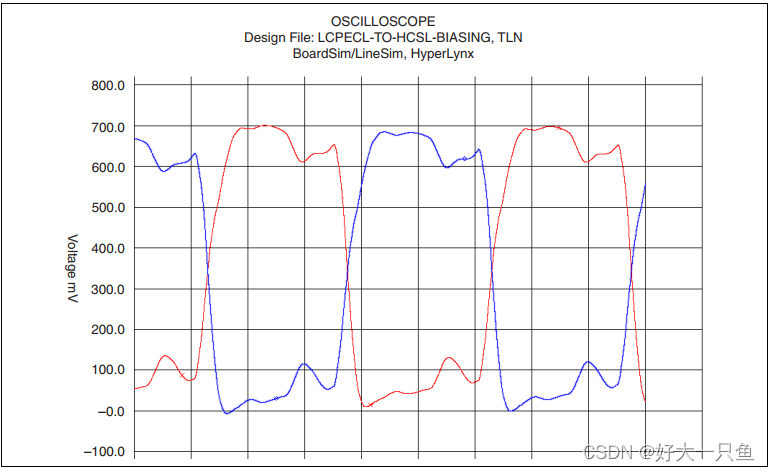

时钟 信号参数遵循标准LVPECL(低电压正射极耦合逻辑)驱动到背板。允许使用满足本章中提供的信号摆动、上升/下降时间、相位抖动和其他要求的其他逻辑系列。为了尽量减少系统板上的一个时钟对另一个时钟的干扰,以8GT/s运行的背板应端接任何未使用的由系统板提供的时钟。还建议时钟到没有插卡的外围板关闭空闲槽位的参考时钟输出。这使得时钟扇出设备的抖动性能最好。

第3.1.1.8.7节提供了一个参考时钟相位抖动规范,该规范应独立于时钟源和任何扇出要求来满足。

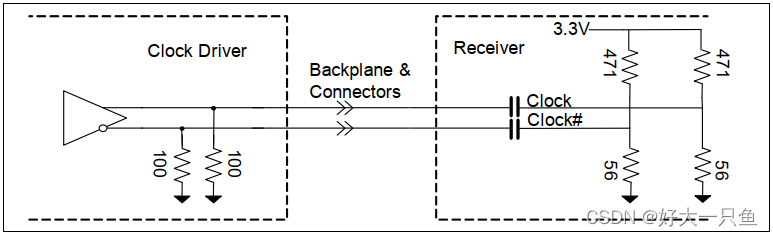

任何设计在板上或专有背板实现上的设备,并从背板接收参考时钟,应包括交流耦合,如章节3.1.1.8.4所述。器件还应包括将信号转换为适合接收PCI Express器件的偏置。关于交流耦合的章节提供了一个推荐的偏置网络,尽管电路板设计者必须保证信号完整性参数是满足的。

3.1.1.8.1 热拔插

时钟源可以提供时钟禁用功能,以允许未使用槽的时钟处于未激活状态。这减少或防止来自未端接时钟信号的电磁干扰。然而,系统设计时应考虑,在所有时钟信号是激活状态下应符合兼容性,与某个特定的插槽是否安装板卡无关。

支持热插拔的外设板应该提供一个时钟禁用机制,通过三态或强制到静态不激活级别,以防止任何未上电的PCI Express器件的损坏。MPWRGD可以用来控制时钟的启用和禁用。任何这样的时钟禁用机制应实现对相位抖动的影响最小。

3.1.1.8.2 时钟扇出

与大量支持PCI Express外设插槽的连接通常需要添加PCI Express Switch,作为标准板或专有实现,以提供必要的扇出。通过PCI Express树的扇形输出,必须生成参考时钟的副本,以保持点对点连接和信号完整性。

参考时钟的扇出应通过LVPECL或类似的器件来完成。LVPECL器件从常用的电源轨运行,如果实现正确,具有极低的附加相位抖动。

本规范中所有参考时钟相位抖动要求均应满足扇出器件和不满足扇出器件。

3.1.1.8.3 时钟依赖关系

该规范的主从实现(带有一个或多个外设板的系统控制器)使用为主流市场设计的PCI Express器件有特定的时钟要求。链路两端的端口传输数据的速率必须始终保持在600 ppm以内。这被要求为允许具有±300ppm偏差的码率时钟源。

针对1型外设槽的计算引擎设计和系统槽,应该提供控制,当安装在外设槽位时不驱动参考时钟到背板。支持这样的体系架构需要监视SYSEN#引脚。它必须基于这个配置本身,当插入到系统槽位时,将参考时钟驱动到背板上,或者当插入到类型1外设槽位时接收时钟。

3.1.1.8.3.1 扩频时钟(SSC)源

数据速率可在标称数据速率频率的+0% ~ 0.5%范围内进行调制,调制速率范围不超过30kHz ~ 33kHz。300ppm要求仍然存在,这要求对两个通信端口进行调制,使它们的差异总数永远不超过600ppm。对于大多数实现来说,这就要求在使用SSC调制数据时,链路的两个端口都需要相同的参考时钟源。

任何针对本规范的板设计都应支持SSC。

3.1.1.8.4 交流耦合和偏置

参考时钟在接收差分时钟的电路板上应该是交流耦合的。建议值为0.1 uF,尽管允许使用在第3.1.1.8.6节中提供的信号完整性和上升/下降时间规格内其他电容值。

在AC耦合之后,需要适当的偏置,以满足外设板上设计的PCI Express器件的输入要求。LVPECL电平标准的端接建议如图3-13和图3-14所示,将DC偏置电平转换为符合主流PCI Express器件的标准。

3.1.1.8.5走线长度

在接收器的数据流中嵌入的时钟和设备的参考时钟输入之间的相位延迟必须小于10ns。最大参考时钟不匹配和最大PCI Express通道长度的组合可能造成最大7ns延迟。剩余的时间分配给Tx和Rx设备内部插入延迟的差值。

系统控制器、外围设备、Switch和背板组件上的任何给定时钟对中的每个信号的走线必须在长度上很好地匹配(<0.005英寸【0.0127厘米】)。它还必须与其他非时钟信号保持适当的间隔,以避免过多的串扰。

主板上参考时钟差分对的路由长度应大于2英寸(5.08厘米)且不超过4英寸(10.16厘米)。

假设PCI Express的最大走线长度为20英寸(50.8 cm),在背板上实现的参考时钟布线的长度应在5英寸内匹配(12.7厘米)。这种匹配要求可以通过更短的PCI Express布线长度来放宽。不隐含特定的最小或最大布线长度。

3.1.1.8.6参考时钟规格

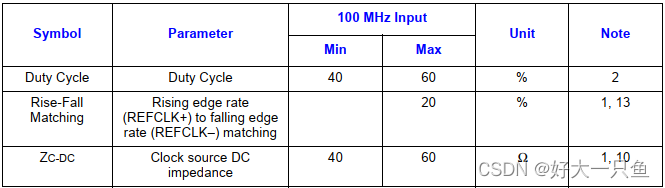

下表提供了时钟源连接器上的信号电平要求,以及接收机应该期望的最坏情况差分信号电平。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?