当前乘法器的设计主要有两种方式,Wallace树乘法器和booth编码乘法器。本篇主要讲述的是Wallace树乘法器。

1、算法讲解

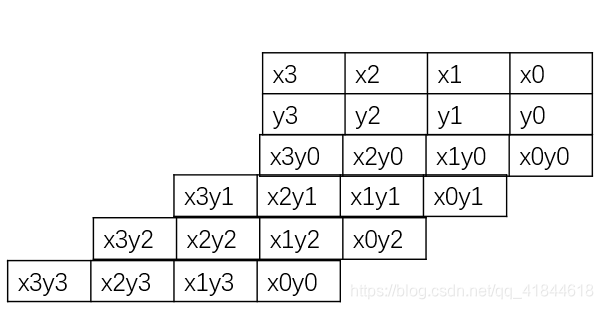

以4×4位乘法器为例,如表1-1所示,列出了各个部分的积

表1-1:

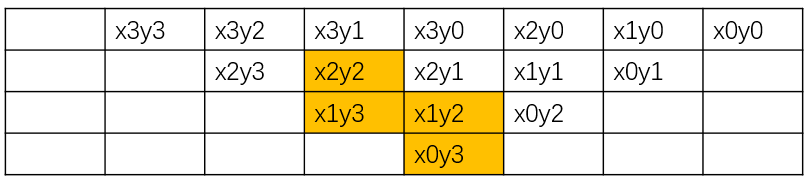

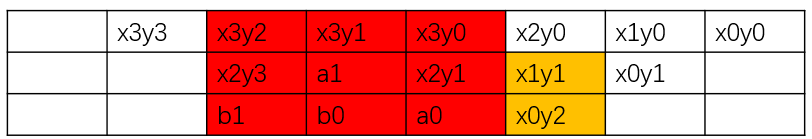

随后我们从数据最多的那一列开始,用半加器将数据最多有四个数据的那一列中的两个数相加,得到和a0以及向高列的进位b0,这时得到进位的那一列也有四个数据,我们也用半加器相加得到积a1和进位b0,如表1-2进行以上操作后可以的到表1-3所示。黄色表是半加器相加,红色表示全加器相加。

表1-2:

表1-3:

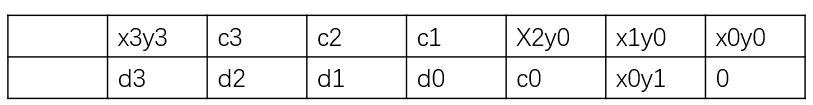

对于表1-3我们可以,用半加器和全加器反复压缩覆盖所有数据超过三个的列,得到表1-4所示的数据:

表1-4:

最后采用简单的2输入加法器,就可以得到相乘结果了。

2、Verilog HDL的实现

module wallace(x,y,out);

parameter size=4;

input [size-1:0]x,y;

output [size-1:0]out;

wire [size*size-1:0]a;

wire [1:0]b0,b1,c0,c1,c2,c3;

wire [5:0]add_a,add_b;

wire [6:0]kk;

wire [7:0]out;

assign a={

x[3],x[3],x[2],x[3],x[2],x[1]

本文介绍了Wallace树乘法器的算法原理,以4×4位乘法器为例,详细阐述了从数据最多的列开始,通过半加器和全加器逐步压缩求和的过程。此外,还探讨了使用Verilog HDL进行乘法器的硬件实现。

本文介绍了Wallace树乘法器的算法原理,以4×4位乘法器为例,详细阐述了从数据最多的列开始,通过半加器和全加器逐步压缩求和的过程。此外,还探讨了使用Verilog HDL进行乘法器的硬件实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1508

1508

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?