介绍

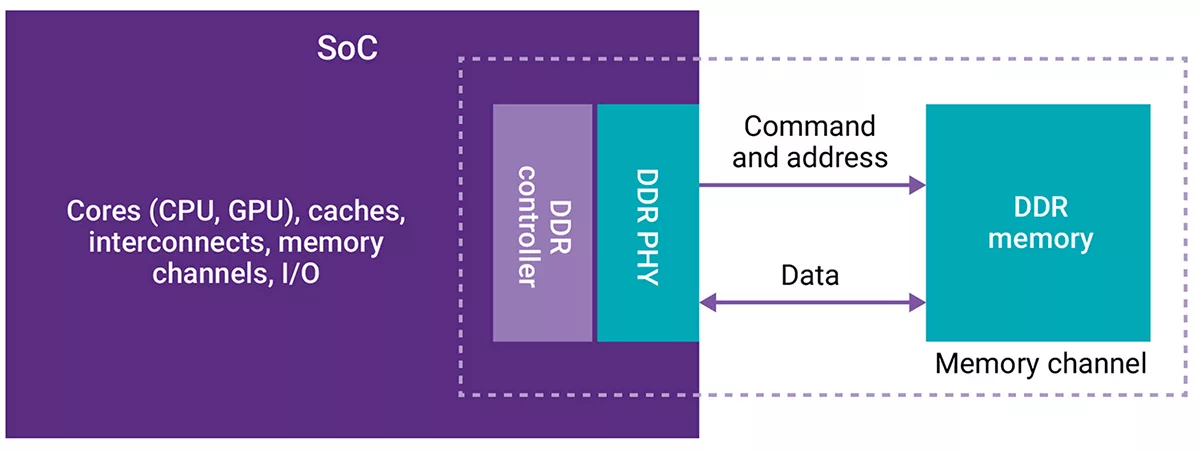

双倍数据速率同步动态随机存取存储器(DDR SDRAM 或简称 DRAM)技术是当今几乎所有应用中广泛用于主存储器的技术,从高性能计算 (HPC) 到功耗、面积敏感型移动应用。这是由于 DDR 的许多优势,包括高密度、简单的架构、低延迟和低功耗。JEDEC 是指定内存标准的标准组织,它定义并开发了四个 DRAM 类别,以指导设计人员精确满足其内存要求:标准 DDR (DDR5/4/3/2)、移动 DDR (LPDDR5/4/3/2)、图形 DDR (GDDR3/4/5/6) 和高带宽 DRAM (HBM2/2E/3)。图 1 显示了典型片上系统 (SoC) 中内存子系统的高级框图,其中包括 DDR 内存控制器、DDR PHY、DDR 通道和 DDR 内存。根据 JEDEC 的定义,DDR 通道由命令/地址和数据通道组成。下面显示的简化 DDR 内存可以表示四个类别中任何一个类别的 DRAM 内存组件。

与任何电子系统一样,由于任何一个组件中的设计故障/缺陷或电气噪声,内存子系统中的错误都可能发生。这些错误分为硬错误(由设计失败引起)或软错误(由系统噪声或 alpha 粒子引起的内存阵列位翻转等)。顾名思义,硬错误是永久性的,而软错误本质上是暂时性的。尽管 DRAM(具有大型内存阵列,并且随着较小工艺节点的每次标准生成而变得越来越密集)成为内存错误的主要来源是合乎逻辑的,但从控制器到 DRAM 的端到端保护对于整体内存子系统的稳健性是非常可取的。

要在运行时处理这些内存错误,内存子系统必须具有高级 RAS(可靠性、可用性和可维护性)功能,以便在出现内存错误时延长整体系统正常运行时间。如果没有 RAS 功能,系统很可能会因内存错误而崩溃。但是,RAS 功能允许系统在出现可纠正的错误时继续运行,同时记录不可纠正的错误详细信息以备将来调试。

ECC 作为内存 RAS 功能

内存子系统中使用的最流行的 RAS 方案之一是纠错码 (ECC) 内存。通过为实际数据生成 ECC SECDED(单位纠错和双位错误检测)代码并将其存储在额外的 DRAM 存储器中,DDR 控制器可以纠正单位错误并检测从 DRAM 接收的数据上的双位错误。

ECC 生成和检查顺序如下:

- ECC 代码由控制器根据实际的 WR (WRITE) 数据生成。内存存储 WR 数据和 ECC 代码。

- 在 RD (READ)作期间,控制器从内存中读取数据和相应的 ECC 代码。控制器从接收到的数据中重新生成 ECC 代码,并将其与接收到的 ECC 代码进行比较。

- 如果存在匹配项,则未发生错误。如果存在不匹配,ECC SECDED 机制允许控制器纠正任何单位错误并检测双位错误。

这种 ECC 方案提供端到端保护,防止 1 位错误,这些错误可能发生在 controller 和 memory 之间的内存子系统中的任何位置。

根据 ECC 代码的实际存储情况,ECC 方案可以有两种类型:边带 ECC 或内联 ECC。在边带 ECC 中,ECC 代码存储在单独的 DRAM 上,而在内联 ECC 中,代码与实际数据存储在相同的 DRAM 上。

由于 DDR5 和 LPDDR5 支持比其前代产品高得多的数据速率,因此它们支持额外的 ECC 功能,以增强内存子系统的稳健性。DDR5 中的 On-die ECC 和 LPDDR5 中的 Link-ECC 是两种这样的 RAS 方案,可进一步增强内存子系统的 RAS 功能。

ECC 的不同方案

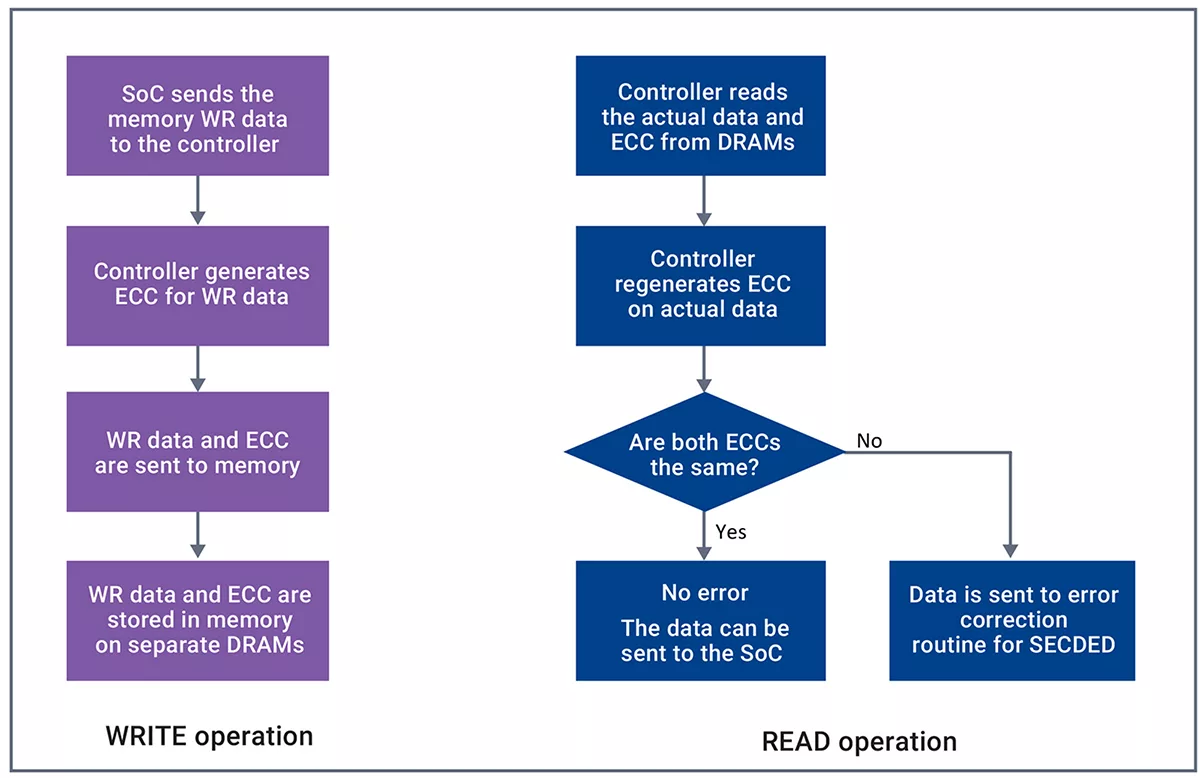

边带 ECC

边带 ECC 方案通常在使用标准 DDR 存储器(如 DDR4 和 DDR5)的应用中实现。顾名思义,ECC 代码作为边带数据与实际数据一起发送到内存。例如,对于 64 位数据宽度,8 个额外的位用于 ECC 存储。因此,当今企业级服务器和数据中心常用的 DDR4 ECC DIMM 宽度为 72 位。这些 DIMM 具有两个额外的 x4 DRAM 或一个 x8 DRAM,用于额外的 8 位 ECC 存储。因此,在边带 ECC 中,控制器将 ECC 代码与实际数据一起写入和读取。此 ECC 方案不需要额外的 WR 或 RD 开销命令。图 2 描述了使用边带 ECC 的 WR 和 RD作流程。当接收到的数据中没有错误时,与内联 ECC 相比,边带 ECC 的延迟损失最小。

图 2:使用边带 ECC 的 WR 和 RD作流程

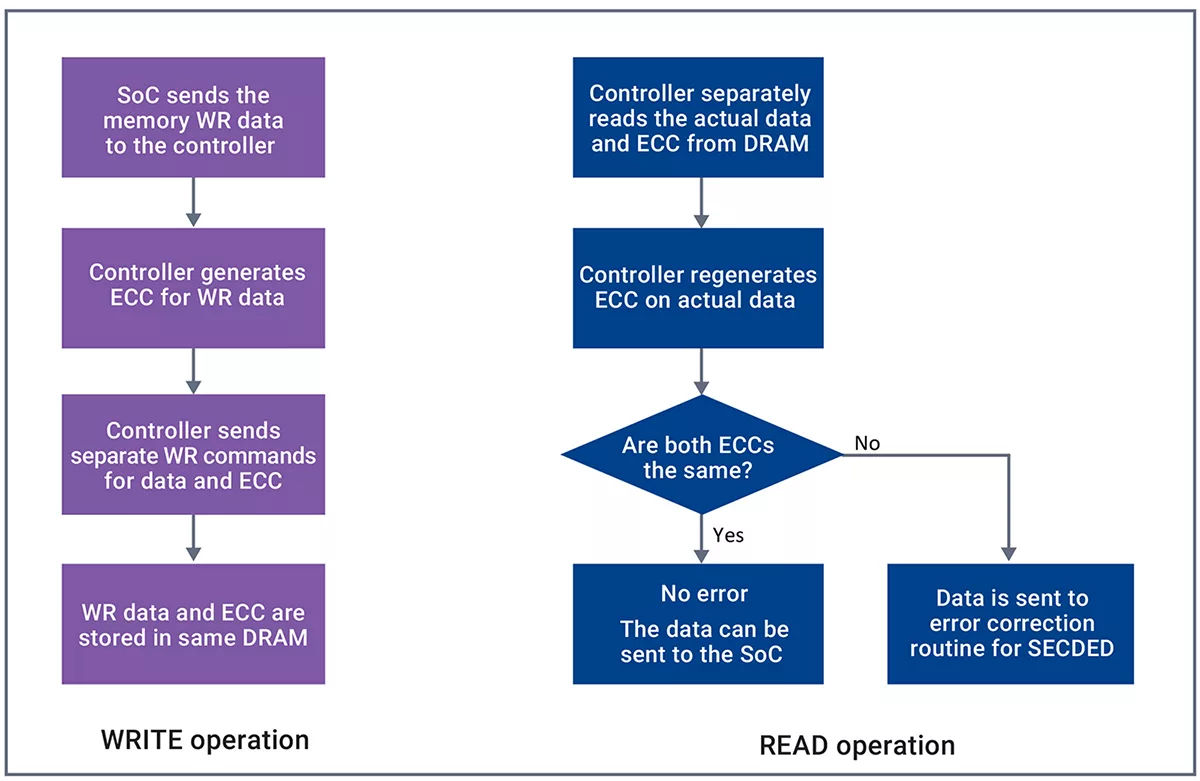

内联 ECC

内联 ECC 方案通常在使用 LPDDR 存储器的应用中实现。由于 LPDDR DRAM 具有固定通道宽度(LPDDR5/4/4X 通道为 16 位),因此边带 ECC 成为这些存储器的昂贵解决方案。例如,对于 16 位数据宽度,需要为 7 位或 8 位 ECC 码字的边带 ECC 分配一个额外的 16 位 LPDDR 通道。此外,7 位或 8 位 ECC 代码字仅部分填充 16 位附加通道,导致存储效率低下,还会给地址命令通道增加额外负载,从而可能限制性能。因此,Inline ECC 成为 LPDDR 内存的更好解决方案。

内联 ECC 中的控制器不需要额外的 ECC 存储通道,而是将 ECC 代码存储在存储实际数据的同一 DRAM 通道中。因此, memory channel 的总体 data-width 与实际 data-width 相同。

在内联 ECC 中,对 16 位通道内存进行分区,以便将内存的专用部分分配给 ECC 代码存储。当 ECC 代码未与 WR 和 RD 数据一起发送时,控制器会为 ECC 代码生成单独的开销 WR 和 RD 命令。因此,实际数据的每个 WR 和 RD 命令都分别伴随着一个用于 ECC 数据的开销 WR 和 RD 命令。高性能控制器通过将多个连续地址的 ECC 数据打包到一个开销 ECC WR 命令中,减少了此类开销 ECC 命令的损失。同样,控制器在一个开销 ECC RD 命令中从内存中读取多个连续地址的 ECC 数据,并且可以将读出的 ECC 数据应用于来自连续地址的实际数据。因此,流量模式的连续性越高,由于此类 ECC 开销命令造成的延迟损失就越小。图 3 描述了使用内联 ECC 的 WR 和 RD作流程。

图 3:使用内联 ECC 的 WR 和 RD作流程

On-die ECC

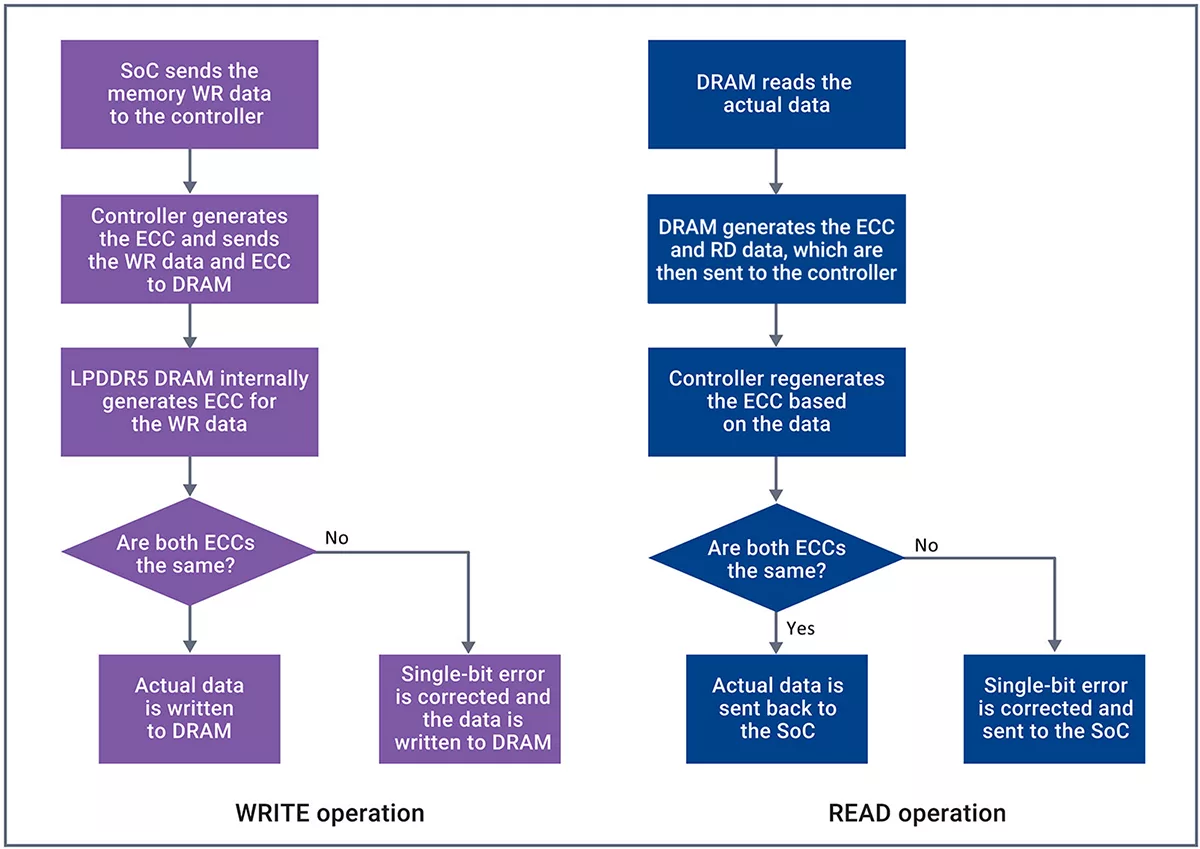

每一代 DDR 都会增加 DRAM 容量。DRAM 供应商缩小工艺技术以实现更高的速度和更好的生产规模经济也很常见。随着更高的容量和速度以及更小的工艺技术,DRAM 内存阵列上出现单位错误的可能性会增加。为了进一步增强内存通道,DDR5 DRAM 具有仅用于 ECC 存储的额外存储。On-die ECC 是一种先进的 RAS 功能,DDR5 系统可以实现更高的速度。对于每 128 位数据,DDR5 DRAM 有 8 个额外的 ECC 存储位。

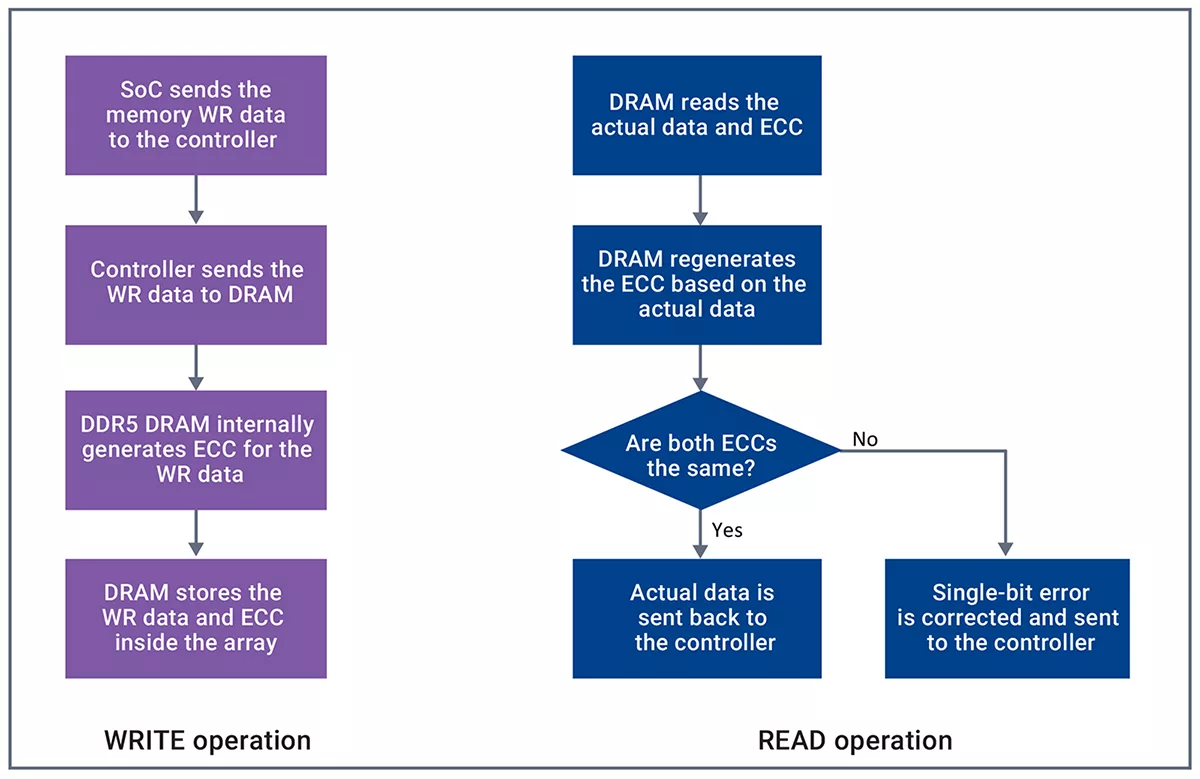

DRAM 在内部计算 WR 数据的 ECC,并将 ECC 代码存储在额外的存储中。在读取作中,DRAM 会读出实际数据和 ECC 代码,并且可以纠正任何读取数据位上的任何单位错误。因此,片上 ECC 提供了进一步的保护,防止 DDR5 内存阵列内部的单位错误。由于该方案不提供任何保护,防止 DDR 通道上发生的错误,因此片上 ECC 与边带 ECC 结合使用,以增强内存子系统上的端到端 RAS。图 4 描述了使用片上 ECC 的 WR 和 RD作流程。

图 4:使用 On-die ECC 的 WR 和 RD作流程

链路 ECC

Link-ECC 方案是 LPDDR5 的一项功能,可防止 LPDDR5 链路或通道上的单位错误。内存控制器计算 WR 数据的 ECC,并将特定位上的 ECC 与数据一起发送。DRAM 在接收到的数据上生成 ECC,根据接收到的 ECC 数据进行检查,并纠正任何单位错误。对于读取作,控制器和 DRAM 的角色是相反的。请注意,link-ECC 不提供任何针对内存阵列上单位错误的保护。然而,内联 ECC 与链路 ECC 相结合,通过提供针对单位错误的端到端保护,增强了 LPDDR5 通道的稳健性。图 5 描述了使用 link-ECC 的 WR 和 RD作流程。

图 5:使用 Link-ECC 的 WR 和 RD作流程

结论

广泛使用的内存 RAS 功能之一是纠错码 (ECC) 方案。使用标准 DDR 存储器的应用程序通常实现边带 ECC,而使用 LPDDR 存储器的应用程序则实现内联 ECC。

729

729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?