DDR ECC的使用

DDR注入错误测试

DDR先刷一遍0,ECC_STATUS,ECC_ON_OF初始化为0,数据注入错误,写DDR,读DDR。

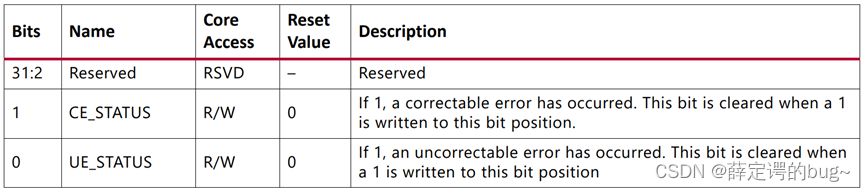

ECC_STATUS

该寄存器保存有关可纠正和不可纠正错误发生的信息。状态位独立地设置为1,表示每种错误类型的第一次发生。状态位可以通过向相应的位位置写入1来清除,但不能通过寄存器写入设置为1。ECC状态寄存器独立于ECC使能中断寄存器运行。

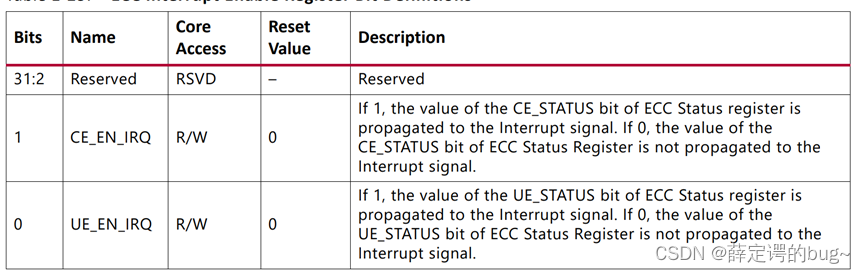

ECC_EN_IRQ

该寄存器确定ECC状态寄存器中的CE_STATUS和UE_STATUS位的值是否触发中断输出信号。如果CE_EN_IRQ和UE_EN_IRQ都被启用,则中断信号的值为CE_STATUS和UE_STATUS位之间的逻辑或。

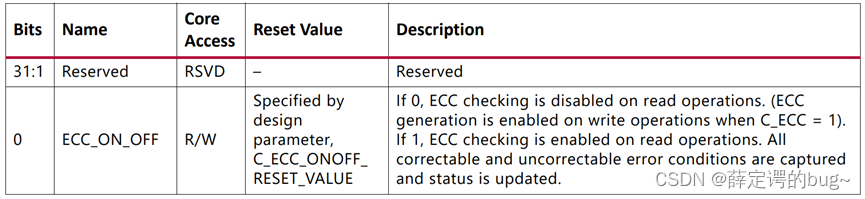

ECC_ON_OF

ECC开/关控制寄存器允许应用程序启用或禁用ECC检查。设计参数C_ECC_ONOFF_RESET_VALUE确定ECC的启用/禁用设置的复位值。当禁用时,读取操作的ECC检查被禁用,但写入操作的ECC生成仍然有效。

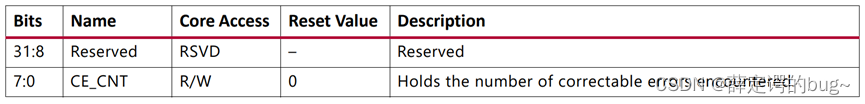

CE_CNT

该寄存器计算可纠正错误发生的次数,可以使用寄存器写入清除或预设为任何值。当计数器达到最大值时,它不会翻转,而是停止递增并保持在最大值。计数器的宽度由C_CE_COUNTER_WIDTH参数定义,固定为8位。

CE_FFA[31:0]

该寄存器存储第一次发生可纠正错误的访问的地址(位[31:0])。当ECC状态寄存器中的CE_STATUS位被清除时,此寄存器重新启用,以存储下一个可纠正错误的地址。复位后启用失败地址的存储。

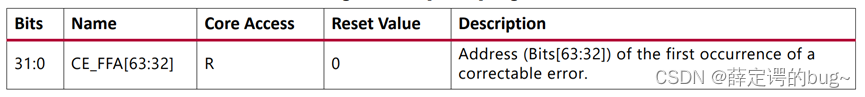

CE_FFA[63:32]

注意:如果 C_S_AXI_ADDR_WIDTH < 33,那么这个寄存器将不会被使用。

这个寄存器存储了第一次出现可纠正错误的访问的地址(位[63:32])。当ECC状态寄存器中的CE_STATUS位被清除时,这个寄存器会重新启用,以存储下一个可纠正错误的地址。在复位后启用失败地址的存储。

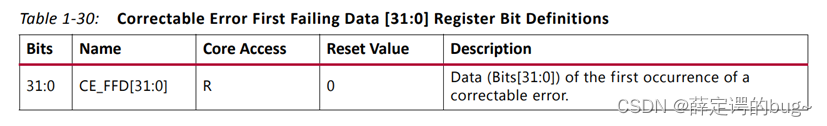

CE_FFD[31:0]

这个寄存器存储了第一次出现可纠正错误的访问的(已纠正的)失败数据(位[31:0])。当ECC状态寄存器中的CE_STATUS位被清除时,这个寄存器会重新启用,以存储下一个可纠正错误的数据。在复位后启用失败数据的存储。

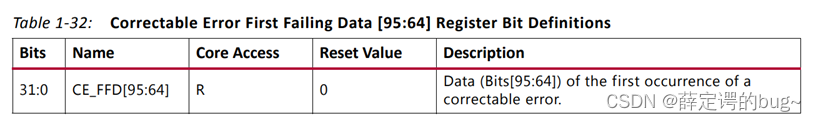

CE_FFD[63:32]

这个寄存器存储了第一次出现可纠正错误的访问的(已纠正的)失败数据(位[63:32])。当ECC状态寄存器中的CE_STATUS位被清除时,这个寄存器会重新启用,以存储下一个可纠正错误的数据。在复位后启用失败数据的存储。

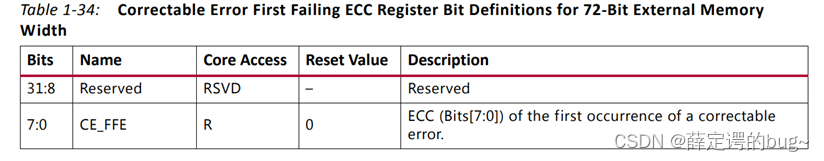

CE_FFE

这个寄存器存储了第一次出现可纠正错误的访问的ECC位。当ECC状态寄存器中的CE_STATUS位被清除时,这个寄存器重新启用,以存储下一个可纠正错误的ECC。复位后启用失败ECC的存储。

表1-34描述了当DQ_WIDTH = 72时寄存器位的使用情况。

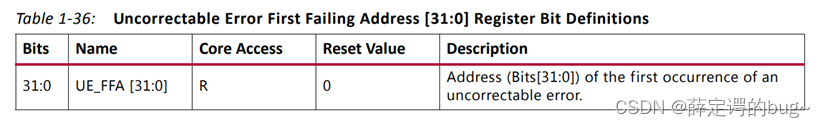

UE_FFA[31:0]

这个寄存器存储了第一次发生不可纠正错误的访问的地址(位[31:0])。当 ECC 状态寄存器中的 UE_STATUS 位被清除时,这个寄存器重新启用,以存储下一个不可纠正错误的地址。复位后启用失败地址的存储。

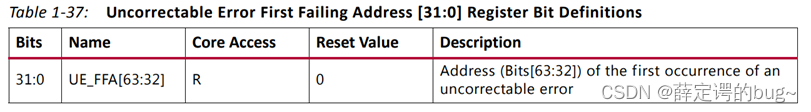

UE_FFA[63:32]

注意:如果 C_S_AXI_ADDR_WIDTH < 33,这个寄存器是未使用的。

这个寄存器存储了第一次出现不可纠正错误的访问的地址(位[63:32])。当 ECC 状态寄存器中的 UE_STATUS 位被清除时,这个寄存器重新启用,以存储下一个不可纠正错误的地址。复位后启用失败地址的存储。

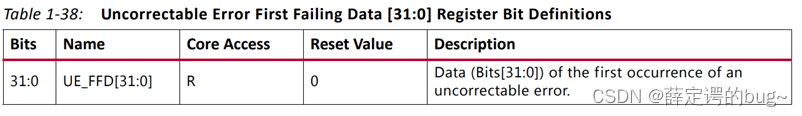

UE_FFD[31:0]

这个寄存器存储了第一次出现不可纠正错误的访问的(未纠正的)失败数据(位[31:0])。当 ECC 状态寄存器中的 UE_STATUS 位被清除时,这个寄存器重新启用,以存储下一个不可纠正错误的数据。复位后,启用失败数据的存储。

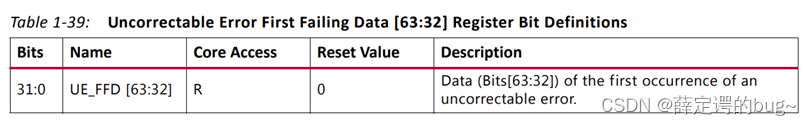

UE_FFD[63:32]

这个寄存器存储了第一次发生不可纠正错误的访问的(未纠正的)失败数据(位[63:32])。当ECC状态寄存器中的UE_STATUS位被清除时,这个寄存器重新启用,以存储下一个不可纠正错误的数据。复位后启用失败数据的存储。

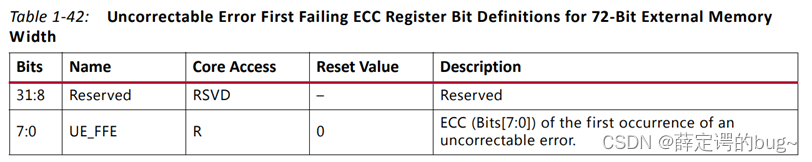

UE_FFE

这个寄存器存储了第一次发生不可纠正错误的访问的ECC位。当ECC状态寄存器中的UE_STATUS位被清除时,这个寄存器重新启用,以存储下一个不可纠正错误的ECC。复位后启用失败ECC的存储。

表1-42描述了当DQ_WIDTH = 72时寄存器位的使用情况。

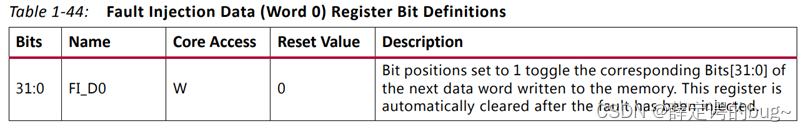

FI_D0

这个寄存器用于在写入内存的数据(Bits[31:0])中注入错误,可以用于测试错误纠正和错误信号。寄存器中设置的位会切换相应的数据位(字0或Bits[31:0]),而不影响写入的ECC位。注入故障后,故障注入数据寄存器会自动清零。

该寄存器只有在Vivado IP目录中的MIG设计中,当C_ECC_TEST = “ON” 或 ECC_TEST_FI_XOR = “ON” 且 ECC = “ON” 时才会实现。

注入故障应该在软件中的一个关键区域进行;也就是说,写入这个寄存器和随后写入内存的操作不能被中断。

必须特别考虑 FI_D0、FI_D1、FI_D2 和 FI_D3,以便仅引入单一错误条件。

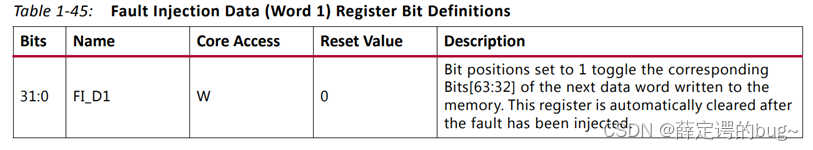

FI_D1

这个寄存器用于在写入内存的数据(位[63:32])中注入错误,可以用于测试错误纠正和错误信号。寄存器中设置的位会切换相应的数据位(字1或位[63:32])的后续写入内存的数据,而不影响写入的ECC位。注入故障后,故障注入数据寄存器会自动清零。这个寄存器只有在Vivado IP目录中的MIG设计中,如果C_ECC_TEST = “ON”或ECC_TEST_FI_XOR = “ON”且ECC = “ON”,才会实现。注入故障应该在软件中的一个关键区域执行;也就是说,写入这个寄存器和后续写入内存的操作不能被中断。

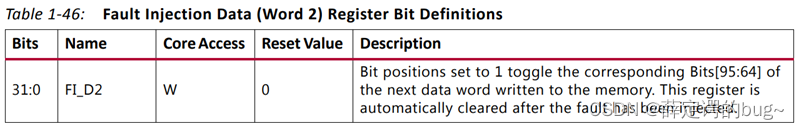

FI_D2

注意:这个寄存器只有在DQ_WIDTH = 144时才使用。

这个寄存器用于在写入内存的数据(位[95:64])中注入错误,可以用于测试错误纠正和错误信号。寄存器中设置的位会切换相应的数据位(字2或位[95:64])的后续数据写入内存,而不影响写入的ECC位。注入故障后,故障注入数据寄存器会自动清零。

这个寄存器只有在Vivado IP目录中的MIG设计中,当C_ECC_TEST = “ON”或ECC_TEST_FI_XOR = “ON”且ECC = “ON”时才实现。

注入故障应该在软件中的一个关键区域执行;也就是说,写入这个寄存器和随后的写入内存的操作不能被中断。

特别注意,在 FI_D0、FI_D1、FI_D2 和 FI_D3 之间必须给予特殊考虑,以便只引入单个错误条件。

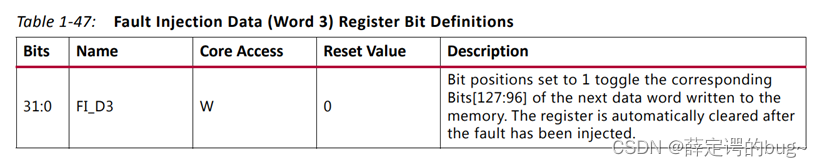

FI_D3

这个寄存器只有在DQ_WIDTH = 144时才使用。

这个寄存器用于在写入内存的数据(位[127:96])中注入错误,可以用于测试错误纠正和错误信号。寄存器中设置的位会切换相应的数据位(字3或位[127:96])的后续写入内存的数据,而不影响写入的ECC位。注入故障后,故障注入数据寄存器会自动清除。

该寄存器只有在C_ECC_TEST = “ON”或ECC_TEST_FI_XOR = “ON”且ECC = “ON”时,在Vivado Design Suite中的MIG设计中才实现。

注入故障应该在软件中的一个关键区域进行;也就是说,写入这个寄存器和随后写入内存的操作不能被中断。

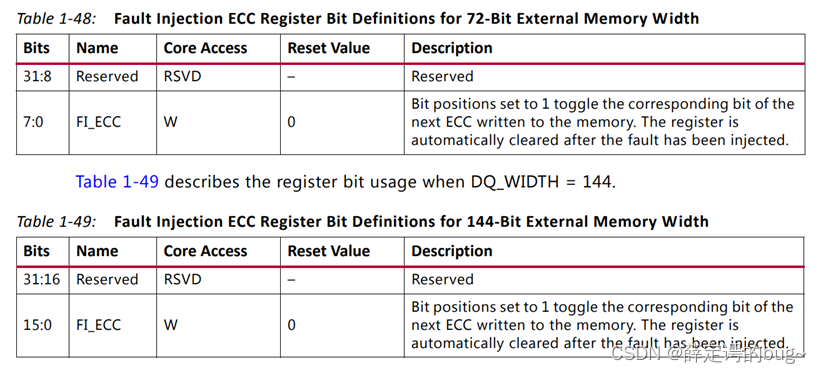

FI_ECC

这个寄存器用于在写入内存的生成的ECC中注入错误,可以用于测试错误纠正和错误信号。寄存器中设置的位会切换下一次写入内存的数据的相应的ECC位。注入故障后,故障注入ECC寄存器会自动清零。

这个寄存器只有在Vivado IP目录中的MIG设计中,C_ECC_TEST = “ON” 或 ECC_TEST_FI_XOR = “ON” 且 ECC = “ON” 时才会实现。

注入故障应该在软件中的一个临界区域进行;也就是说,写入这个寄存器和随后的写入内存的操作不能被中断。

表1-48描述了当DQ_WIDTH = 72时,寄存器位的用法。

本文详细介绍了DDR内存中的ECC(ErrorCorrectingCode)功能,包括ECC_STATUS、ECC_ON_OFF控制、错误计数器、错误发生地址和数据存储寄存器,以及用于测试错误纠正的FI_D0至FI_ECC寄存器。着重讨论了这些寄存器的用途和操作注意事项。

本文详细介绍了DDR内存中的ECC(ErrorCorrectingCode)功能,包括ECC_STATUS、ECC_ON_OFF控制、错误计数器、错误发生地址和数据存储寄存器,以及用于测试错误纠正的FI_D0至FI_ECC寄存器。着重讨论了这些寄存器的用途和操作注意事项。

735

735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?