为了在运行时处理这些内存错误,内存子系统必须具有先进的 RAS(可靠性、可用性和可维护性)功能,以在发生内存错误时进行修正,延长整个系统的正常运行时间。如果没有 RAS 功能,系统很可能会因为内存错误而崩溃。但是,RAS 功能允许系统在出现可纠正的错误时继续运行,同时记录不可纠正错误的详细信息,以便将来进行调试。

作为内存 RAS 功能的 ECC

内存子系统中较常用的一种 RAS 方案是纠错码 (ECC) 内存。DDR 控制器通过为实际数据生成 ECC SECDED(单位纠错和双位检错)数据并存储到附加 DRAM 存储器中,可以对 DRAM 发送的数据进行单位纠错和双位检错。

ECC 生成和校验顺序如下:

ECC 数据由控制器根据实际的 WR(写入)数据生成。内存同时存储写命令的数据和 ECC 数据。

在 RD(读取)操作期间,控制器从内存读取数据和相应的 ECC 数据。控制器利用接收到的数据重新生成 ECC 数据,并将其与接收到的 ECC 数据进行比较。

如果两者匹配,则不会发生错误。如果不匹配,ECC SECDED 机制允许控制器纠正任何单 bit 错误并检测双 bit 错误。

这种 ECC 方案提供端到端的保护,以防止可能在控制器和内存之间的内存子系统中发生的单 bit 错误。

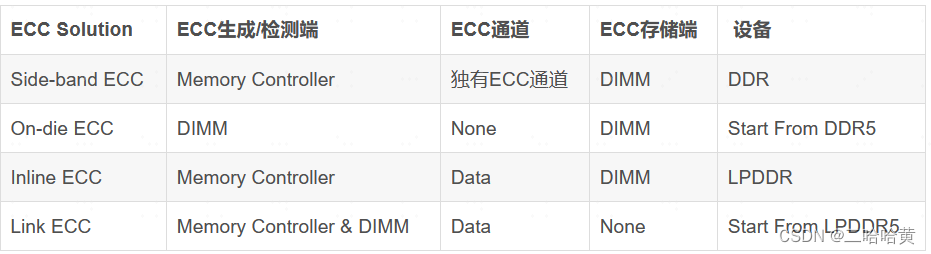

基于 ECC 的实际存储,ECC 方案可能有两种类型:side-band ECC 或 inline ECC。在 side-band ECC 中,ECC 数据存储在单独的 DRAM 上;在inline ECC 中,ECC 数据与实际数据一起存储在同一个 DRAM 上。

DDR5 和 LPDDR5 支持的数据速率远高于其前代产品,因此它们支持更多 ECC 功能,以增强内存子系统的稳定性。DDR5 中的 On-die ECC 和 LPDDR5 中的 Link ECC 就是两种此类 RAS 方案,可进一步增强内存子系统 RAS 功能。

Side-band ECC

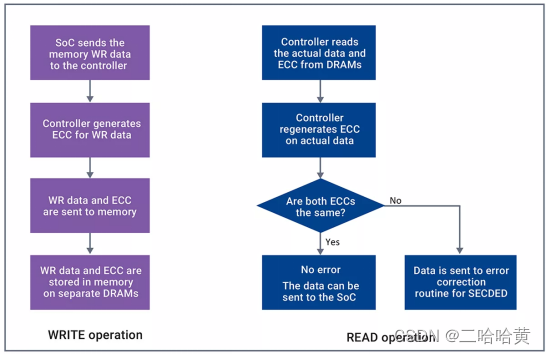

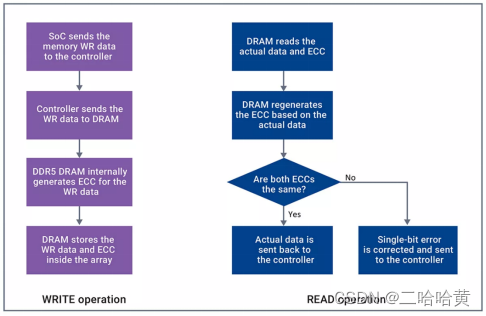

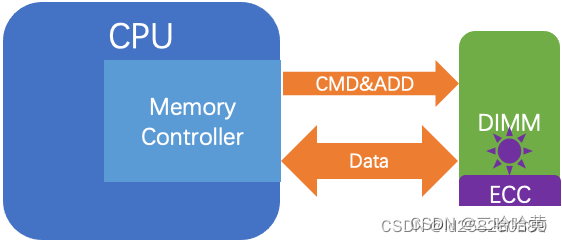

side-band ECC 方案通常在应用中使用标准 DDR 内存(如 DDR4 和 DDR5)实现。顾名思义,ECC 数据作为边带数据连同实际数据发送到内存。例如,对于 64 位数据宽度,增加 8 个数位用于 ECC 存储。因此,当今企业级服务器和数据中心常用的 DDR4 ECC DIMM 具有 72 位宽。这些 DIMM 有两个额外的 x4 DRAM 或一个 x8 DRAM,用于额外的 8 位 ECC 存储。因而在 side-band ECC 中,控制器会同时读写 ECC 数据和实际数据。此 ECC 方案不需要额外的 WR 或 RD 开销命令。图 2 描述了 side-band ECC 的 WR 和 RD 操作流程。如果接收的数据没有错误,side-band ECC 与 inline ECC 相比,延时损失更小。

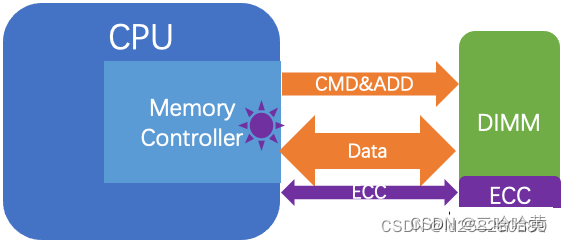

Side-band ECC即为标准DDR 内存的ECC,如上图,ECC的生成和校验均由Memory Controller来完成,Data通道宽度为64-bit,有额外专门的8-bit ECC通道(一共72-bit),DIMM端也有专门的颗粒存储ECC。读写操作如下:

写:Memory Controller会根据64-bit Data计算出ECC,再经ECC通道写入DIMM端ECC位置。

读:Memory Controller会读取Data和ECC,Memory Controller再根据Data计算出ECC,然后通过对比读取的ECC和计算出的ECC进行校验

图 2:side-band ECC 的 WR 和 RD 操作流程

Inline ECC

Inline ECC 方案通常在使用 LPDDR 内存的应用中实现。LPDDR DRAM 具有固定信道宽度(LPDDR5/4/4X 信道宽度为 16 位),因此 side-band ECC 对于此类内存而言是一种昂贵的解决方案。例如,对于 16 位数据宽度,需要为 7 位或 8 位 ECC 位宽的 inline ECC 额外分配 16 位 LPDDR 信道。此外,7 或 8 位 ECC 数据字段仅部分填充了 16 位额外的通路,导致存储效率低下,还给地址命令信道带来额外负载,可能会对性能有所影响。因此,inline ECC 成为更适合用作 LPDDR 内存的解决方案。

Inline ECC 中的控制器不需要额外的信道来存储 ECC,而是将 ECC 数据存储在存储实际数据的同一 DRAM 信道中。因此,内存信道的总体数据宽度与实际数据宽度相同。

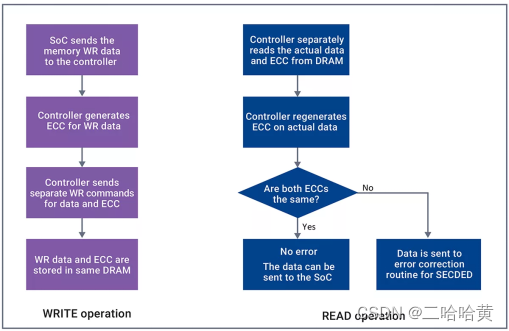

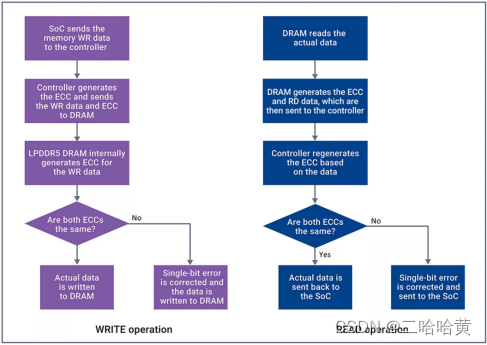

在 inline ECC 中,16 位信道内存被分区,使得内存的专用部分被分配给 ECC 数据存储。当 ECC 数据未与读写数据一起发送时,控制器为 ECC 数据生成单独的开销 WR 和 RD 命令。因此,实际数据的每条 WR 和 RD 命令都伴有一条 ECC 数据的开销 WR 和 RD 命令。高性能控制器通过在一条 ECC WR 命令中封装几个连续地址的 ECC 数据,以此来降低此类 ECC 命令的损失。同样,控制器在一条 ECC RD 命令中读取内存发出的若干连续地址的 ECC 数据,并且可以将读出的 ECC 数据,应用于该连续地址产生的实际数据。因此,流量模式越有序,此类 ECC 开销命令造成的延迟损失越小。图 3 描述了 inline ECC 的 WR 和 RD 操作流程。

图 3:Inline ECC 的 WR 和 RD 操作流程

inlineECC的原理是(8,4)汉明码

Inline ECC为LPDDR中传统的ECC方案,LPDDR数据宽度为16-bit,Inline ECC没有额外的ECC通道,所以需要额外增加ECC数据的读写操作来传输ECC,ECC数据一样被写到DIMM端,这样影响了效率,对性能也产生了影响。具体读写操作如下:

写:Memory Controller根据Data计算出ECC,Memory Controller通过不同的命令将Data和ECC分别传送至DIMM。

读:Memory Controller用不同的命令从DIMM端读取Data和ECC,Memory Controller根据Data再次计算出ECC,比较读取的ECC和计算出的ECC进行校验。

On-die ECC

每一代 DDR 的发展,DRAM 容量通常都会增加。DRAM 供应商通常也会缩小工艺技术,以实现更高的速度和更经济的量产。面对更高的容量和速度以及更小的工艺技术,DRAM 内存阵列出现单位错误的可能性会增加。为进一步改善内存信道,DDR5 DRAM 配备额外的存储器,只用于 ECC 存储。On-die ECC 是一种高级 RAS 功能,可获得 DDR5 系统的支持以实现更高的速度。DDR5 DRAM 为每 128 位数据额外设置 8 位的 ECC 存储空间。

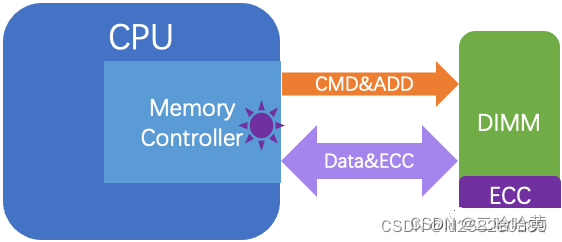

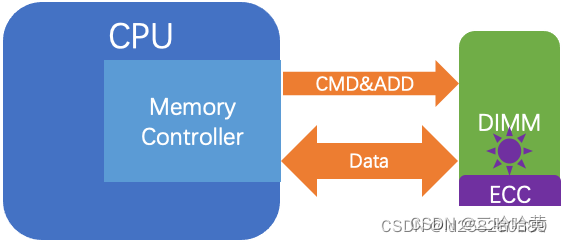

DRAM 内部计算 WR 数据的 ECC,并将 ECC 数据存储在额外的存储器中。在读取操作中,DRAM 读出实际数据以及 ECC 数据,并且可以纠正任何读数据位上的任何单位错误。因此,on-die ECC 进一步保护 DDR5 内存阵列免于产生单位错误。由于此方案无法针对 DDR 信道上发生的错误提供任何保护,所以 on-die ECC 会与 side-band ECC 结合使用,以增强内存子系统上的端到端 RAS。图 4 描述了 on-die ECC 的 WR 和 RD 操作流程。

个人理解:

ECC是dram内部产生的,内部检测的。所以不会对数据从DRAM出来到controler之间的通道进行数据检测保护。

图 4:片上 ECC 的 WR 和 RD 操作流程

On-die ECC是DDR5上推出的新功能,随着DDR的速度,工艺双重提升,Memory出现问题的概率大大的增加了,为了降低Memory问题,DDR颗粒本身可以对自己的数据进行校验(Data 128-bit, ECC 8-bit);即DDR5的颗粒自己具备ECC的生成,校验和存储功能,即所有的动作均在DIMM颗粒内进行。因此ECC数据不需要传输至Memory Controller端,此功能对Memory Controller透明,可以和Side-band ECC同时使用,互不干涉。具体的读写操作如下:

写:Memory Controller将Data传输至DIMM,DIMM颗粒计算出ECC在存储至颗粒里面。

读:DIMM颗粒读出Data和对应的ECC,DIMM颗粒再次计算出ECC,和读取的ECC进行校验。

Link ECC

Link-ECC 方案是一种 LPDDR5 功能,可保护 LPDDR5 链路或信道免受单位错误的影响。内存控制器计算 WR 数据的 ECC,并在特定位上发送 ECC 和数据。DRAM 基于接收到的数据生成 ECC,对照接收到的 ECC 数据进行校验,并纠正任何单位错误。控制器和 DRAM 在读取操作中的作用是相反的。请注意,link ECC 不针对内存阵列上的单位错误提供任何保护。然而,inline ECC 与 link ECC 相结合,通过提供端到端的单位错误防护,增强了 LPDDR5 信道的稳定性。图 5 描述了 link ECC 的 WR 和 RD 操作流程。

Link ECC是LPDDR5新有的功能,其定位检测LPDDR5链路是否产生了问题;做法为用Memory Controller计算出的ECC和DIMM计算出的ECC进行对比,这样可以确保数据中链路上没有发生错误;但是DIMM端数据存储中发生的问题是不能被检测的。具体读写操作如下:

写:Memory Controller计算出ECC,并用Inline的方式将数据和ECC分别传送至DIMM,DIMM通过Data再次计算出ECC,计算出的ECC被和传输到的ECC进行比较校验。

读:DIMM根据Data计算出ECC,Data和ECC分别被传送至Memory Controller;Memory Controller根据Data再次计算出ECC,计算出的ECC和被传过来的ECC进行比较校验。

link ECC原理

LPDDR5的Link ECC功能只能纠正最多2bit的fail,超过2bit的fail依旧无法纠正。????

存在疑问:ECC不应该只能对单bit错误进行纠正,对2bit数据只能做检查,对多bit数据不能保证能检测到?

其实现原理是在传输数据的过程中,同时传递Link ECC的校验码,当DRAM接收到数据和校验码时,DRAM内部会给数据做一个Link ECC的校验,去判断数据传输过程中有无bit fail。

当计算出的校验码不是0时,说明有fail,根据系列算法,可以反推出是数据fail还是Link ECC校验码错误。

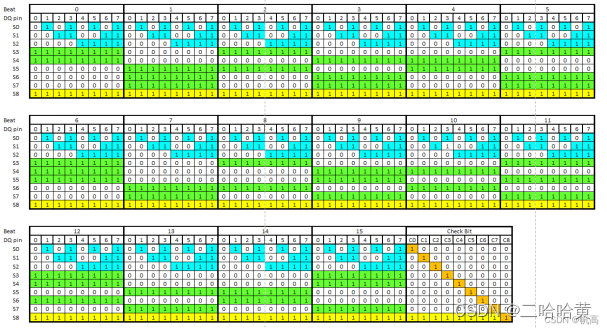

此处不能看成3个表格,应该看成1个表格。是137列,11行。

Beat代表的是每个Burst的数据。 DQ pin行中代表的是DQ0-DQ7。S0-S8是算出来的Link ECC code.

对于DQ8-15计算方式与DQ0-7一致。

对于BurstLength=32时,分为前16个Burst和后16个Burst,分开进行Link ECC code计算。

计算公式是将每个1的位置的数据进行异或,从而得到S0-S8.

在输入数据时,将Link ECC code 和Data同时传输进入LPDDR5.

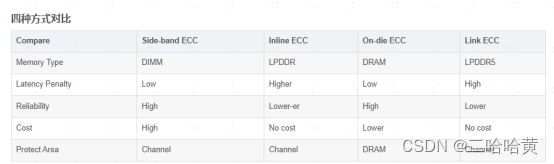

四种对比

768

768

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?