系列文章目录

芯动力——硬件加速设计方法学习笔记(第二章)高质量VerilogHDL描述方法(1)(常见语法对应硬件结构)

芯动力——硬件加速设计方法学习笔记(第二章)高质量VerilogHDL描述方法(2)(考虑面积、功耗、时延等)

芯动力——硬件加速设计方法学习笔记(第二章)高质量VerilogHDL描述方法(3)(RTL设计指导原则)

芯动力——硬件加速设计方法学习笔记(第三章)单bit信号和多bit数据流的跨时钟域传输

前言

学习打卡第五天,今天下午继续学习,加油!

今日天气:晴

一、复位电路

定义:数字电路中重要组成部分,能够使电路进入初始状态或其他预知状态

寄存器、存储器、其他逻辑单元都需要复位电路

时序电路:双稳态电路,需要复位电路

组合逻辑电路:没有存储功能,不需要复位电路

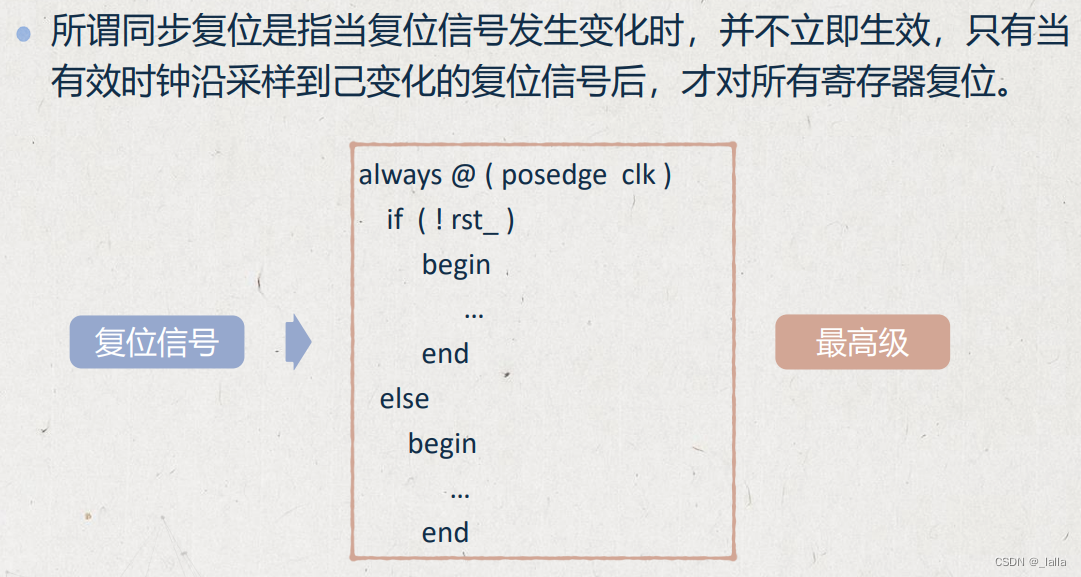

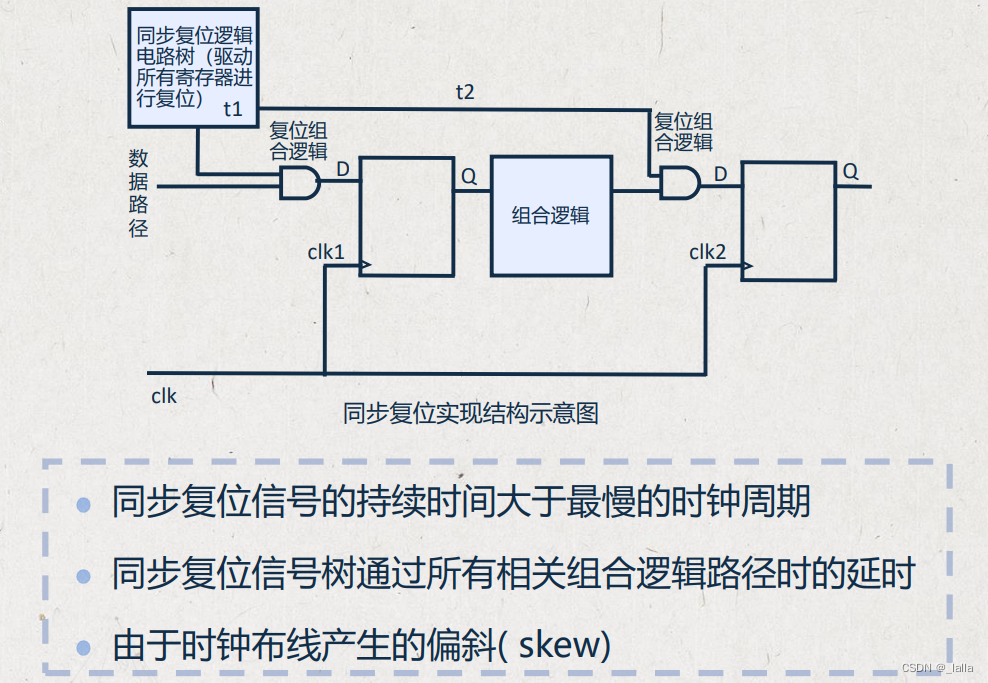

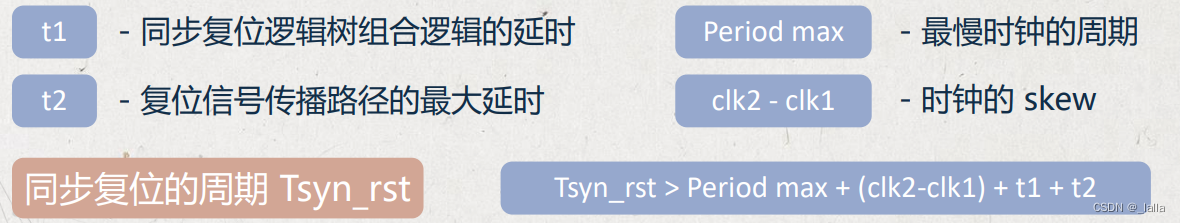

1、同步复位

优点:有利于时序分析和仿真、过滤掉毛刺

缺点:大多数逻辑器件的目标库内的DFF只有异步复位端口,需要消耗掉组合逻辑资源来实现同步复位;复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。

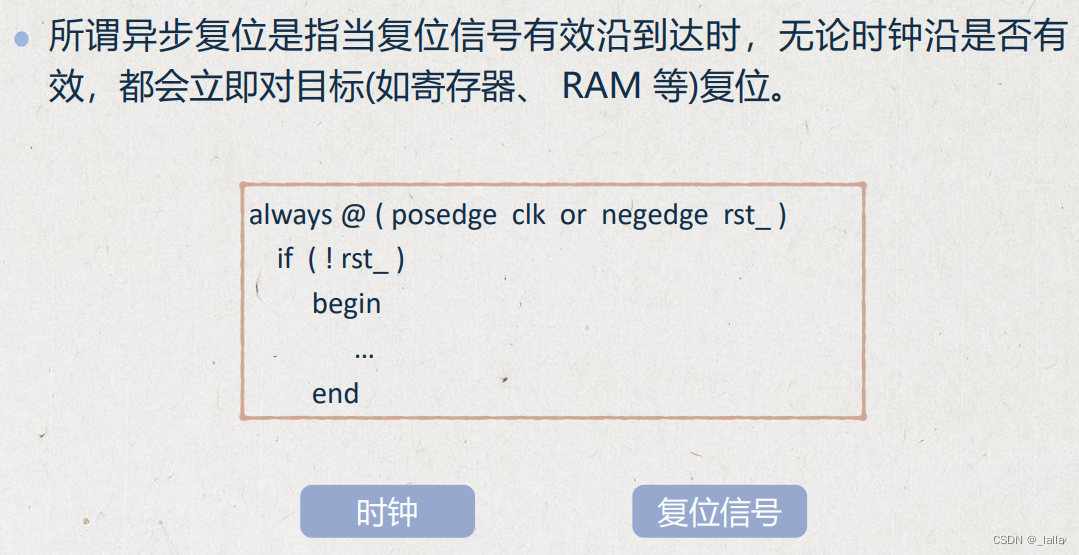

2、异步复位

优点:设计简单;节约资源、库中触发器自带异步复位端;异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

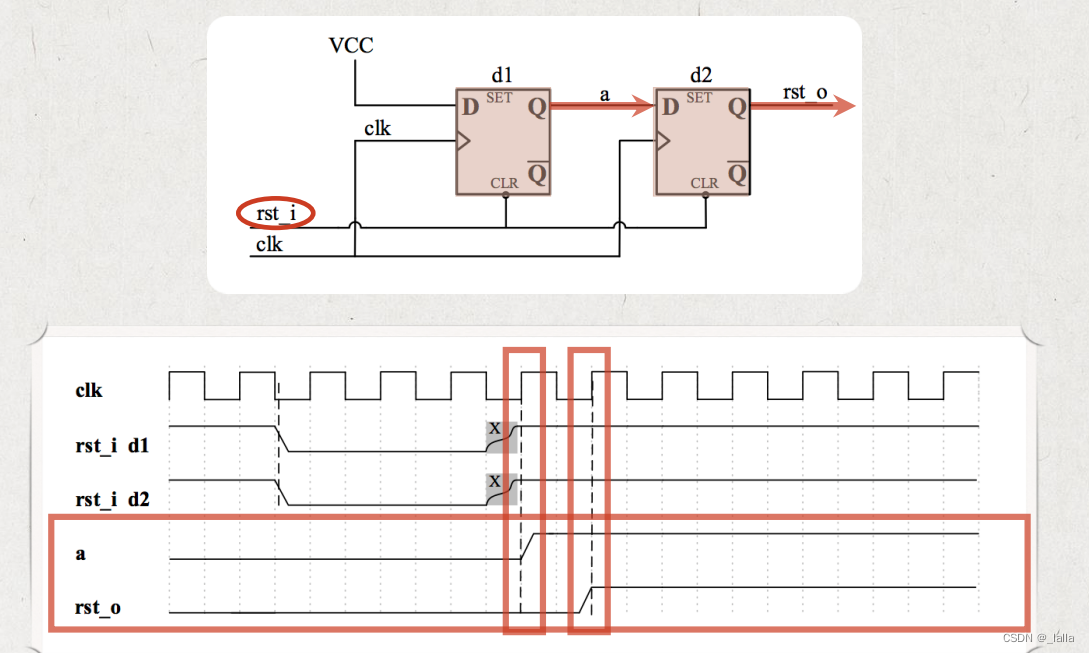

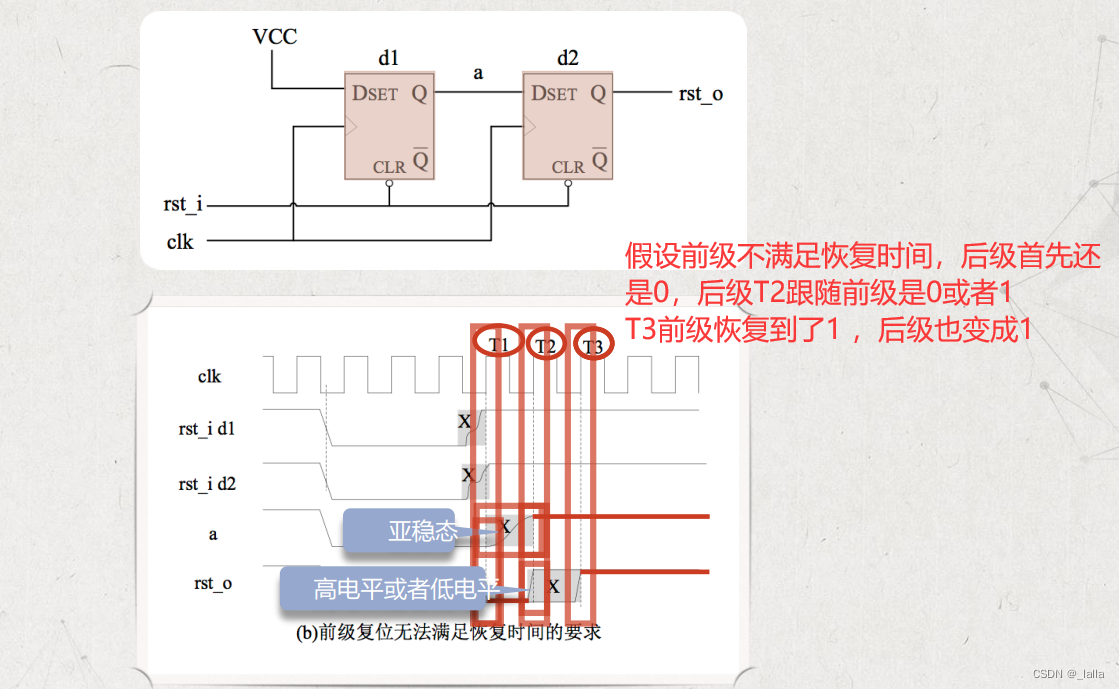

缺点:易受毛刺影响、亚稳态(倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态)

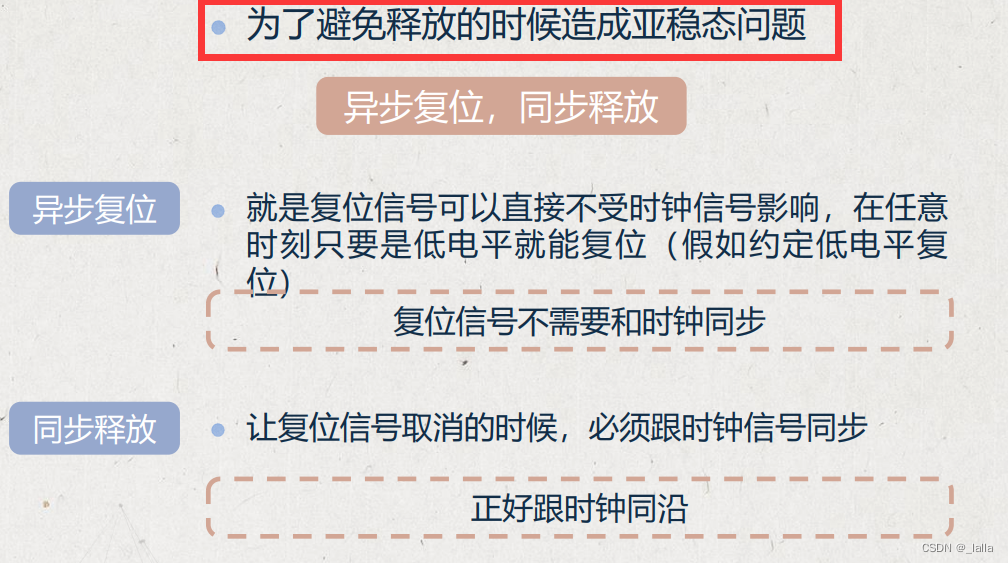

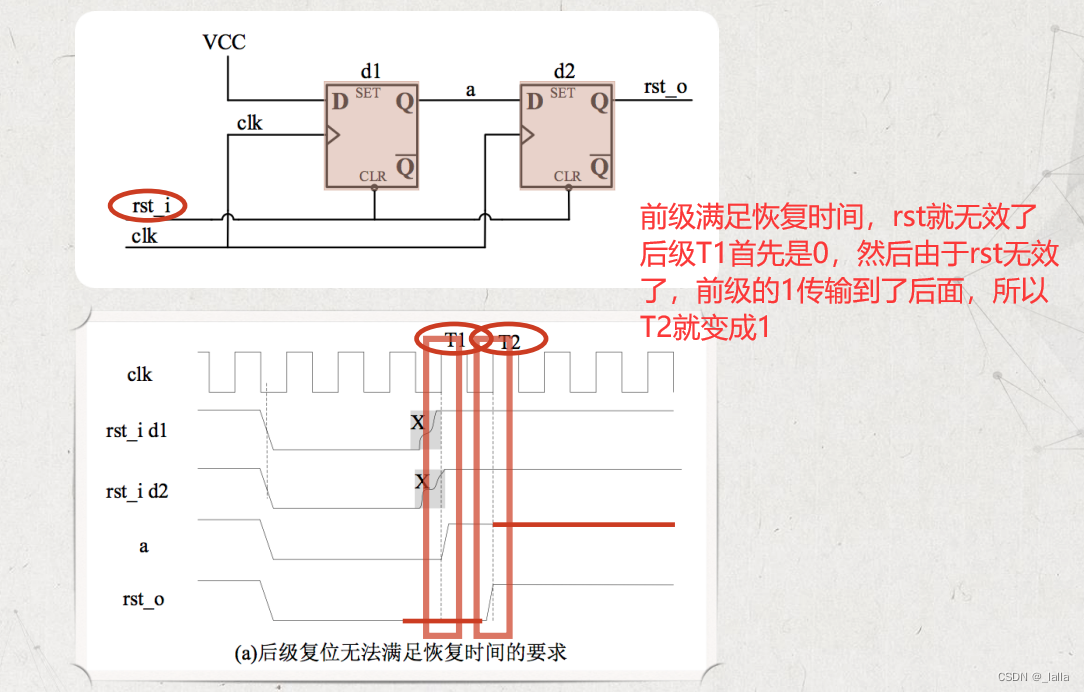

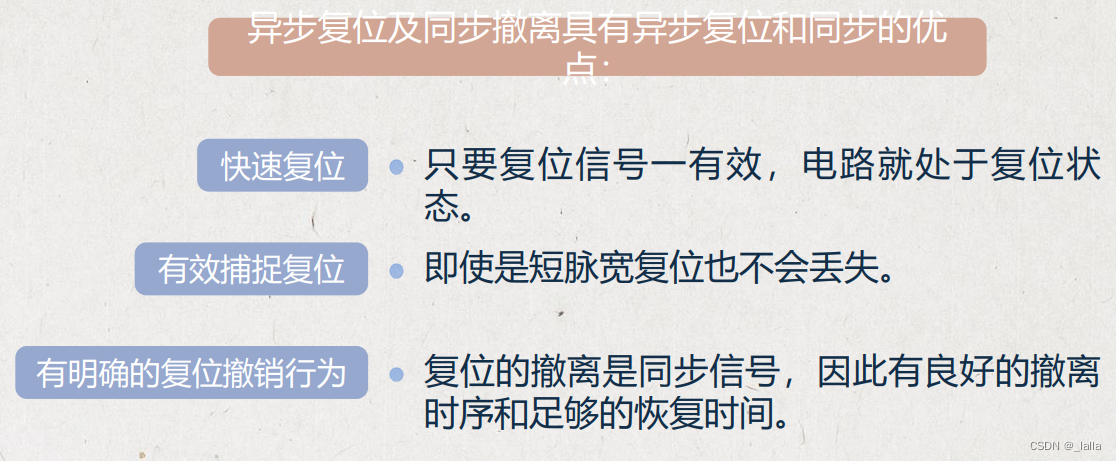

3、异步复位 同步释放

(1)优点:快速复位,有效捕捉复位信号,有明确的复位撤销时间

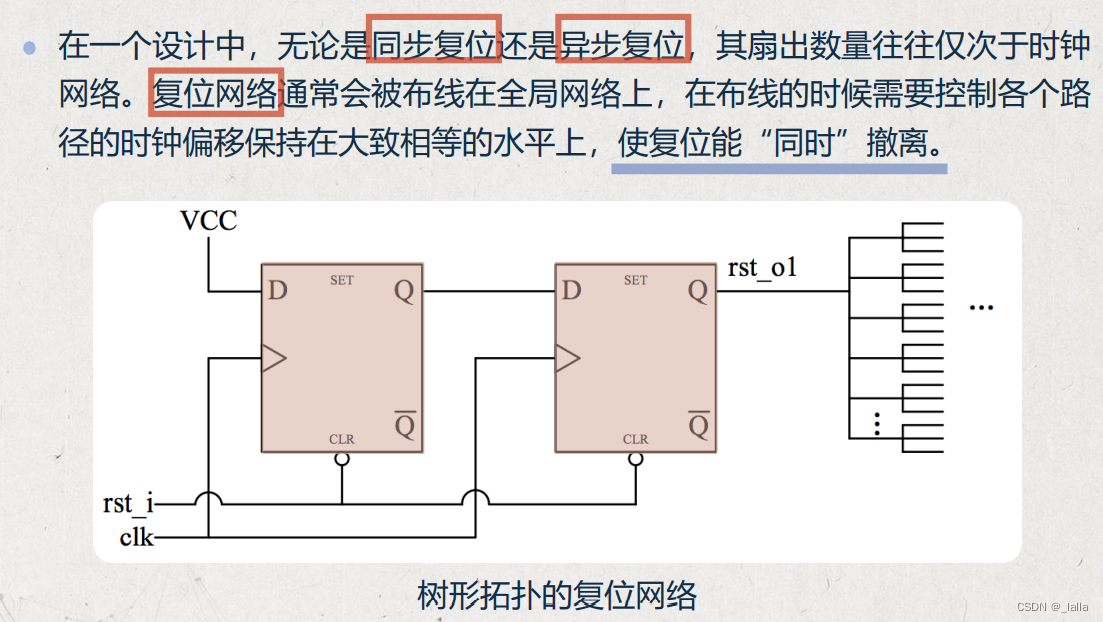

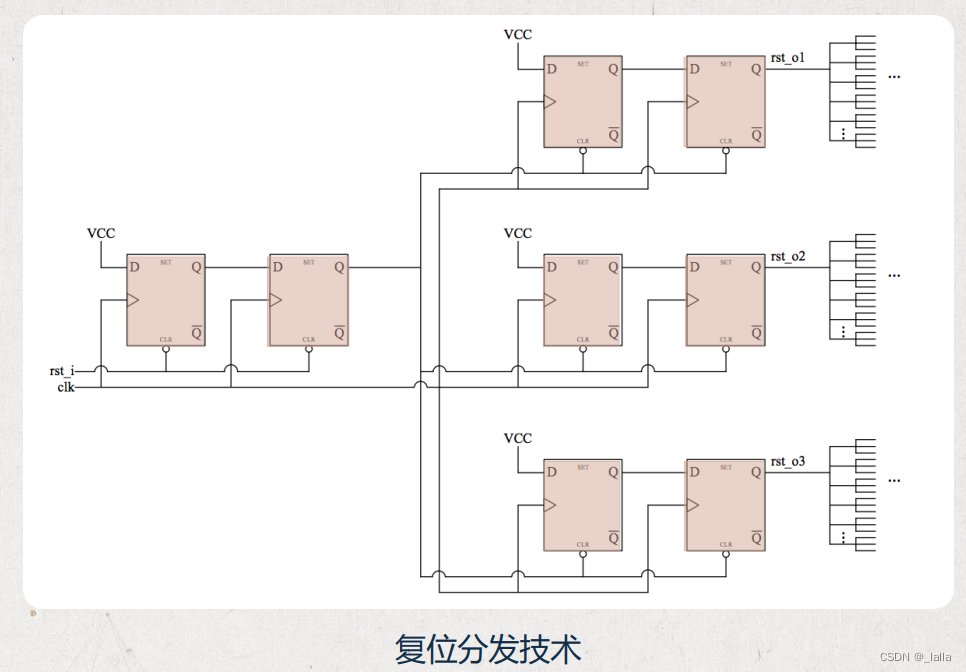

(2)复位网络:复位分发技术

复位信号相互独立,同时减小了扇出数

我理解的是不是把1进行了打两拍处理,而不是复位信号

484

484

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?