文章目录

前言

从今天开始写学习mooc上面的《芯动力——硬件加速设计方法》,怕自己学之后就忘了,特此记录下来,希望自己能坚持学习下来!(本文单纯只是记录自己学习笔记,同时对相关内容进行补充,还是推荐大家去mooc上看邸老师的视频!

一、产业链

1、Foundry:晶圆厂商,专门从事半导体晶圆制造生产,接受其他无晶圆厂设计公司委托,制造芯片,是整个微电子行业的基础。

代表公司:台积电(TSMC,目前成熟工艺可以做到5nm和7nm)、中芯国际(SMIC、EUV光刻机)、华虹半导体

2、Fabless:单词Fabrication和less的组合,指代没有芯片制造工厂的IC设计公司,简称为无晶圆厂,只要专注于设计而没有制造。

代表公司:博通、高通(国外)

国内:

3、EDA(Electronic Design Automation):自动化软件生产厂商,为集成电路设计提供软件支持

三大巨头:Synopsys、Cadence、Mentor

国内:华大九天

4、Design Service:主要提供芯片后端设计服务。一些设计公司在项目机制或者缺少后端设计能力时,选择设计服务公司。

代表公司:芯原、世芯

5、IP供应商:由于IP研发成本高,可复用性强,一些设计公司为其他公司提供IP设计服务。

代表公司:ARM(RISC IP)

6、IDM(Integrated Device Manufactory 集成电路制造商):集芯片设计、芯片制造、芯片封装和测试等多个产业链环节于一身

代表公司:Intel、三星、TI

二、岗位

三、数字芯片设计流程

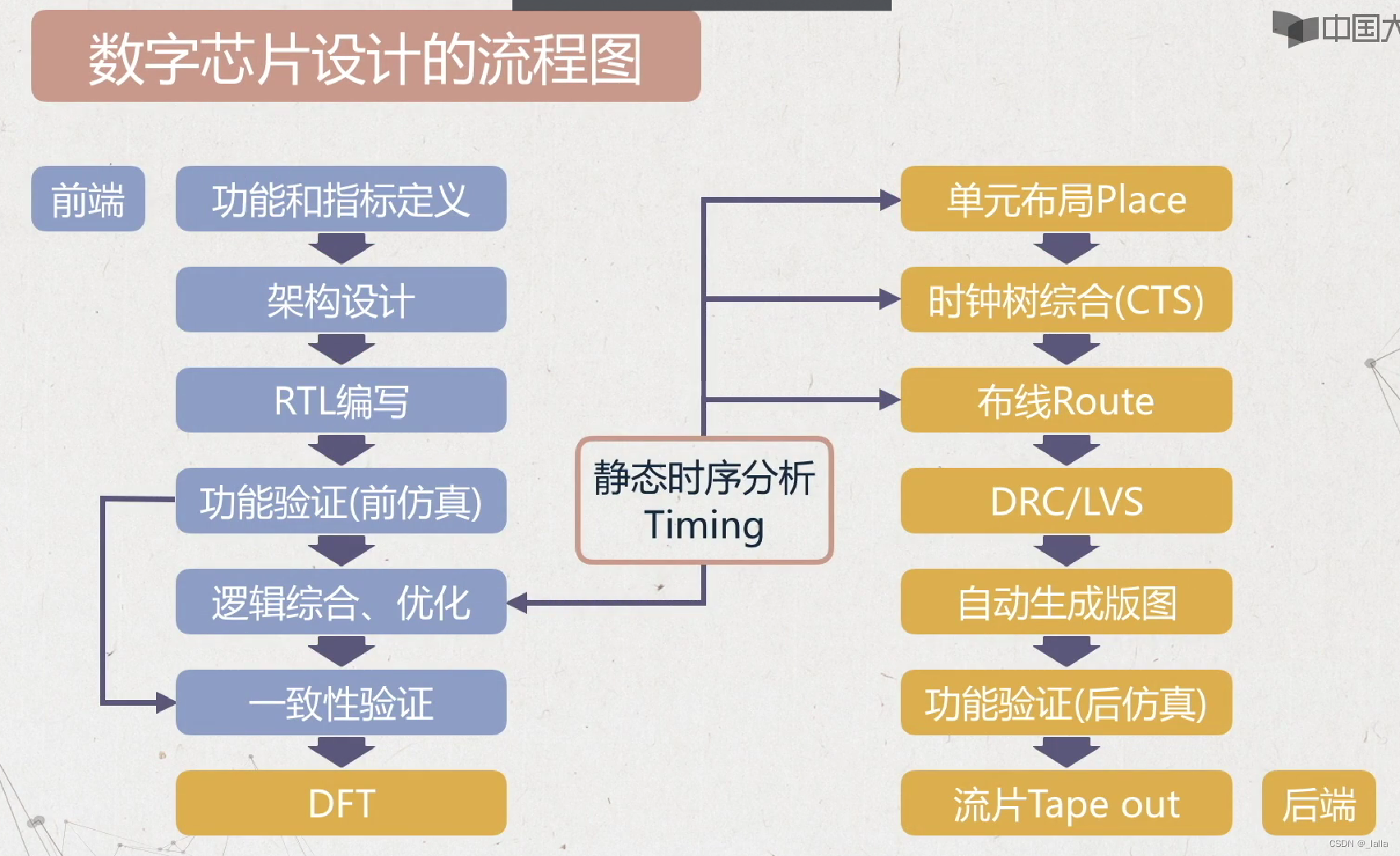

1、数字前端设计/逻辑设计

这篇文章总结得很好

链接

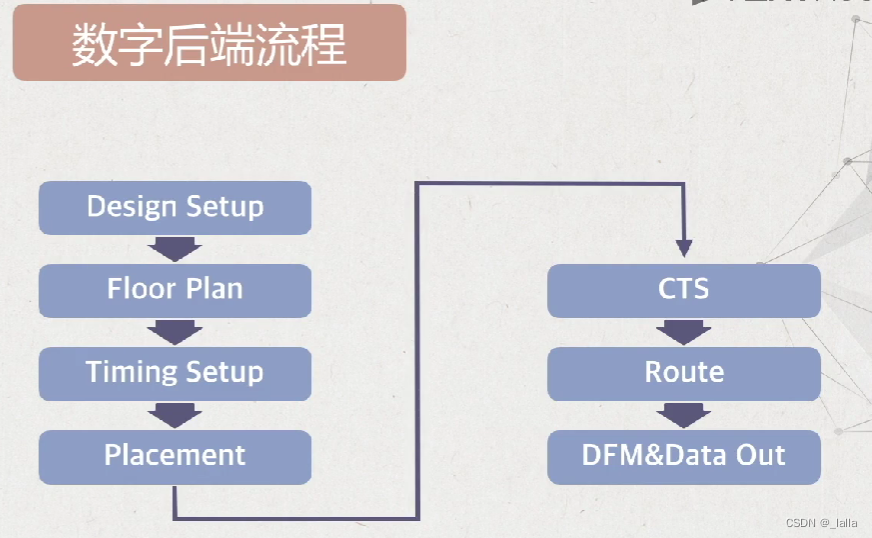

2、数字后端设计/物理设计

将网表格式文本转化为一个个有物理大小和位置的单元、连线,在完成过程中满足面积、性能、功耗的要求。

工具来源:Synopsys、Cadence

Design Setup:判断输入文件是否缺失或错误

Floor Plan:确定design的形状大小、出pin的位置、macro的摆放

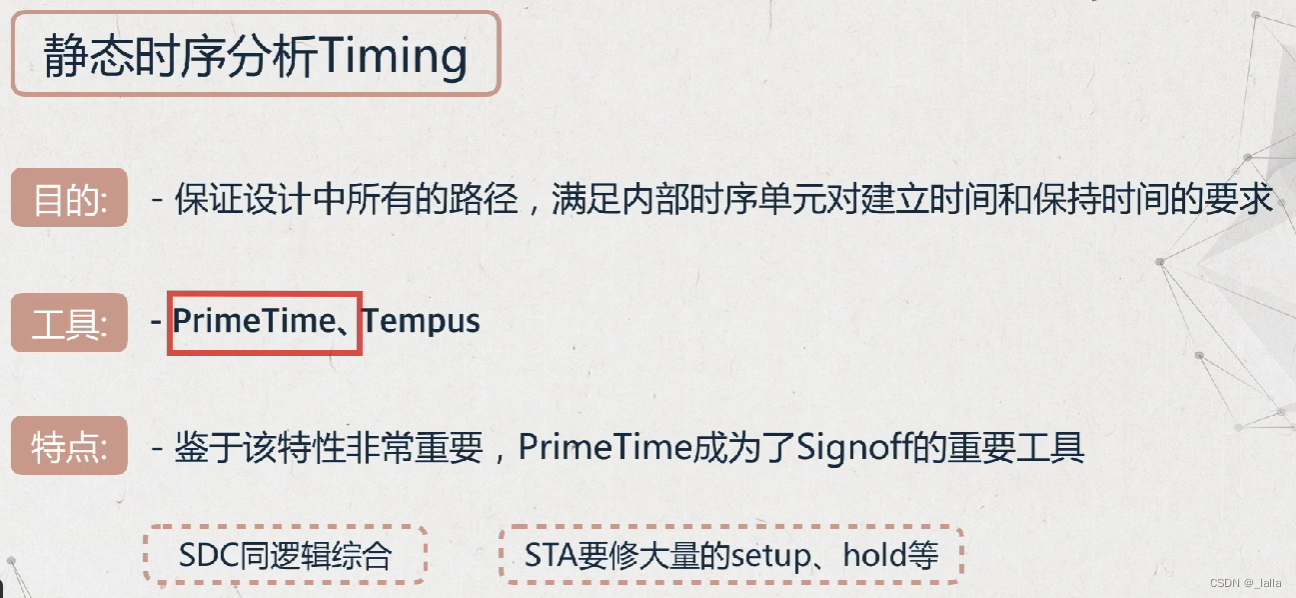

Timing Setup:静态时序分析

Placement:将标准单元(std cell)放到core area中,并且满足congestion和timing的要求

CTS:clock tree synthesis 时钟树综合,时钟网络及其上的缓冲器构成了时钟树

(由于要驱动电路中所有时序单元,带载较多,负载延时较大,需要插入缓冲器减小负载和平衡延时)

Routing:将信号线通过金属连接起来,考虑DRC、LVS(Layout vs Schematic网表一致性检查)

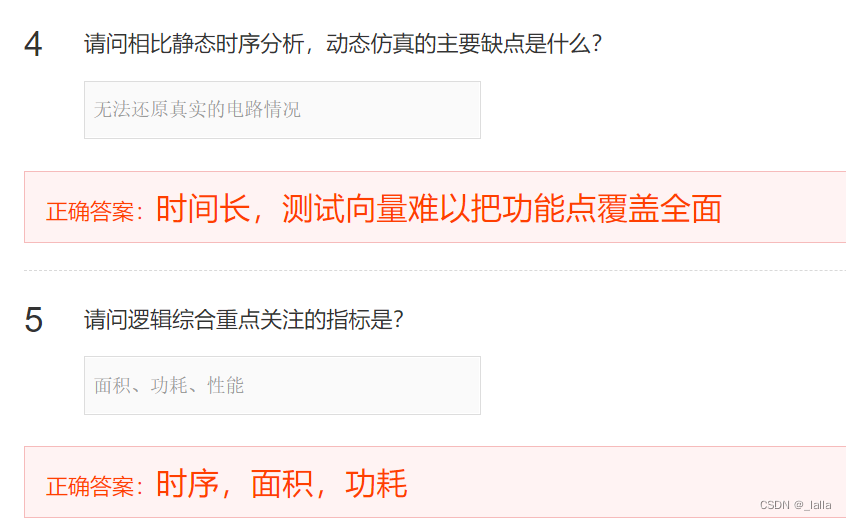

四、简答题

1、芯片设计的产业链主要包括哪几个环节,各个环节的典型代表企业有哪些?

晶圆厂 Foundry,无晶圆设计公司 Fabless,EDA软件公司,设计服务公司,IP 供应商,集成设计与制造 IDM

2、请写出数字芯片、模拟芯片的设计流程

(1)电气设计,物理设计,制造,封装和测试

(2)根据设计需求,制定电路设计指标->根据电路设计指标选用相应的架构->使用交互式电路图进行设计->进行电路仿真->模拟版图设计->版图验证(DRC、LVS、NE、ERC、PEX)->后仿真->生成GDSⅡ文件,交给芯片制造商流片;

3、请总结数字芯片与模拟芯片设计有何异同

先分别回答两者的设计流程

相同点:都是去设计一个芯片

区别:

(1)数字芯片处理数字信号,模拟芯片处理模拟信号,比如运算放大器、线性稳压器、基准电压源等

(2)在基础单元上有些区别的,基本上数字芯片是CMOS结构,模拟芯片是N个(一个或多个)PN结构组成

(3)数字芯片基本都是由N多个相同的单元电路由一个控制电路或多个控制电路等单元构成。基本上一样的单元的重复。而模拟芯片电路是各个不同的单元构成,(二者相比而言)重复的单元电路很少

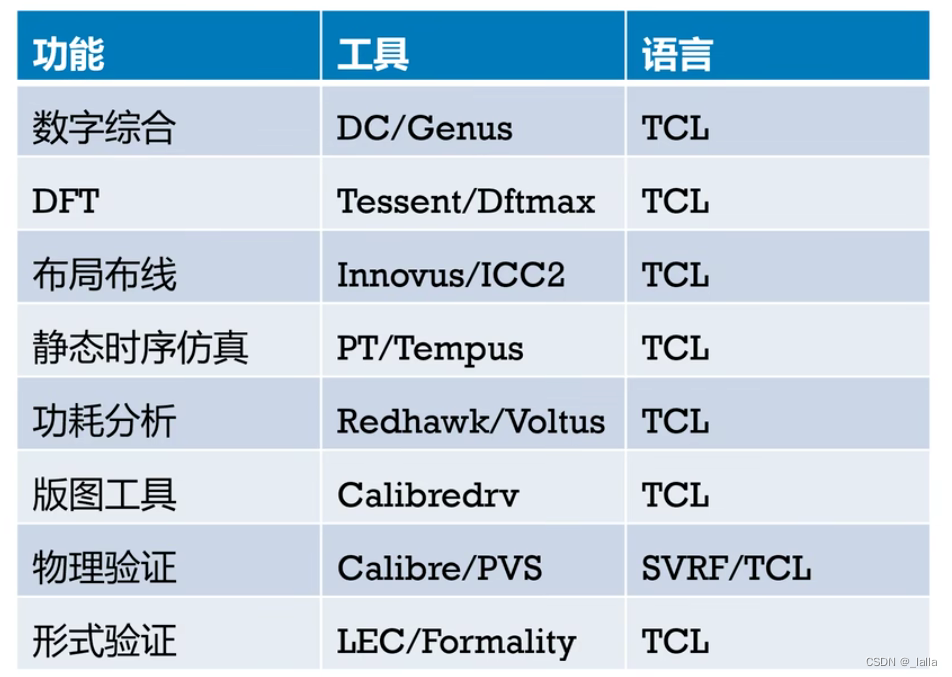

4、Synopsys、Cadence两家的仿真验证工具、逻辑综合工具、形式验证工具、布局布线工具分别是什么?

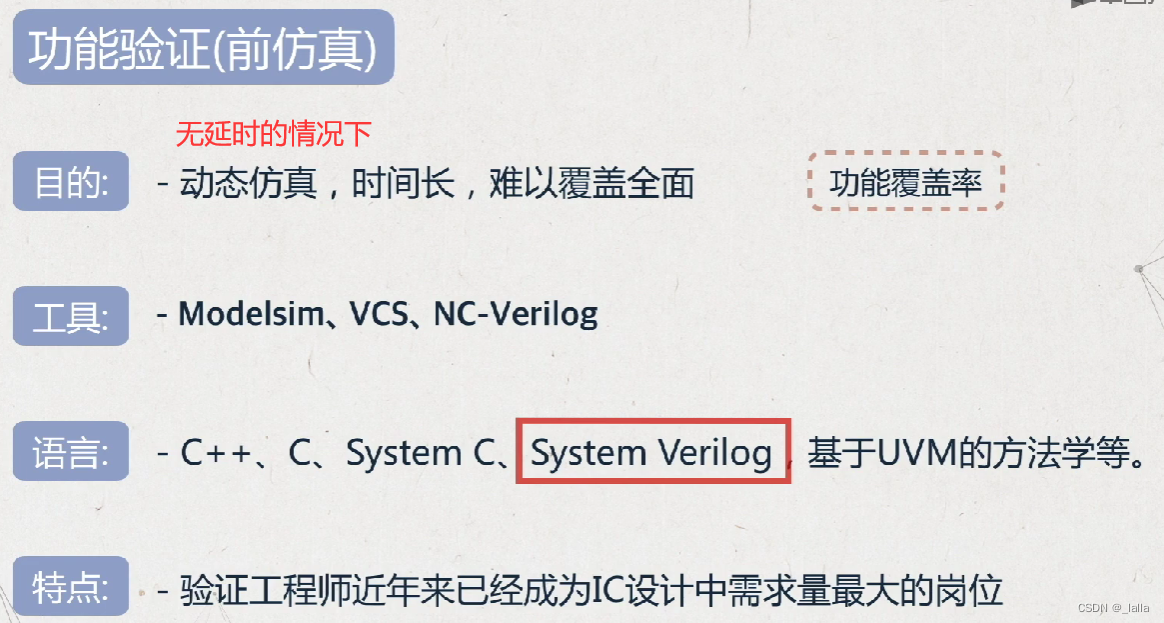

(1)仿真验证

Synopsys:VCS

Cadence:NC-Verilog

Mentor:Modelsim、Questasim

(2)逻辑综合

Synopsys:DesignCompiler

Cadence:buildgates、Envisia Ambit

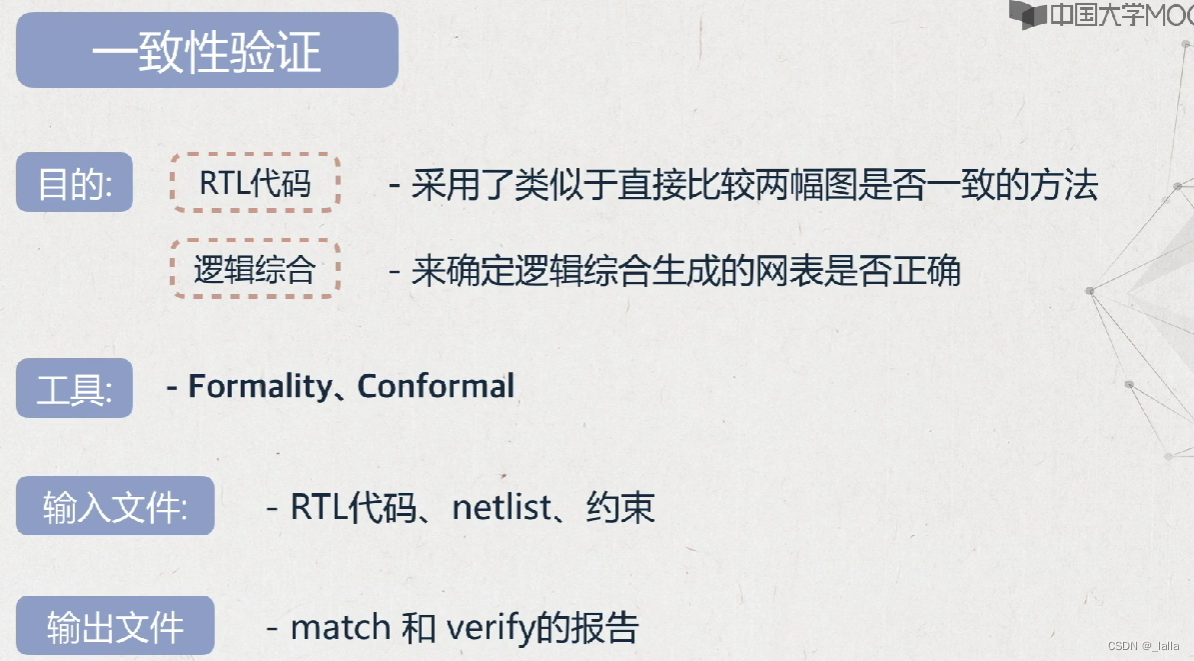

(3)形式验证

Synopsys:Formality

Cadence:LEC、FormalCheck

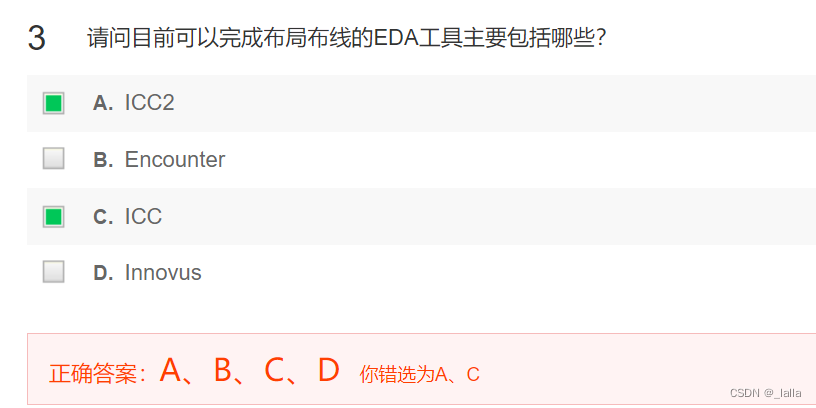

(4)布局布线

Synopsys:Astro、Physical Compiler、IC Compiler

Cadence:Encounter、PKS、Silicon Ensemble、Design Planner

(5)STA

Synopsys:Prime Time

Cadence:Pearl、Tempus

5、前仿和后仿的区别

逻辑综合之前的该部分仿真称为前仿真,也即功能仿真/行为仿真/逻辑仿真。接下来在版图设计完成之后还要再进行一次仿真,称为后仿真,也即时序仿真 。

五、课后习题

1404

1404

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?