题目

请编写一个模块,实现简易秒表的功能:具有两个输出,当输出端口second从1-60循环计数,每当second计数到60,输出端口minute加一,一直到minute=60,暂停计数。

模块的接口信号图如下:

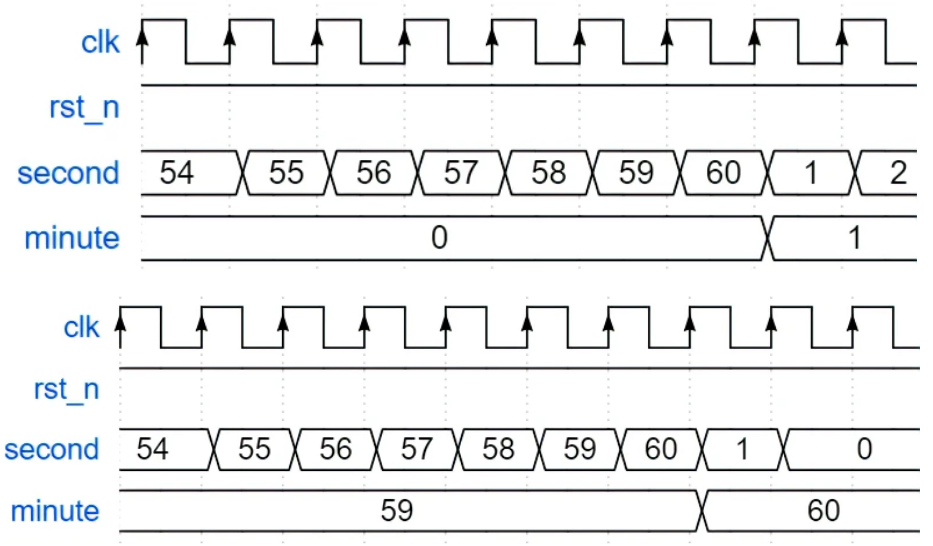

模块的时序图如下:

输入输出描述如下。

| 信号 | 类型 | 输入/输出 | 位宽 | 描述 |

|---|---|---|---|---|

| clk | wire | Intput | 1 | 系统时钟信号 |

| rst_n | wire | Intput | 1 | 异步复位信号,低电平有效 |

| second | reg | Output | 6 | 秒表的秒读数 |

| minute | reg | Output | 6 | 秒表的分读数 |

答案

在这里需要注意的是:second在复位时是0,也就是说第一个minute的计数是从0计数到60,而后面second计数到60后,再进行计数时,是从1计数到60。

`timescale 1ns/1ns

module count_module(

input clk,

input rst_n,

output reg [5:0]second,

output reg [5:0]minute

);

//second

always @(posedge clk or negedge rst_n)

if(!rst_n)

second <= 6'd0;

else if(minute != 6'd60)

if(second == 6'd60)

second <= 6'd1;

else

second <= second + 1'd1;

else

second <= 6'd0;

//minute

always @(posedge clk or negedge rst_n)

if(!rst_n)

minute <= 6'd0;

else if(second == 6'd60)

minute <= minute + 1'd1;

else

minute <= minute;

endmodule

304

304

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?