DDS

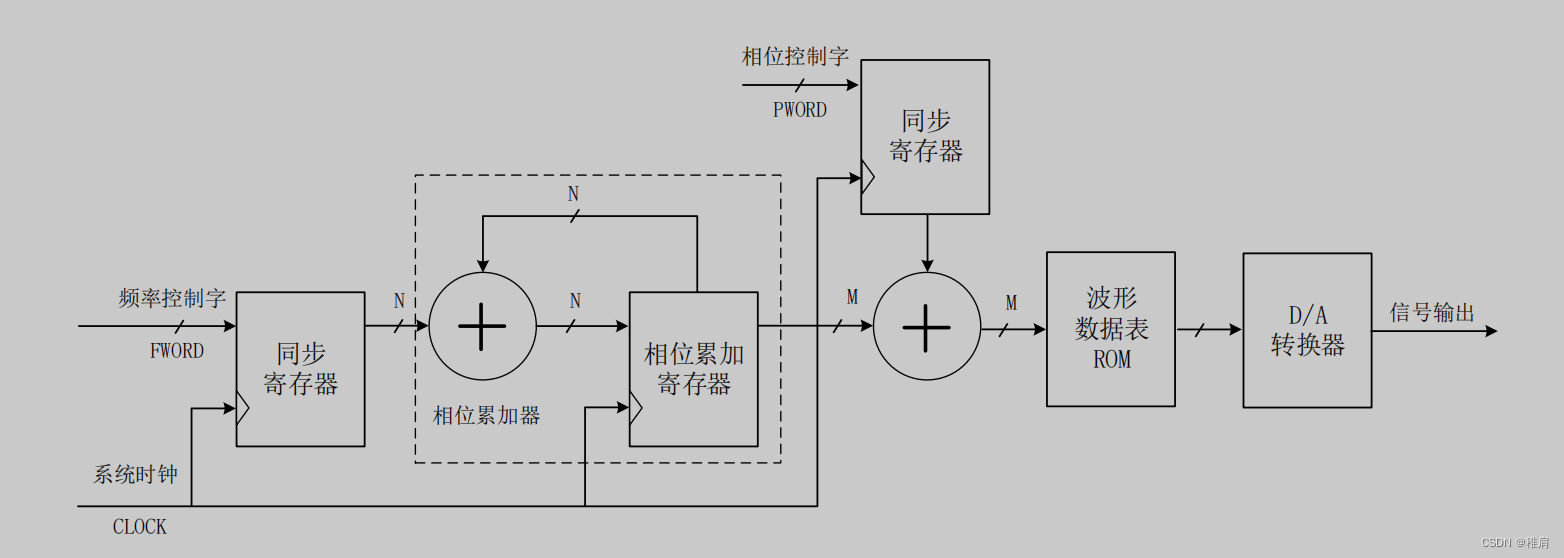

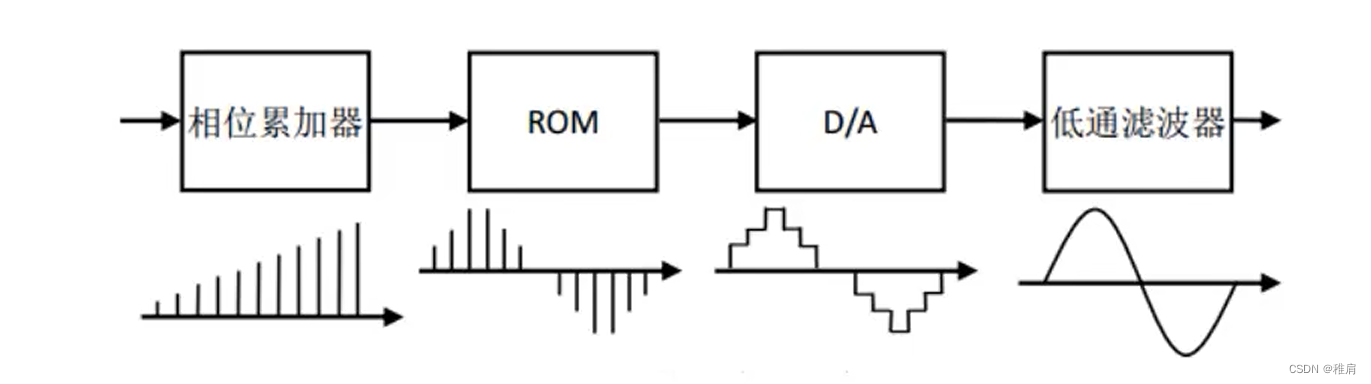

DDS主要由相位累加器,ROM,DA转换模块,同步寄存器等模块组成。主要有相位控制字和频率控制字作为输入。时钟上升沿到来,加法器就将输入频率控制字与累加寄存器输出的相位数据相加,所得的结果又给到累加寄存器的输入端,每个时钟沿到来,将频率控制字进行线性相位的累加。

相位累加器输出的数据是波形存储器ROM的相位的采样地址,与相位控制字结合,这样可以实现相位到幅度的转变,它的溢出频率就是DDS输出的信号频率。波形数据表ROM再经过DA模块将数字信号转为模拟信号输出。

若相位累加器的位数是N,则分辨率是1/2的N次方。若DDS的时钟频率是F,频率控制字是fword,则输出频率为Out=fword*F/2的N次方。

锁相环

锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于通信和控制系统中的反馈控制电路。可以为硬件电路中的不同模块提供稳定的工作频率保证时钟域的同步。

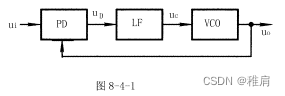

锁相环主要由以下三个基本部件组成:

- 鉴相器(Phase Detector,PD):它的作用是比较输入信号和反馈信号的相位差,并将这个相位差转换为对应的电压信号输出。

- 环路滤波器(Loop Filter,LF):通常是一个低通滤波器,用于平滑鉴相器输出的电压信号,消除高频噪声,并生成一个干净的控制电压。

- 压控振荡器(Voltage-Controlled Oscillator,VCO):根据环路滤波器输出的控制电压调整其输出频率,目的是使输出信号的频率与输入信号的频率相匹配或保持固定比例关系。

锁相环的工作原理是:当输入信号的频率发生变化时,鉴相器检测到相位差的变化,并通过环路滤波器调节压控振荡器的控制电压,从而改变压控振荡器的输出频率,以减小输入与输出之间的频率和相位差。最终,在锁相环锁定状态下,输出信号的频率会跟踪输入信号的频率变化,两者的相位差保持稳定。

此外,锁相环还具有许多应用,比如在无线通信系统中用于解调和调制、在电力系统中用于同步发电机、在计算机时钟生成等场合。由于锁相环能够提供稳定的相位关系,因此它在需要精确频率合成或信号跟踪的应用中非常有用。

663

663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?