参考资料:

芯片设计专题(二)——CRG(Clock中的ICG) - 知乎

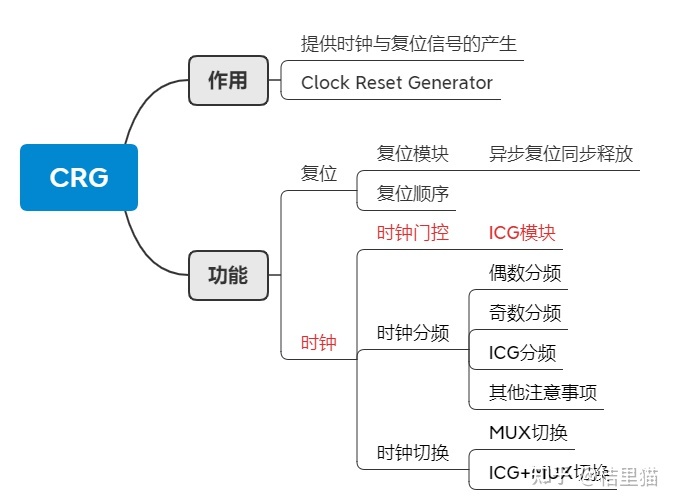

CRG模块:时钟复位产生模块。控制着一个设计的所有时钟。(嘿嘿,注意这边不是要将时钟复位),仅仅是引申下CRG的模块接口利用关联数组,在使用时提高复用性。

首先了解到这个模块会存在许多时钟信号,环境会通过设置时钟周期来设置时钟频率。

首先定义:

real clk_period[15];

int clk_name[string] = {default:-1};

//配置

clk_name["string"] = clk_type::APB;

这个clk_type::APB可以用package clk_type,内部定义parameter APB = 1;

也可以用枚举类型给他赋值。

所以在调用时可以clk_period[clk_name["apb"]] = N;

突然觉得可以直接

real clk_perio[string] = {default:-1};(尤其是一个soc里面的复位设计,全局复位,上电复位,事件复位,软复位,硬复位……牵涉到功耗管理和芯片安全模块等等,关于这些你知道有什么可参考的书籍或者资料吗?谢谢!)

3111

3111

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?