Verilog有限状态机(8)

前言

今天继续更新状态机小节的习题。

题库

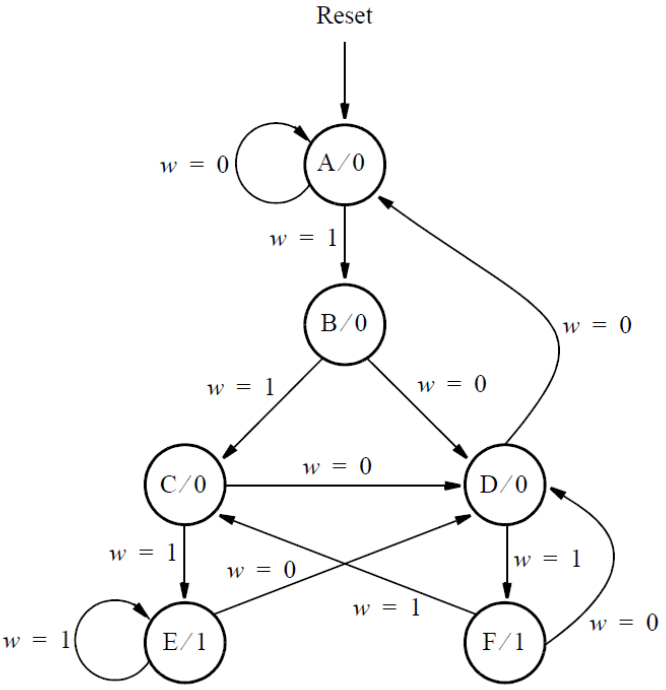

Q2a:FSM

正宗的FSM题,没啥说的,看图写代码。

Solution:

module top_module (

input clk,

input reset, // Synchronous active-high reset

input w,

output z

);

parameter A = 3'd0, B = 3'd1, C = 3'd2;

parameter D = 3'd3, E = 3'd4, F = 3'd5;

reg [2:0] current_state, next_state;

always @(*) begin

case(current_state)

A: next_state = w ? B : A;

B: next_state = w ? C : D;

C: next_state = w ? E : D;

D: next_state = w ? F : A;

E: next_state = w ? E : D;

F: next_state = w ? C : D;

default:next_state = A;

endcase

end

always @(posedge clk) begin

if(reset) begin

current_state <= A;

end

else begin

current_state <= next_state;

end

end

assign z = (current_state == E) | (current_state == F);

endmodule

Q2b:One-hot FSM equations

状态使用独热编码,将状态中的y[1]和y[3]表示出来。

Solution:

module top_module (

input [5:0] y,

input w,

output Y1,

output Y3

);

assign Y1 = y[0] & w;

assign Y3 = (y[1] | y[2] | y[4] | y[5]) & ~w;

endmodule

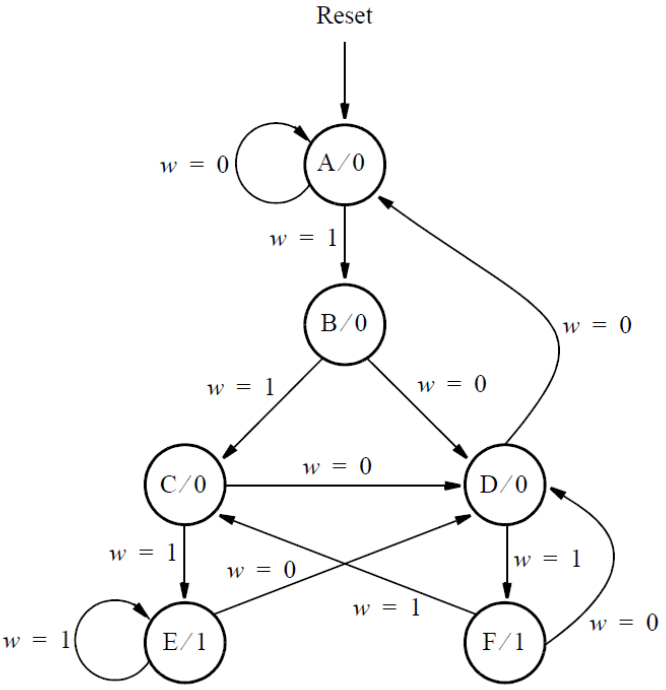

Q2a:FSM

本题是用状态机实现一个判优器。其中r1、r2、r3分别表示三种设备的request,g1、g2、g3表示资源的分配情况。由下面的状态图可见,设备1,2,3的优先级依次递减。当设备请求到资源时,需等其完成任务才能释放资源。

Solution:

module top_module (

input clk,

input resetn, // active-low synchronous reset

input [3:1] r, // request

output [3:1] g // grant

);

parameter A = 2'd0, B = 2'd1;

parameter C = 2'd2, D = 2'd3;

reg [1:0] current_state, next_state;

always @(*) begin

case(current_state)

A:begin

if(r[1] == 1'b1) begin

next_state = B;

end

else if(r[2] == 1'b1) begin

next_state = C;

end

else if(r[3] == 1'b1) begin

next_state = D;

end

else begin

next_state = A;

end

end

B: next_state = r[1] ? B : A;

C: next_state = r[2] ? C : A;

D: next_state = r[3] ? D : A;

default: next_state = A;

endcase

end

always @(posedge clk) begin

if(~resetn) begin

current_state <= A;

end

else begin

current_state <= next_state;

end

end

assign g[1] = current_state == B;

assign g[2] = current_state == C;

assign g[3] = current_state == D;

endmodule

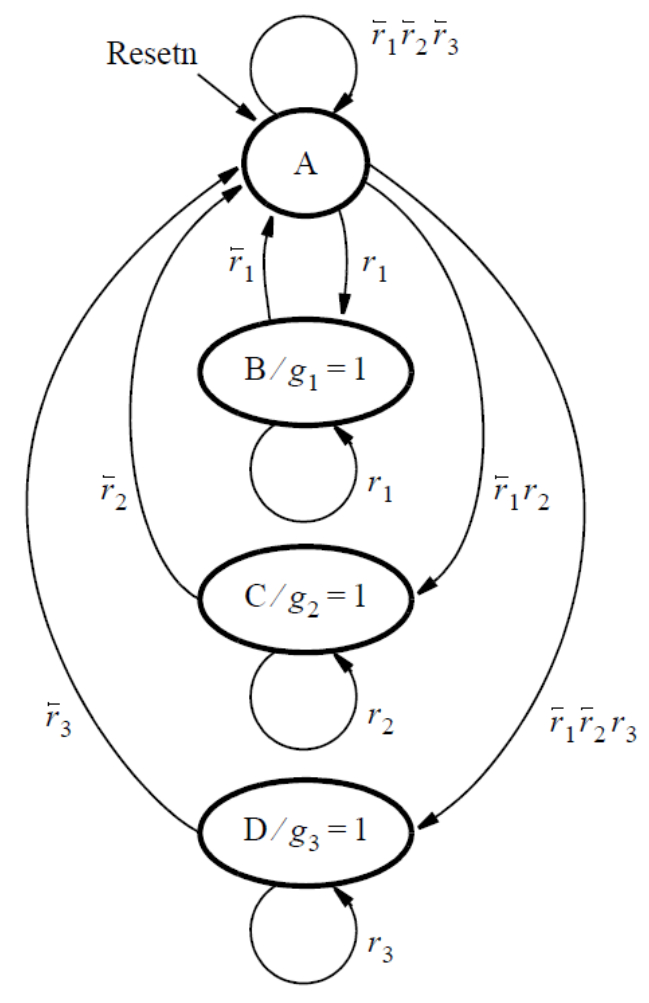

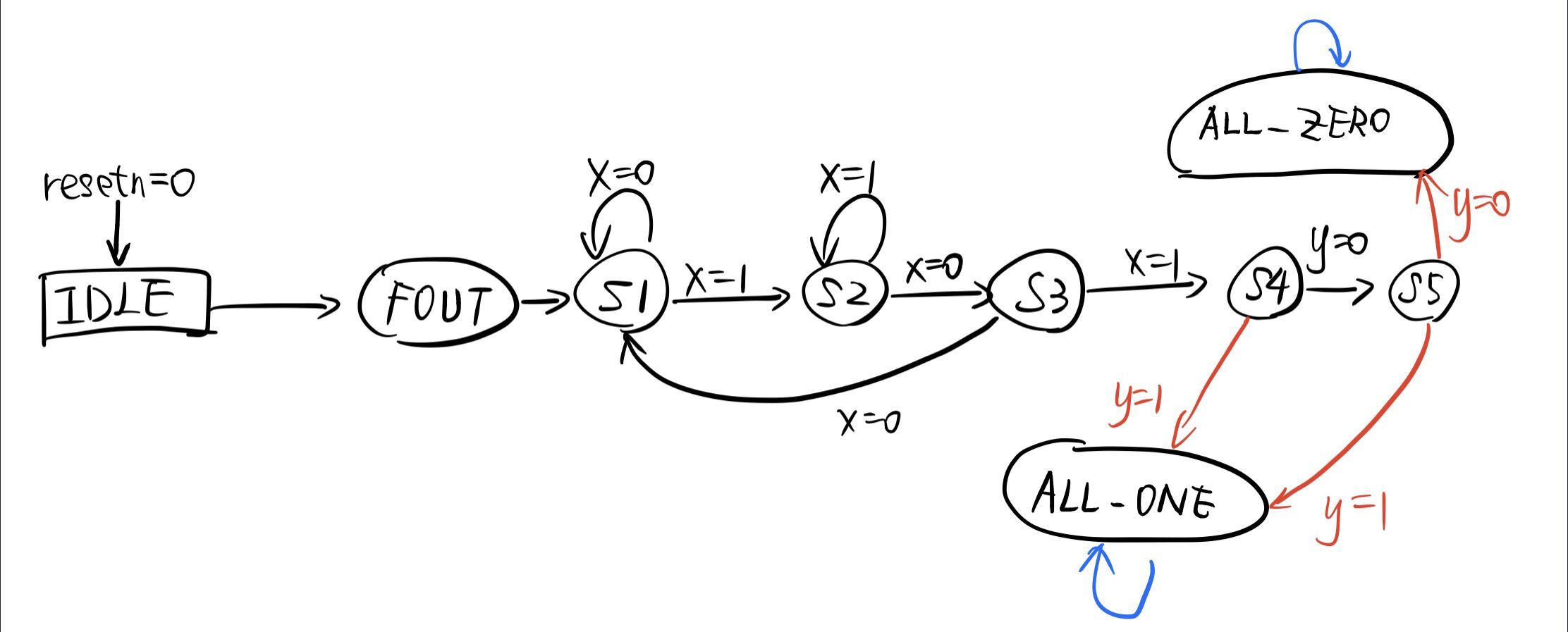

Q2b:Another FSM

该题的状态机共2输入2输出;当复位信号撤销时,在下一个周期内将f输出为1,需留意f为1持续一个周期;然后状态机取决于x的值,当x在连续的三个周期中产生值为1、0、1时,下一周期将g输出为1,在保持g为1时判断y的输入,如果y在两个周期中有任意一个周期为1了,那么g永久保持1;如果两个周期都没有1,那么g将永久保持0。

Solution:

module top_module (

input clk,

input resetn, // active-low synchronous reset

input x,

input y,

output f,

output g

);

parameter IDLE = 4'd0, FOUT = 4'd1, S1 = 4'd2;

parameter S2 = 4'd3, S3 = 4'd4, S4 = 4'd5;

parameter S5 = 4'd6, ALL_ONE = 4'd7, ALL_ZERO = 4'd8;

reg [3:0] current_state, next_state;

always @(*) begin

case(current_state)

IDLE: next_state = FOUT;

FOUT: next_state = S1;

S1: next_state = x ? S2 : S1;

S2: next_state = x ? S2 : S3;

S3: next_state = x ? S4 : S1;

S4: next_state = y ? ALL_ONE : S5;

S5: next_state = y ? ALL_ONE : ALL_ZERO;

ALL_ONE: next_state = ALL_ONE;

ALL_ZERO: next_state = ALL_ZERO;

default: next_state = IDLE;

endcase

end

always @(posedge clk) begin

if(~resetn) begin

current_state <= IDLE;

end

else begin

current_state <= next_state;

end

end

assign f = current_state == FOUT;

assign g = current_state == S4 | current_state == S5 | current_state == ALL_ONE;

endmodule

心得:状态机设计的好坏决定代码的难易程度,在画状态转移图时可以多留点时间。

结语

状态机这部分题目终于更新完了,自己在做这些题目的过程中收获也非常大,很感谢该网站的作者。如果代码哪里有误,请大家指正,评论区也欢迎大家交流不同的解题思路。

8453

8453

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?