JTAG接口电路上下拉

1 JTAG 标准中的描述

最新JTAG标准:IEEE_std_1149.1-2001

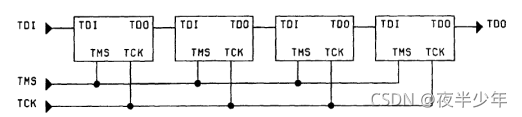

图1 JTAG原理

1.1 TMS

TMS是启动使能信号(标准PAGE-11),上拉:

1.2 TCK

TCK是时钟信号(标准PAGE-9)上升沿或下降沿有效,可以上拉也可下拉,根据具体的器件要求选择:

1.3 TDI

TDI是数据输入(标准PAGE-11),上拉:

1.4 TDO

TDO是数据输出(标准PAGE-12),三态输出,可以和TDI做级联,上拉或浮空:

1.5 TRST

TRST 是复位信号(标准PAGE-13),低电平为复位状态,上拉:

2 器件的JTAG特性

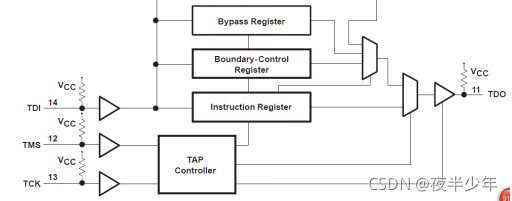

2.1 JTAG标准中的示例

标准PAGE-189 的示例:74BCT8374

74BCT8374的JTAG口上下拉特性,全部都是上拉:

2.2 CM408

手册PAGE-52 53,TDO浮空,TCK下拉,其余上拉:

2.3 ADSP-BF607

手册PAGE-39,TCK和TSRT下拉,TDO浮空,TDI和TMS上拉:

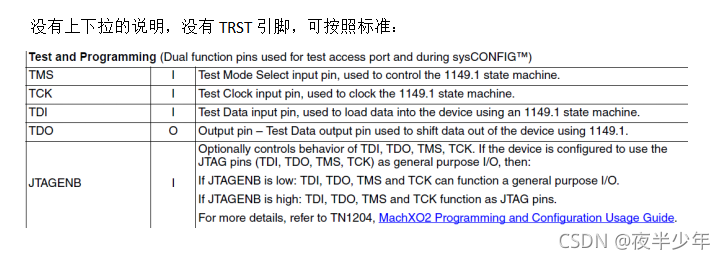

2.4 CPLD LCMXO2-4000

没有上下拉的说明,没有TRST引脚,可按照标准:

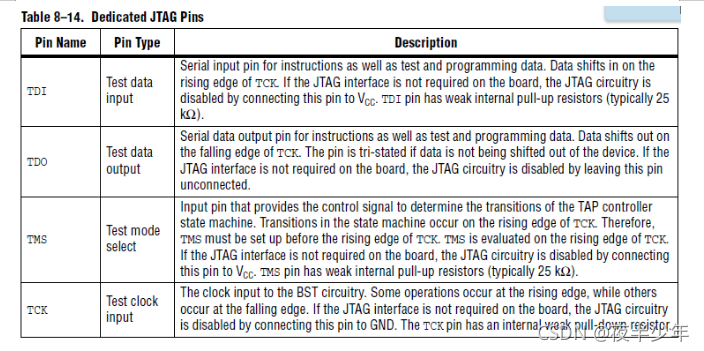

2.5 FPGA EP4CE22F17C8N

手册PAGE 8-46,TDI和TMS 上拉25K电阻,TDO浮空,TCK下拉:

3 总结

上下拉电路一般在IC内部就已经做好,外部可以不加,如果外部添加,要与IC手册中的上下拉特性一致,TCK和TRST引脚有可能会不同,TDI和TMS都是上拉。TDO在IC内部都是浮空,由于TDO都是连接TDI,因此可以加上拉与TDI一致。

| 引脚 | 上下拉特性 | 说明 |

| TMS | 上拉 | |

| TDI | 上拉 | |

| TDO | 浮空或上拉 | |

| TCK | 根据器件资料 | |

| TRST | 根据器件资料,一般上拉 |

1701

1701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?